axi专题

Xilinx FPGA Microblaze AXI_IIC使用方法及心得

Xilinx FPGA Microblaze AXI_IIC使用方法及心得 前言 本着好好学习,认真负责的态度,我计划在空闲时间把自己用到的一些模块的使用方法与心得总结下与大家分享下,技术交流的同时共同进步,如有问题,欢迎批评指正! 本次先着重讲下AXI_IIC核的使用,后续还会包括以下模块 UART_AXI核使用及AXI总线详解QSPI_AXI核的使用AXI_DMA与AXI_FIFO使用,

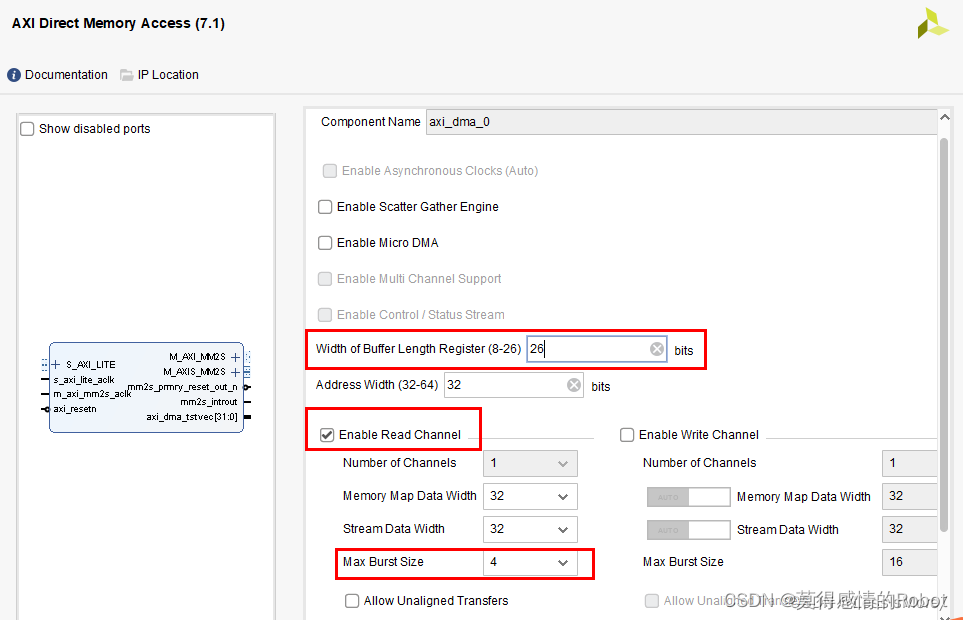

zynq axi-dma 接口参考资料

参考资料: Xilinx官方参考文档:PG021_axi_dma、UG585_zynq_7000_TRM等 AXI DMA开发 http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html 黑金教程 course_s2_ALINX ZYNQ开发平台SDK应用教程V2.02.pdf 米联客教程 S03_CH01_AXI_D

Zynq AXI总线

S02_CH12_ AXI_Lite 总线详解 - 米联客 - 博客园 12.1前言 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密。 12.2 AXI总线与ZYNQ的关系 AXI(Advanced eXtensible Interface)本是由ARM公司提出的一种总线协议,Xilinx从6系列的FPG

AXI三板斧之Outstanding、Out-of-order、interleaving

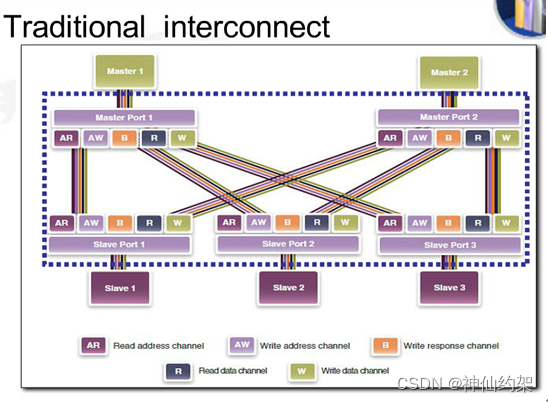

1、AXI三板斧之Outstanding 可以不用等单个命令的响应,直接连续发送N个命令(N>1),假设Slave端的Outstanding能力为N时(N>1),那么Master端可以在Slave不返回读数据的情况下,连续发出N个请求。假如在这期间Slave端返回了m个数据,那么Master端还可以接着发m个请求。形象点说,就是Master端 "在路上" 的请求最多为N个。 下图所示,AXI

【总线】AXI总线:FPGA设计中的通信骨干

目录 AXI4:高性能地址映射通信的基石 AXI4-Lite:轻量级但功能强大的通信接口 AXI4-Stream:高速流数据传输的利器 结语:AXI总线在FPGA设计中的重要性 大家好,欢迎来到今天的总线学习时间!如果你对电子设计、特别是FPGA和SoC设计感兴趣,那你绝对不能错过我们今天的主角——AXI4总线。作为ARM公司AMBA总线家族中的佼佼者,A

博客摘录「 AXI三种接口及DMA DDR XDMA介绍(应用于vivado中的ip调用)」2024年6月10日

关键要点: 1.AXI Stream经过协议转换可使用AXI_FULL(PS与PL间的接口,如GP、HP和ACP)。 2.传输数据类里就涉及一个握手协议,即在主从双方数据通信前,有一个握手的过程。基本内容:数据的传输源会产生“VALID”信号,来指明何时数据有效或控制信息有效。而在目标源一方,会产生“READY”信号,来指明已经准备好接受数据或控制信息。当“VALID”信号和“READY”信号

AXI Quad SPI IP核中的STARTUPEn原语参数

启动STARTUPEn Primitive (原语)参数在 FPGA的主 SPI模式下非常有用。当你启用这个参数时,对于 7 系列设备,STARTUPE2 原语会被包含在设计中;而对于 UltraScale™ 设备,则是 STARTUPE3 原语。这些原语在 FPGA 配置后成为IP核的一部分。 1 启用STARTUPEn 原语参数 STARTUPEn(如STARTUPE2或STARTUP

AXI Quad SPI IP核AXI4-Lite接口的部分操作指南

1 AXI4-Lite接口标准SPI模式——传统模式下可选FIFO的使用 当AXI Quad SPI IP核配置为标准SPI模式时,可以选择在设计中包含16或256深度的可选FIFOs。由于AXI Quad SPI是全双工的,所以发送和接收FIFOs都作为一对被实例化,并且可以包含在IP核中。 当实现FIFO时,要求所有的从选择地址都相同缓冲在FIFO中的数据。这是必要的,因为从机选择地址没有

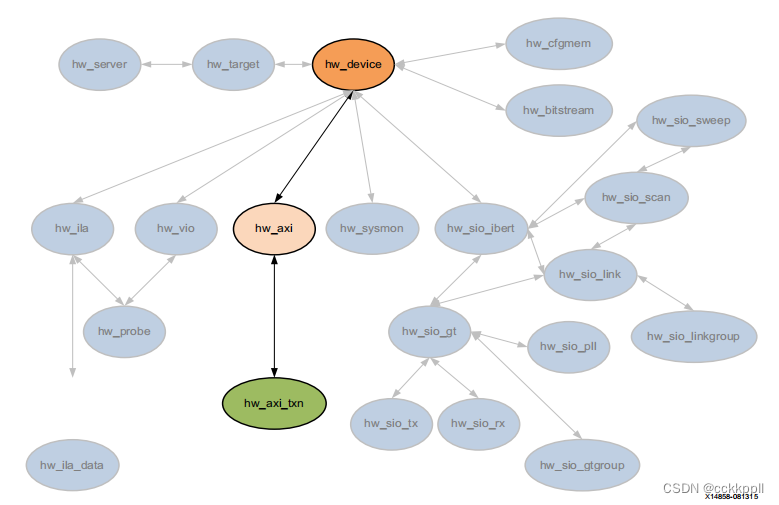

vivado DIAGRAM、HW_AXI

图表 描述 块设计(.bd)是在IP中创建的互连IP核的复杂系统 Vivado设计套件的集成商。Vivado IP集成器可让您创建复杂的 通过实例化和互连Vivado IP目录中的IP进行系统设计。一块 设计是一种分层设计,可以写入磁盘上的文件(.bd),但存储为 Vivado工具内存中的图表对象。 块设计通常是在界面级别构建的,以提高生产力,但是 也可以在端口或引脚级别进行编辑,以提供更大的控制

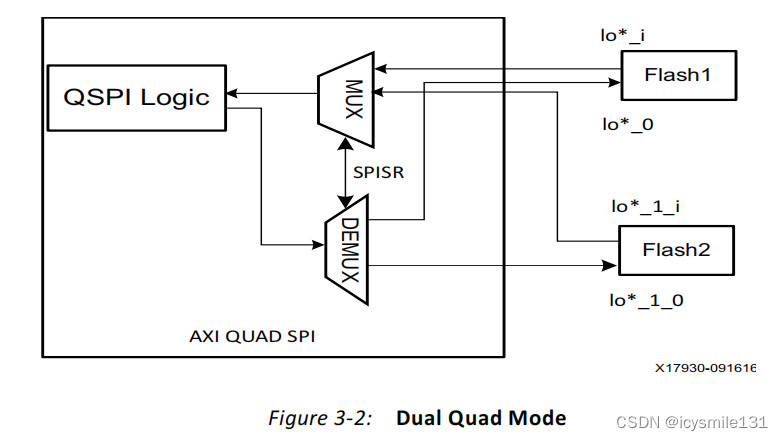

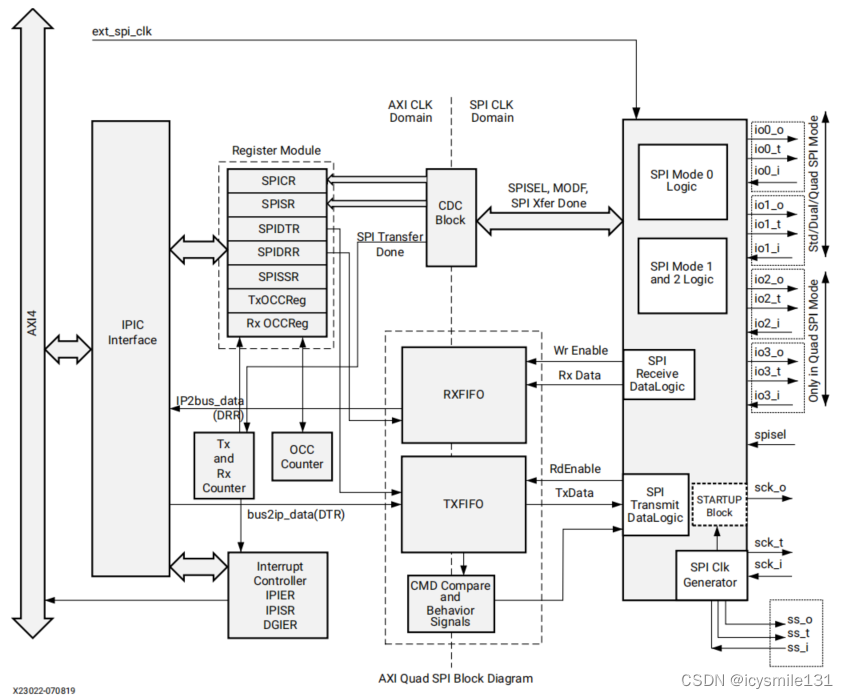

AXI Quad SPI IP核子模块

当选择Enable Performance Mode选项时,AXI Quad SPI IP核向后兼容所有早期版本的AXI Quad SPI IP核。该IP核包括以下子模块: AXI4-Lite 接口模块 AXI4-Lite接口模块为AXI4-Lite协议和IPIC提供接口。AXI4Lite接口上的读写事务被转换为等效的IP 互连(IPIC)事务。这是该IP核的默认组合。 SPI 寄存器模块

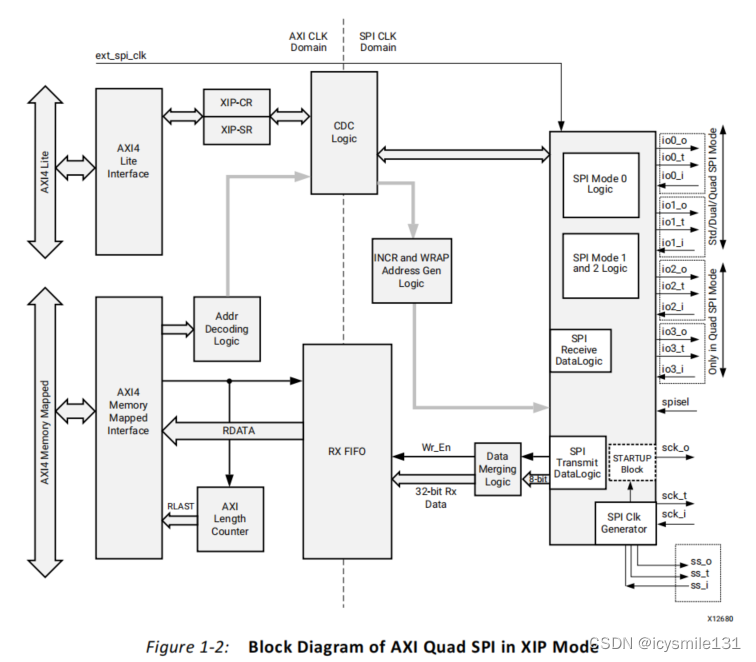

AXI Quad SPI IP核AXI4接口下的三种操作模式

当选择Enable Performance Mode选项时,AXI4接口包括在内。在该模式下,IP核可以在增强模式下操作(未选择启用XIP模式)或XIP模式(选择启用XIP模式)。在性能模式下,AXI4接口用于在DTR和DRR位置的突发事务。 1 增强模式 在这种模式下,原先用于IP核的AXI4-Lite接口被AXI4接口所取代。AXI4接口支持更复杂的数据传输方式,包括突发传输。根据“Mod

Vitis HLS 学习笔记--接口聚合与解聚-AXI主接口

目录 1. 简介 2. 用法及语法 3. 详细解读 4. 总结 1. 简介 在使用 Vitis HLS 工具进行硬件设计时,如果你在接口上使用了结构体,工具会自动把结构体里的所有元素组合成一个整体。就像把一堆零件组装成一个玩具一样。这样做的好处是,数据可以作为一个单元一起处理,而不是分开处理每个元素。 默认情况下,Vitis HLS 会自动做这个组合工作,你不需要特别告诉它去

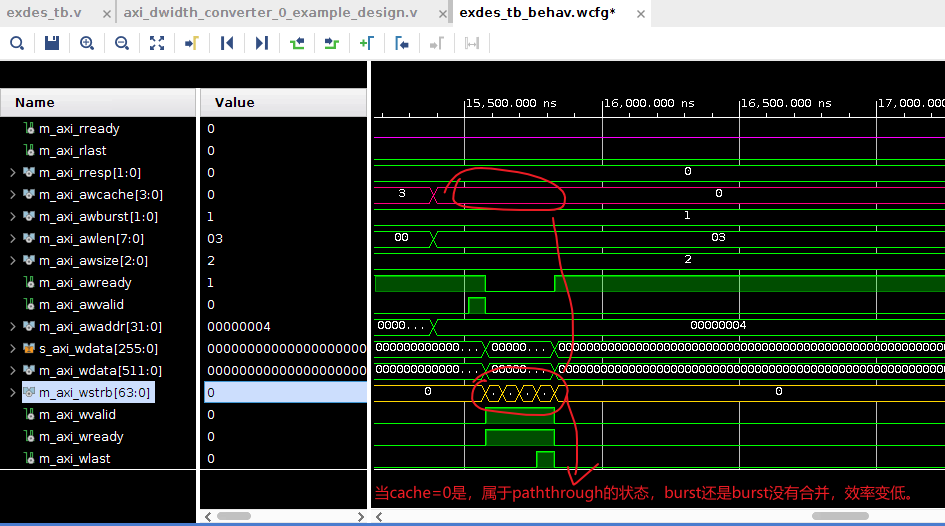

axi width convert

1,axi width convert 比如32数据位宽转512数据位宽, 那么在32位宽端对0,4,8的写操作将变为 在512位宽端对地址0的strb写操作。(strb信号用来指示512bit即64字节在哪些位置的byte是有效的) 逻辑上理解可以无缝转换。 但实际对于4/8等地址的操作是无效的,只能0/64/128/… 32位宽端的busrt操作会被转化为512端的

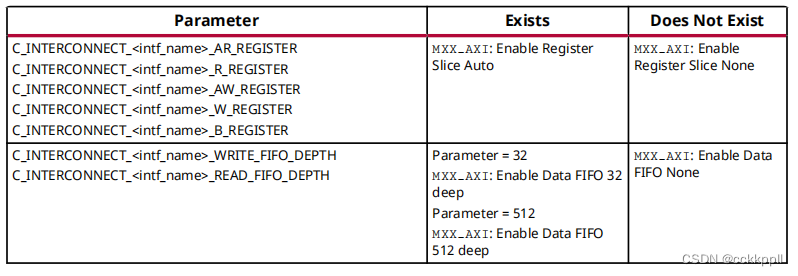

设置AXI主寄存器切片和AXI数据FIFO

设置AXI主寄存器切片和AXI数据FIFO 打开MHS文件,并为每个AXI主机设置启用寄存器切片/启用数据FIFO。到 确定正确的设置,使用下表中的信息搜索MHS。 进行搜索时,将<intf_name>替换为相关的BUS_INTERFACE名称。 例如,BUS_INTERFACE M_AXI_MM2S的<intf_name>为 M_AXI_MM2S,并且BUS_INTERFACE M_AXI_GP

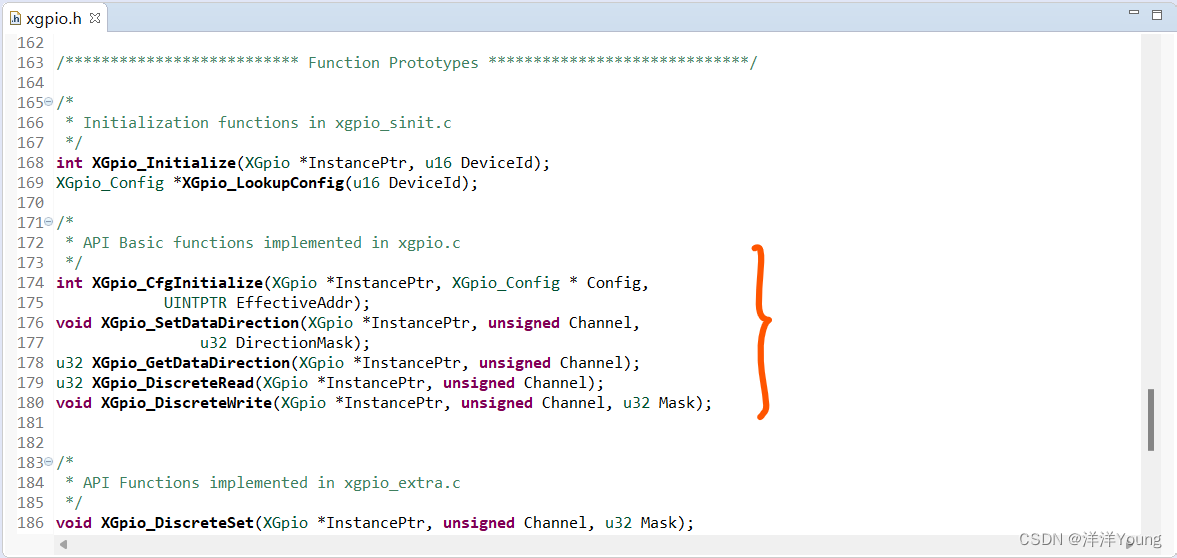

【ZYNQ】GPIO 与 AXI GPIO

在嵌入式开发中,GPIO 是最常见的外设。GPIO 是 General Purpose I/O 的缩写,译为通用输入/输出。GPIO 用于连接外部设备,例如按键、传感器等,实现数字信号的输入或输出功能。本文主要介绍 Zynq GPIO 的基本概念,并对比 GPIO 与 AXI GPIO 的使用方法。 GPIO Zynq GPIO 被称为 MIO,是 Multiplex

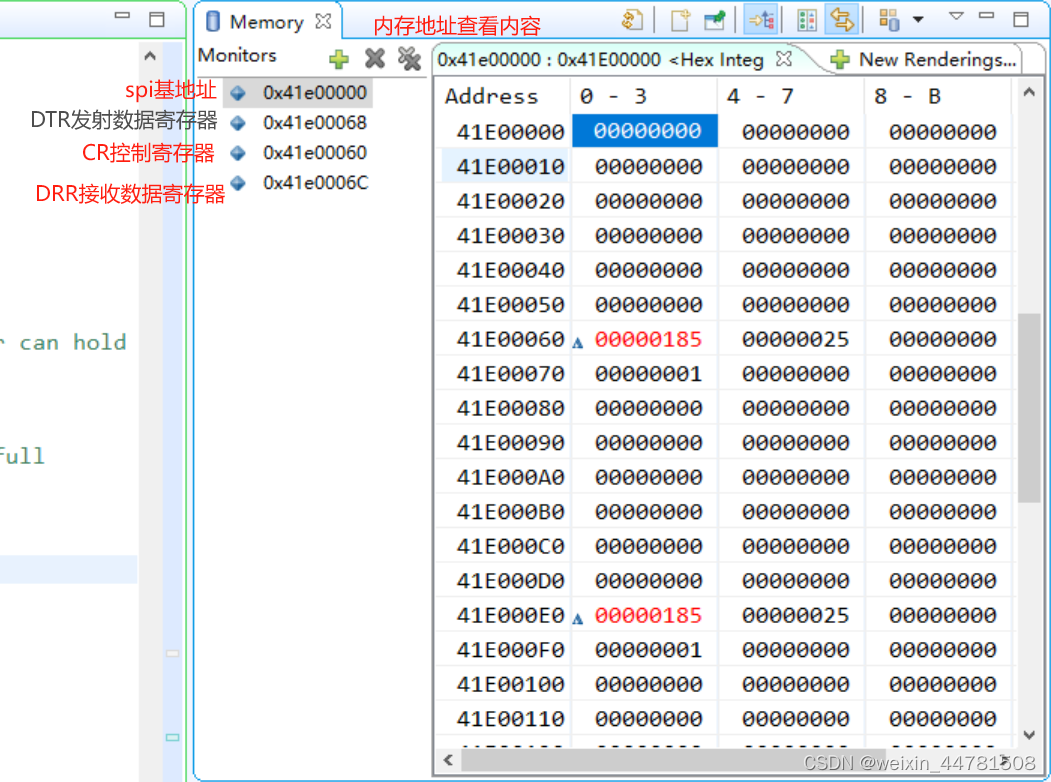

【ZYNQ】AXI-Quad-SPI SDK 开发记录 测试

前人工作 如前人工作,在Navigate to BSP Settings中找到历例程 file:///F:/Xilinx/Vitis/2019.2/data/embeddedsw/XilinxProcessorIPLib/drivers/spi_v4_5/doc/html/api/example.html 使用XSpi_LowLevelExample例子,源代码的AI解析 int

【IC前端虚拟项目】axi ddr/sram验证组件思路与编写

【IC前端虚拟项目】数据搬运指令处理模块前端实现虚拟项目说明-CSDN博客 在完成了所有的utils包括apb_utils之后,就要进行验证环境的整体搭建,因此我们再把验证环境拿出来看一下: 按照由底至顶层的思路,接下主要有五大部分需要我们完成:ram_model、reference_model、env、base_test和harness,这一篇从最难的ram_model开始说起。这

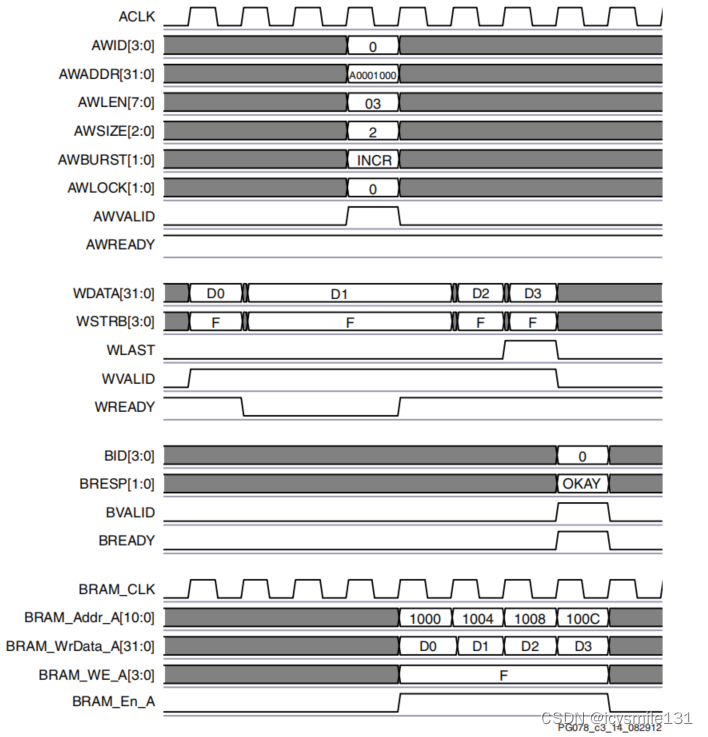

AXI4写时序在AXI Block RAM (BRAM) IP核中的应用

在本文中将展示描述了AXI从设备(slave)AXI BRAM Controller IP核与Xilinx AXI Interconnect之间的写时序关系。 1 Single Write 图1是一个关于32位宽度的BRAM(Block RAM)的单次写入操作的例子。这个例子展示了如何向地址0x1000h的BRAM写入数据,其中C_S_AXI_BASEADDR被设置为0xA000 0000,并

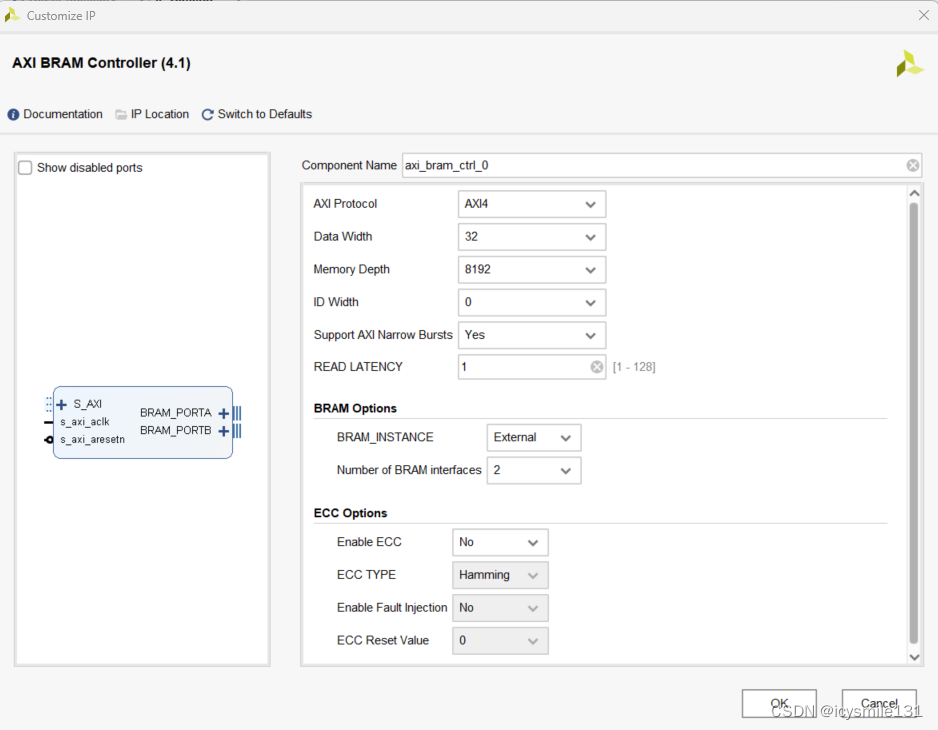

AXI Block RAM 控制器IP核的用法详解

本文描述了如何使用Xilinx的Vivado Design Suite环境中的工具来定制和生成AXI Block RAM (BRAM) IP 核。Vivado Design Suite是一个强大的FPGA设计和开发环境,它允许用户定制和配置各种IP核以适应他们的特定设计需求。 以下是针对如何定制IP核的步骤的简要概述: 1. 从IP Catalog中选择IP。 2. 定制IP核 双击选

Vitis HLS 学习笔记--AXI_STREAM_TO_MASTER

目录 1. 简介 2. 示例 2.1 示例功能介绍 2.2 示例代码 2.3 顶层函数解释 2.4 综合报告(HW Interfaces) 2.5 关于TKEEP和TSTRB 2.6 综合报告(SW I/O Information) 3. 总结 1. 简介 本文通过“<Examples>/Interface/Streaming/axi_stream_to_master

FIFO Generate IP核使用——AXI接口AW Config页配置

AXI FIFO与Native FIFO在First-Word Fall-Through模式下具有相似的功能,但AXI FIFO通常还提供了更多的特性和灵活性。 1 配置选项(Configuration Option) FIFO Generator IP核提供了三种可选的配置选项,包括FIFO、Register Slice(寄存器切片)和Pass Through Wire(直通线)。这些选

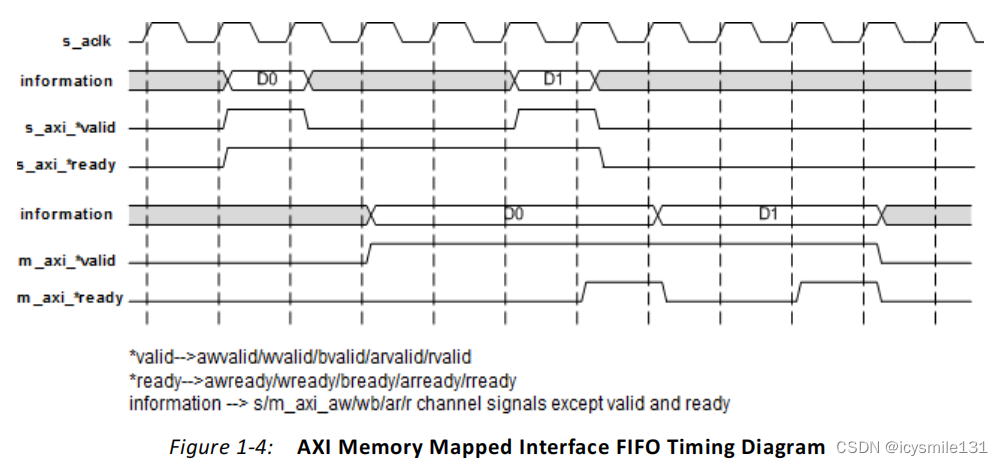

FIFO Generate IP核使用——AXI接口FIFO简介

AXI接口FIFO是从Native接口FIFO派生而来的。AXI内存映射接口提供了三种样式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的应用外,AXI FIFO还可以用于AXI系统总线和点对点高速应用。 AXI接口FIFO不支持Builtin FIFO和 Shift Register FIFO配置。 当需要连接到其他AXI功能时,可以在Native接口FIFO支持

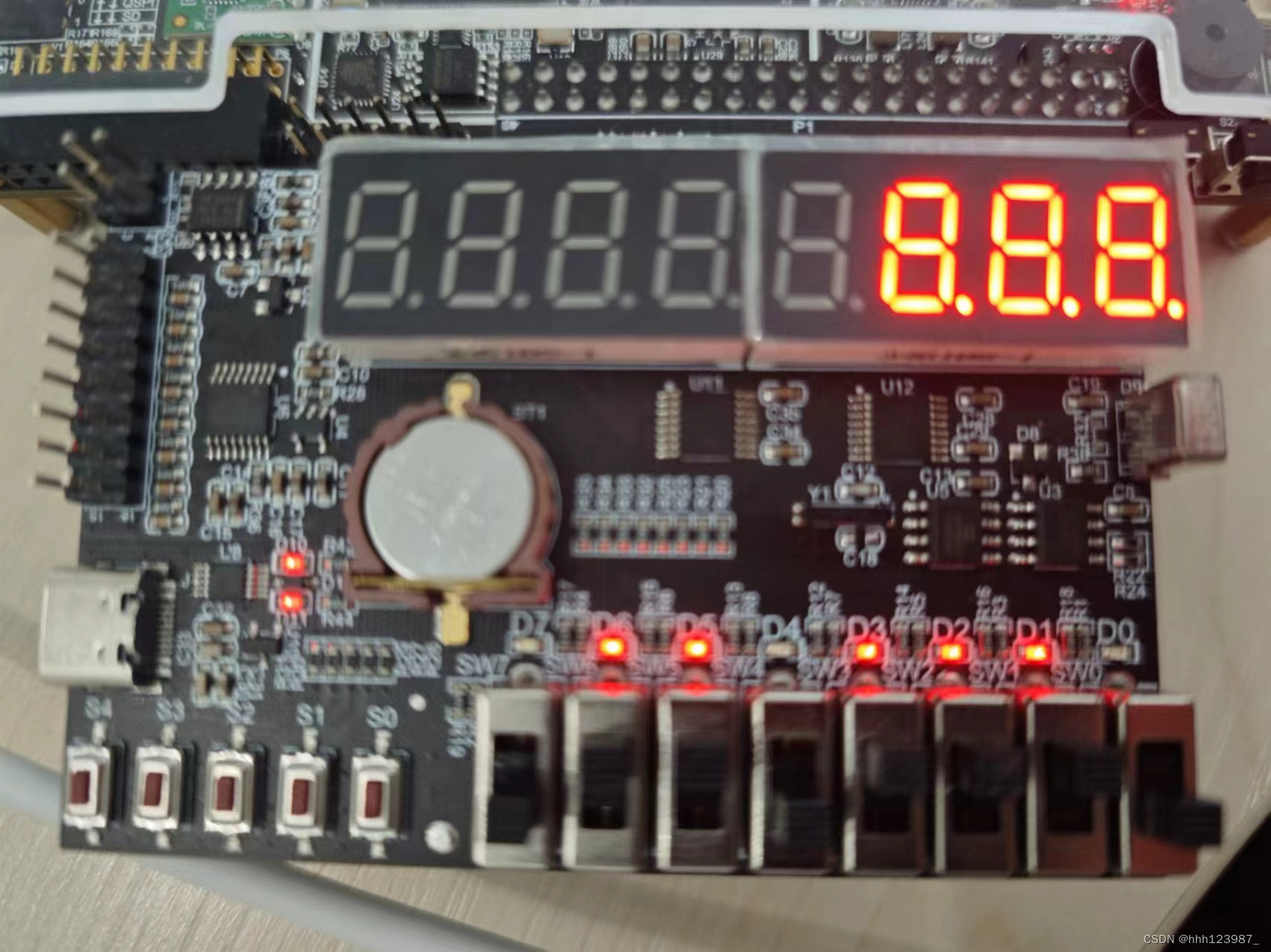

ZYNQ PS + PL异构多核案例开发手册之axi_timer_pwm_demo案例

本文主要介绍ZYNQ PS + PL异构多核案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。 axi_timer_pwm_demo案例 1 案例功能 案例功能:PS端通过AXI4-Lite总线发送命令至PL端AXI Timer IP核,IP核再根据命令通过PWM方式控制评估底板PL端LED5的状

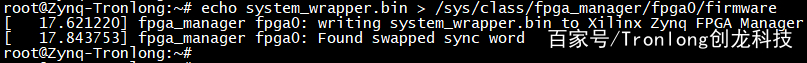

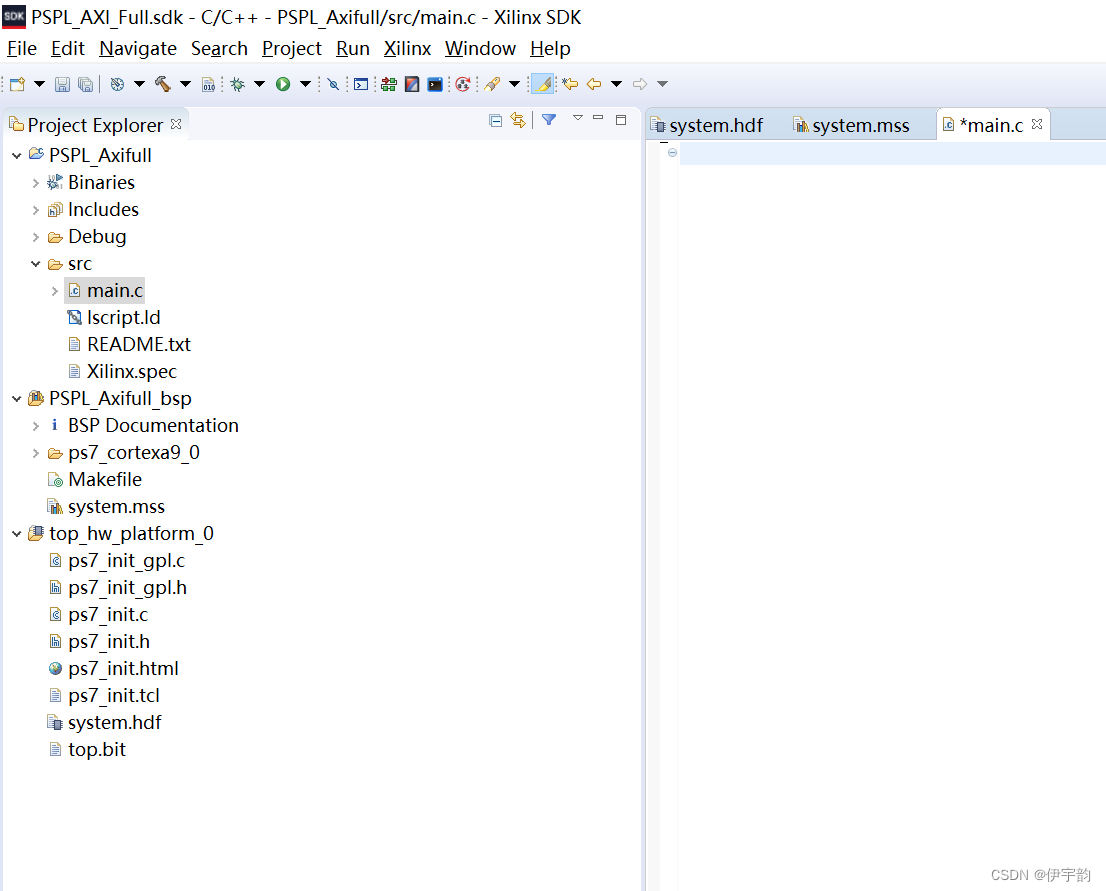

FPGA - 基于自定义AXI FULL总线的PS和PL交互

前言 在FPGA - ZYNQ 基于Axi_Lite的PS和PL交互中,介绍了基于基于AXi_Lite的PL和PS交互,接下来构建基于基于Axi_Lite的PS和PL交互。 AXI_GP、AXI_HP和AXI_ACP接口 首先看一下ZYNQ SoC的系统框图,如下图所示。在图中,箭头方向代表主机到从机的方向。 在上图中红色框线中,就是PS和PL之间的交互,将上图简化如下: 可

Zynq学习笔记--AXI 总线概述

目录 1. AXI总线概述 1.1 主要特点 1.2 通道功能 1.3 信号概览 2. AXI Interconnect 2.1 信号说明 2.2 内部结构 3. PS-PL AXI Interface 3.1 AXI FPD/LFP/ACP 3.2 Address Editor 3.3 地址空间 3.4 AXI-DDR 4. 通过ILA观察AXI信号 4.1 AXI