本文主要是介绍vivado DIAGRAM、HW_AXI,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

图表

描述

块设计(.bd)是在IP中创建的互连IP核的复杂系统

Vivado设计套件的集成商。Vivado IP集成器可让您创建复杂的

通过实例化和互连Vivado IP目录中的IP进行系统设计。一块

设计是一种分层设计,可以写入磁盘上的文件(.bd),但存储为

Vivado工具内存中的图表对象。

块设计通常是在界面级别构建的,以提高生产力,但是

也可以在端口或引脚级别进行编辑,以提供更大的控制。Vivado设计套件

项目可以在设计层次结构的不同级别合并多个图表,也可以

由单个图表组成作为顶层设计。

相关对象

如图1-2第13页所示,图对象包含其他IP积分器块设计

(bd)对象,如bd_cell、bd_nets和bd_ports。这些对象之间的关系

类似于单元、引脚和网络的标准网表对象之间的关系。你

可以得到块设计的每个对象:单元、地址空间、地址段、网络、引脚、端口、,

指定图表对象的接口网、接口引脚和接口端口。

例如,使用以下Tcl命令获取块设计的网络:

get_bd_nets-of_objects[current_bd_design]

属性

下表列出了在Vivado Design中分配给图表对象的属性

Suite,具有示例值:

描述

JTAG到AXI主核心,或hw_AXI对象,是一个可定制的IP核心,用作AXI

Master在Xilinx FPGA上驱动AXI事务和驱动AXI信号,hw_device对象。

AXI Master核心支持AXI4接口和AXI4 Lite协议。AXI数据的宽度

总线是可配置的。AXI内核可以驱动AXI4 Lite或AXI4内存映射从机

通过AXI4互连。核心也可以连接到互连作为

主人

JTAG到AXI主核心必须在Xilinx IP目录的RTL代码中实例化。

关于VIO核心的详细文档可以在LogiCORE IP JTAG到AXI中找到

主产品指南(PG174)[参考文献29]。

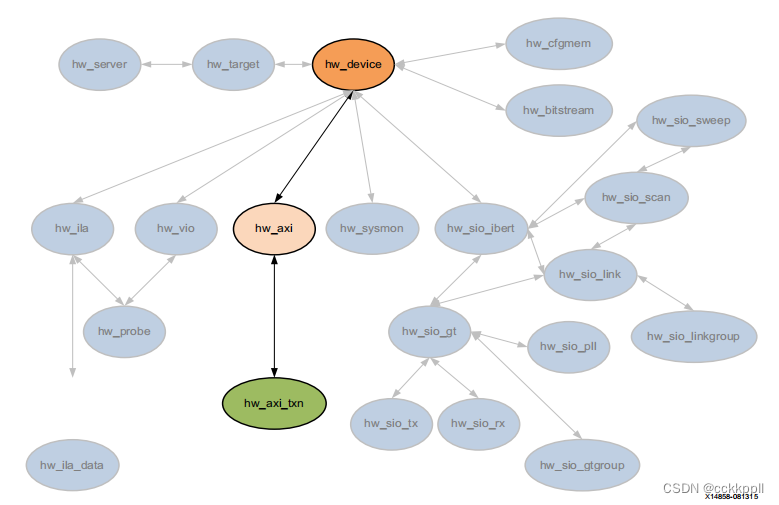

相关对象

目录AXI核心可以在综合网表设计中使用

get_debug_cores命令。这些不是硬件AXI主核心对象hw_AXI,

在Vivado Design Suite的硬件管理器功能中找到,尽管它们是相关的。

HW_AXI核心可以在编程硬件的硬件管理器中找到

设备对象,hw_device。您可以如下查询hw_device的hw_axi:

get_hw_axis-of[get_hw_devices]

此外,HW_AXI核心具有与该核心相关联的AXI事务,该事务可以是

查询如下:

get_hw_axi_txns-of[get_hw_axis]

属性

可以使用report_property命令报告指定给的特性

HW_AXI核心。请参阅Vivado Design Suite Tcl命令参考指南(UG835)

[参考文献13]了解更多信息。分配给HW_AXI对象的属性包括

以下是示例:

这篇关于vivado DIAGRAM、HW_AXI的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!