vivado专题

vivado 添加多循环路径

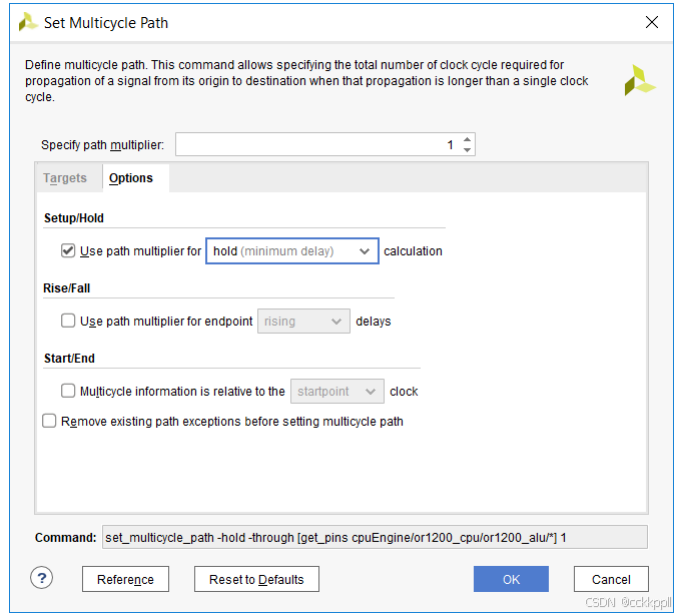

添加多循环路径 接下来,您将使用约束编辑器添加一个多循环路径。 1.双击树的“异常”类别下的“设置多周期路径”。 2.在“设置多周期路径”对话框中,将路径乘数设置为2。 3.在“通过”输入框中,键入以下字符串(或者,您可以复制和粘贴它 从这里): [get_pins cpuEngine/or1200_cpu/or1200_alu/*] 请注意,Tcl命令显示在command字段中。

vivado error:Combinatorial Loop Alert:1 LUT cells form a combinatorial loop

VIVADO ERROR :Combinatorial Loop Alert:1 LUT cells form a combinatorial loop vivao生成bit流时发生报错,如下图所示定位原因解决 vivao生成bit流时发生报错,如下图所示 定位原因 在三段式状态机中,组合逻辑代码if else 语句未写全只写了if…elsif…,没有写else,导致错误

vivado 创建时间约束3

下图显示了完成的输入延迟页面。请注意,四个约束是 跳过。 12.成功输入所有输入约束值后,单击下一步。 向导的“输出延迟”页面显示了中不受约束的所有输出 设计。页面布局与输入页面非常相似。 13.在“输出延迟”页面中,单击“时钟”标题,按时钟的字母顺序对表格进行排序 名字。 14.使用下表约束所有输出,就像您对输入约束值所做的那样。 您可以在向导中一次选择多行,同时编辑多个条目。

vivado 创建时间约束1

步骤3:创建时间约束 在此步骤中,您打开合成的设计并使用AMD Vivado™定时约束 男巫定时约束向导分析门级网表并发现缺失 约束。使用“定时约束”向导为此设计生成约束。 1.在“流导航器”中,单击“打开综合设计”。 2.当综合设计打开时,单击综合设计下的约束向导 部分。 此时会出现“定时约束”向导的介绍页面。本页介绍 向导创建的约束类型:时钟、输入和输出端口以及时钟 域交叉。 3.阅读页面后,

Vivado+PetaLinux 系统搭建教程

PetaLinux 是基于 Yocto project DDR SDRAM 双倍数据率同步动态随机存取存储器(英语:Double Data Rate Synchronous Dynamic Random Access Memory,简称DDR SDRAM)为具有双倍资料传输率的SDRAM,其资料传输速度为系统主频的两倍,由于速度增加,其传输性能优于传统的SDRAM。 FTP文件传输 在ubun

点击Vivado的安装程序exe无法安装的解决办法

在Windows操作系统上,在安装Vivado的时候会遇到双击xsetup.exe没有反应的情况,即使是用管理员权限再加上设置兼容模式也没有任何效果,且此问题有可能在多个版本上都存在,包括最新的2016.02。 打开解压后的Vivado安装包的bin目录下,可以看到xsetup.exe本质上是调用xsetup.bat (个别版本是xsetup2.bat)这个批处理文件。 接下来我们可以尝试用管理员

创建 AD9361 的 vivado 工程,纯FPGA配置,不使用ARM程序

前言 AD9361 的配置程序,如果使用官方的,就必须用ps进行配置,复杂不好使,如果直接使用FPGA配置,将会特别的简单。 配置软件 创建一份完整的寄存器配置表 //************************************************************// AD9361 R2 Auto Generated Initialization Scri

Vivado DDS IP核使用和仿真(二、多通道信号发生器)

按照博文https://blog.csdn.net/u013215852/article/details/91042672了解完单通道信号发生器之后,我们来看一下如果用一个IP核同时生成多通道信号怎么做,本文以1MHz和10MHz双通道为例: 1、设置参数,注意与单通道不同的地方 通道设置为2,那么我们想要得到与单通道一样16bit的输出数据,那么根据公式 我们就需要把Frequen

Vivado DDS IP核使用和仿真(一、单通道信号发生器)小补充

请先看上一篇博文:https://blog.csdn.net/u013215852/article/details/91042672 在此博文的最后,生成了同时输出正弦信号和余弦信号,一些读者对此有一些疑问,其实很简单,按照上一篇的设置,如果把output设置为Sine and Cosine,那么IP核会自动将输出的宽度扩大一倍,即16变成了32,根据下图可知高16位为SINE,低16位为COS

ubuntu,vivado HLS C simulation启动失败

在ubuntu18.04环境下安装了vivado2018.3版本,运行C simulation时失败,原因是缺少组件,解决办法: sudo apt-get install tofrodos gawk xvfb git libncurses5-dev tftpd zlib1g-dev zlib1g-dev:i386 libssl-dev flex bison chrpath socat autoc

ADI HDL 和 Vivado版本对应

ADI HDL 和 Vivado版本对应 ADI HdlVivadoQuartushdl_2014_r12013.414.0hdl_2014_r22014.214.0hdl_2015_r12014.4.115.0hdl_2015_r22015.2.115.1hdl_2016_r12015.4.215.1hdl_2016_r22016.216.0hdl_2017_r12016.416.1hdl_2

microsoft微软excel或WPS表格打开vivado逻辑分析仪ILA保存的csv文件,自动转换科学计数法损失精度的bug

问题 vivado的逻辑分析仪ILA,可以方便的把数据导出成CSV(Comma-Separated Values)文件,实际是逗号作为分隔符的数据文件。 导出数据文件用文本编辑器打开,第74行有如下数据: 但是使用excel打开这个csv文件,则这个数据自动显示为科学计数法,但是值的最后一位已经从8变成0: 误差 这个值代表的双精度浮点数,误差-0.00000000000005

AD9162数据链路lanes与FPGA高速BANK引脚交叉相连导致vivado编译失败

问题概述 对AD9162芯片进行功能开发时,发现AD9162的链路lanes与FPGA的高速BANK引脚存在交叉相连的情况,按照实际的引脚连接关系进行约束后,vivado编译失败。 问题阐述及原因分析 问题详情阐述 板卡对AD9162芯片进行功能开发时,发现硬件电路的设计结果存在AD9162数据链路与FPGA高速BANK引脚交叉相连的问题,示意图如图3‑1,若根据图示的引脚连接关系进行

VIVADO自定义 IP封装

简介 本章节主要针对VIVAO 2020.2版本做IP自定义封装,其中涉及到IP寄存器读写配置,自定义接口封装等介绍。 IP封装 IP标准自定义步骤一般有创建工程,封装IP,自定义内容,添加自定义库这4个步骤,下面就每个步骤详细介绍。 创建工程 以寄存器读写IP为例子,自定义封装一个IP模块,首先创建工程,如下图所示:

vivado SLEW

SLEW为配置了I/O标准的输出缓冲区指定了输出缓冲区转换速率 支持可编程输出转换速率。 架构支持 所有架构。 适用对象 •端口(get_Ports) °连接输出或双向端口 •单元(get_cell) °输出缓冲器(所有OBUF变体) 价值观 •慢速(默认) •中等:适用于UltraScale体系结构,仅适用于高性能(HP)I/O。 •快速 Syntax Verilog Syntax

vivado RPM

RPM属性是分配给定义集的逻辑元素的只读属性 通过RTL源文件中的H_SET、HU_SET或U_SET属性。 当RTL源文件中也存在RLOC时,H_SET、HU_SET和U_SET属性 转换为合成网表中单元格的只读RPM属性。HU_SET 在Vivado Design的文本编辑器中的RTL源文件上可以看到U_SET属性 一套。但是,在单元格对象的“属性”窗口中,会显示RPM属性。For 有关使用这

vivado 调用 vscode 编辑器

打开 vivado,找到 Setting - Text Editor - Custom Editor - … 在 Editor 框中输入(确保 vscode 在环境变量中,如果没有请使用绝对路径) 对于 Windows code.cmd -g [file name]:[line number] 如果是预览版 vscode,请输入 code-insiders.cmd -g [file na

vivado RLOC

相对位置(RLOC)约束定义了逻辑元素的相对位置 分配给一个集合,如H_set、HU_set或U_set。 当RTL源文件中存在RLOC时,H_SET、HU_SET或U_SET属性将得到 转换为合成网表中单元的只读RPM属性。RLOC 属性被保留,但在合成后成为只读属性。了解更多 有关使用这些属性和定义RPM的信息,请参阅Vivado设计套件 用户指南:使用约束(UG903)[参考文献19]。 提

[vivado][IP核]DDS

刘东华的IP核详解: 1、 这里的是指IP核配置中的相位数据的宽度。 2、 实际使用此IP核时并没有“频率分辨率”可以配,是靠改变来变的。 3、 4、 5、 数据输出的ready在数据正式输出时才会有。 自己仿真: 使用SIN/COS LUT only的模式,使用一个累加器作为相位输入,不知怎么,输出为X。

[vivado]translate_off\on

答疑帖: 1)https://forums.xilinx.com/t5/Synthesis/Question-about-synthesis-translate-on-and-translate-off/td-p/658790

[ip核][vivado]aurora

Xapp1193: discovered:1)并不是所有芯片都支持aurora.xc7z010就没有。 2)XDC文件的指令-允许未约束的引脚的存在: set_property BITSTREAM.General.UnconstrainedPins {Allow} [current_design] PG046

[ip核][vivado]FIFO 学习

<xlinx FPGA应用进阶 通用IP核详解和设计开发>读书摘录: 1. 2.3.仿真模型 特点总结:1)复位后会有busy状态,需要等待wr_rst_busy信号低电平后才能正常写入 2)prog_full信号的高电平长度可调 3)仿真中的读状态很奇怪,并没有正常读取,都是XXX的状态。 所用的te

![[vivado][IP核]FFT](https://img-blog.csdn.net/20180705090837930?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[vivado][IP核]DDS](https://img-blog.csdn.net/20180705083319195?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[ip核][vivado]aurora](https://img-blog.csdn.net/20180626151312133?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[ip核][vivado]Block Menory Gennerator 学习](https://img-blog.csdn.net/20180624220549393?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)

![[ip核][vivado]FIFO 学习](https://img-blog.csdn.net/2018062400334231?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)