本文主要是介绍AXI Block RAM 控制器IP核的用法详解,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

本文描述了如何使用Xilinx的Vivado Design Suite环境中的工具来定制和生成AXI Block RAM (BRAM) IP 核。Vivado Design Suite是一个强大的FPGA设计和开发环境,它允许用户定制和配置各种IP核以适应他们的特定设计需求。

以下是针对如何定制IP核的步骤的简要概述:

1. 从IP Catalog中选择IP。

2. 定制IP核

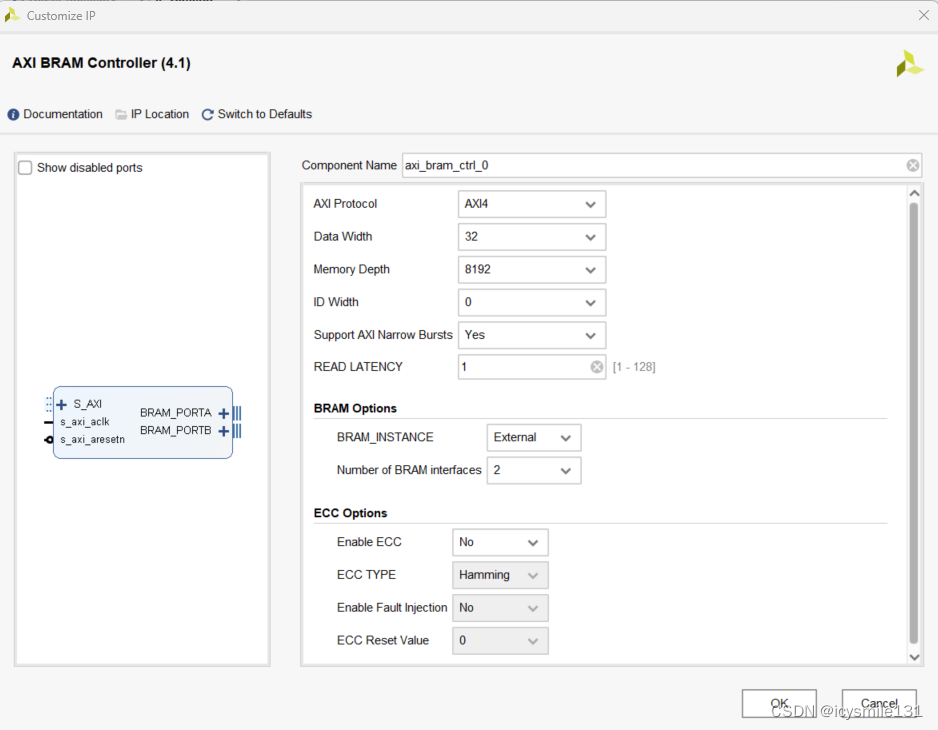

双击选择的IP核,或者从工具栏或右键菜单中选择“Customize IP”命令,打开IP核,开始设置与IP核相关的各种参数值。

在Xilinx的Vivado Design Suite中,AXI BRAM(Block RAM)Controller的参数通常被分为几个类别,以便用户根据设计需求进行定制。

一、General Protocol options(通用协议选项)

具体内容和功能:

- 这些选项通常涵盖了AXI BRAM Controller的基本协议和通信设置。

- 可能包括设置AXI接口的版本(如AXI4、AXI3等)、数据流方向(如读/写)、数据宽度、地址宽度等。

- 通用协议选项还可能包括一些控制信号的配置,如复位信号、时钟信号等。

具体设置为:

(1)AXI Protocol

定义了AXI接口的连接类型。AXI协议有几种不同的版本,包括AXI4、AXI3和AXI4-Lite。这些版本提供了不同程度的复杂性和性能。AXI4是最新且功能最丰富的版本,而AXI4-Lite则是一个简化版本,通常用于那些不需要高性能或复杂性的场合。

(2)Data Width

指定了AXI从设备(即BRAM)的数据宽度。数据宽度可以是32、64、128、256、512或1024位。最大的数据宽度支持为1024位。这个值定义了每次数据传输可以处理的位数。

(3)Memory Depth

定义了AXI从设备的内存深度,即可以存储的字(words)数量。支持的内存深度有1k、2k、4k、8k、16k、32k、64k、128k或256k个字。最大的内存深度支持为128K个单词。这个值决定了可以存储在BRAM中的数据量。

注意:

- 当使用IP Integrator时,此参数的值在设计验证过程中会自动从主设备传播过来。这意味着,如果您在系统中连接了一个具有特定数据宽度和内存深度的主设备,AXI BRAM Controller的这些参数可能会自动调整以匹配主设备的设置。

- BRAM接口的地址宽度是基于数据宽度和内存深度自动计算的。如果BRAM的地址宽度与AXI接口的地址宽度不同,BRAM接口的地址宽度将连接到BRAM地址的低位。

- 在IP Integrator中,AXI BRAM Controller支持特定的内存宽度和深度值。这确保了与其他AXI设备的兼容性和高效的数据传输。

AXI BRAM Controller在连接到Block Memory Generator IP核时,支持的内存宽度和内存深度值具体取决于其设计和配置。但一般来说,AXI BRAM Controller支持的内存最大为2mbytes(字节大小为8或9)。同时,AXI BRAM Controller IP支持的最小深度为512字节,任何小于512的深度都会被自动调整为512字节。

(4)ID Width

是ID向量在AXI系统中(包括所有主设备和从设备)的宽度,支持的ID宽度范围是0到32位。

在使用IP integrator时,此参数的值在设计验证期间会自动从主设备传播过来。

(5)Support AXI Narrow Bursts

支持AXI4窄写或窄读操作。

在使用IP integrator时,可以设置此参数的值或将其设置为自动,在这种情况下,值将从主设备传播过来。

(6)Read Latency

BRAM或内存接口上的读延迟。AXI BRAM Controller支持可配置的读延迟选项,以支持BRAM流水线阶段。支持的值是1到128,默认值是1。

在使用IP integrator且BRAM实例参数设置为External时,读延迟的值将传播到从设备IP的BRAM接口。

(7)Read Command Optimization

读命令优化。减少AXI BRAM Controller在读取路径上的处理延迟。支持的值是“否”和“是”,默认值是“否”。

注意:当读延迟大于1时,不支持读命令优化。

二、BRAM options(BRAM选项)

具体内容和功能:

- BRAM选项主要关注BRAM(Block RAM)的配置和控制。

- 可能包括设置BRAM的类型(如单端口RAM、真双端口RAM、ROM等)、存储深度、数据宽度等。

- 在某些情况下,还可以配置BRAM的访问延迟、刷新模式等参数。

指定BRAM是否内部可用(与AXI BRAM Controller IP一起)或外部可用。

在使用IP integrator时,BRAM实例参数的值被设置为External。Number of BRAM Interfaces可以设置为单端口(1)或双端口(2)BRAM接口。

三、ECC Options(ECC选项)

具体内容和功能:

- ECC选项与错误纠正码(Error Correction Code)相关,用于提高数据传输和存储的可靠性。

- 可能包括启用/禁用ECC检查、设置ECC算法的类型、配置ECC的校验位数等。

- 在某些情况下,还可以设置ECC的阈值,以控制何时触发错误纠正操作。

具体设置为:

● Enable ECC: 启用或禁用ECC检查。

● ECC Type: 选择要使用的ECC算法:Hamming(默认)或HSIAO。此选项仅在启用ECC时可用。

● Enable Fault Injection: 指定是否注入故障。当此选项为“是”时,可以在数据以及写入块RAM的生成的ECC中注入错误。此选项仅在启用ECC时可用。

● ECC Reset Value: 确定ECC启用/禁用设置的复位值。在复位期间使用该选项可以启用或禁用ECC检查,但之后可以通过软件命令来控制它。只有当设置为Yes时该选项才可用。

这篇关于AXI Block RAM 控制器IP核的用法详解的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!