ram专题

新型 RAMBO 侧信道攻击通过 RAM 无线电波泄露数据

内盖夫本·古里安大学的研究人员发现了一种从隔离系统中泄露敏感数据的方法。 引入了一种称为 RAMBO(基于 RAM 的电磁隐蔽通道)的新型攻击技术。 该攻击利用计算机 RAM 产生的电磁辐射,使攻击者能够窃取加密密钥、密码、生物特征数据和文件等信息。 即使在系统与外部网络物理隔离的环境中,这种攻击也能实现。 信息泄露速度达 7.5 kB/分钟 该研究由 Morde

[IMX9]Suspend to RAM

由于系统中的所有设备都进入了低功耗状态,因此这种状态可以大大节省功耗,但内存除外,因为内存会进入自刷新模式以保留其内容。 Suspend to RAM 要挂起至 RAM,请执行以下命令: pm-suspend Wake up 从挂起状态唤醒的方法有很多种,举几个例子: - 按下 ON/OFF 按钮(如果电路板上有该按钮) - 按下电路板上的按钮,该按钮的设备树节点(gpio_keys

怎么检测电脑的RAM?丨什么是RAM?

RAM 是 Random Access Memory 的缩写,它是一个允许计算机短期存储数据以更快访问的组件。众所周知,操作系统、应用程序和各种个人文件都存储在硬盘驱动器中。 当 CPU 需要调用硬盘上的数据进行计算和运行时,CPU 会将数据传输到 RAM 中进行计算。然后,计算完成后,CPU 会将结果传回硬盘进行保存。 为什么 CPU 不直接在硬盘上计算?可能会问这个问题。原因是硬盘驱动

FPGA上板项目(三)——RAM测试

目录 实验内容实验原理实验步骤实验用时序波形HDL 代码仿真综合实现上板测试 实验内容 对 FPGA 内部的 RAM 进行数据读写操作。 实验原理 RAM (Random Access Memory),是可以进行数据交换的存储器,可读可写;而 ROM(Read-Only Memory)为只读存储器,只可读取不可写入。 实验步骤 添加 Block Memory Gene

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR*(一篇文章就懂)

内存之RAM、SRAM、DRAM、ROM、FLASH、SDRAM、DDR* 内存 内存(Memory)指的是内存存储器,又称为主存,是CPU用来直接寻址和存储的空间,它相当于一座桥梁,用以负责诸如硬盘、主板、显卡等硬件上的数据与处理器之间数据交换处理,我们可以把内存看作数据缓存区,一个高速的缓存区。内存之所以称为内存,是相对于硬盘这些外存而言,我们要用的软件数据都安装存放在外存上,但是当我

【数字ic自整资料】存储器及不同端口RAM对比

参考资料 【FPGA】zynq 单端口RAM 双端口RAM 读写冲突 写写冲突_双口ram-CSDN博客 华为海思数字芯片设计笔试第五套_10、下列不属于动志数组内建函数的是: a lengtho b. new c. delete() d-CSDN博客 目录 1、计算器典型存储体系结构 2、三种不同端口RAM (1)单端口RAM(Single-port RAM) (2)伪双端口R

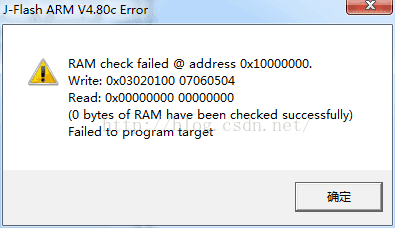

RAM check failed @ address 0x10000000.

用J-Flash RAM软件烧录出现如下错误: 或者: RAM check failed @address 0x20000000. Write: 0x03020100 07060504 Read : 0xAAAAAAAA AAAAAAAA (0 bytes of RAM have been checked successfully) Failed to eras

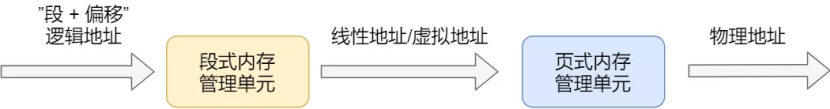

段,页,段页,三种内存(RAM)管理机制分析

段,页,段页 是为实现虚拟内存而产生的技术。直接使用物理内存弊端:地址空间不隔离,内存使用效率低。 段 段:就是按照二进制文件的格式,在内存给进程分段(包括堆栈、数据段、代码段)。通过段寄存器中的段表来进行虚拟地址和物理地址的转换。 段实现的虚拟地址 = 段号+offset 物理地址:被分为很多个有编号的段,每个进程的虚拟地址都有段号,这样可以实现虚实地址之间的转换。其实所谓的地

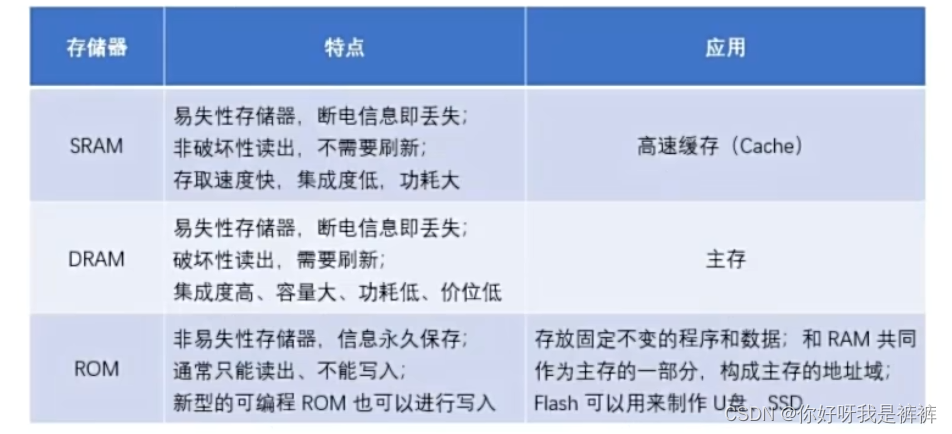

ROM以及ROM与RAM对比

1.ROM ROM最原始的定义是“只读存储器”,一旦写入原始信息则不能更改。所以ROM通常用来存放固定不变的程序、常数和汉字字库,甚至用于操作系统的固化。它与随机存储器可共同作为主存的一部分,统一构成主存的地址域。 现在已经发展出了很多ROM,让用户拥有了修改数据的能力。 固定掩模型ROM(MROM)一次可改写ROM(PROM)紫外线擦除电可编程ROM(EPROM)电擦除电可编程ROM(EE

Jlink下载固件到RAM区

Jlink下载固件到RAM区 准备批处理搜索exe批处理调用jlink批处理准备jlink脚本 调用执行 环境:J-Flash V7.96g 平台:arm cortex-m3 准备批处理 搜索exe批处理 find_file.bat @echo off:: 自动识别脚本名和路径set "SCRIPT_DIR=%~dp0"set "SCRIPT_NAME=%~nx0

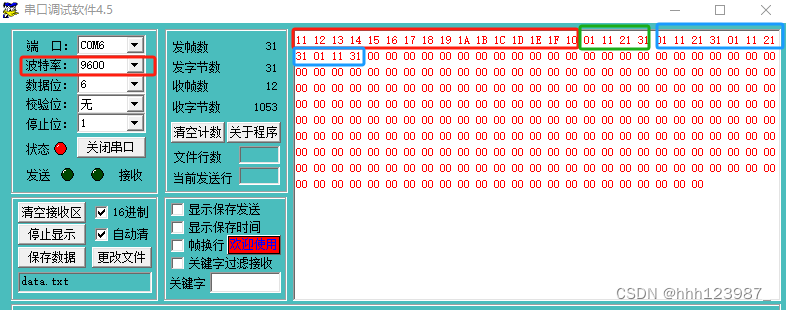

RAM + 串口的简单应用

REVIEW 之前已经学习过: RAM: RAM IP核配置_ip核 ram配置-CSDN博客 串口接收:Vivado 串口接收优化-CSDN博客 串口发送:Vivado 串口通信(UART)------串口发送_vivado串口收发实验-CSDN博客 按键:基于状态机的按键消抖实现-CSDN博客 按键+串口发送实验_串口发按键值-CSDN博客 1. 今日摸鱼任务 小梅哥教材:02_

RAM、ROM、flash、eMMC(通俗易懂)

RAM:Random-Access Memory的缩写,意思为“随机存取存储器” ROM:Read-Only Memory的缩写,意思为“只读存储器” RAM: 临时性:RAM存储的数据在断电时会丢失,因此称为易失性存储器。 可读写:RAM可以被快速读取和写入,它的存储单元可以根据需要来读取和修改数据。 容量和速度:RAM的容量可以从几兆字节(MB)到数百GB不等,速度非常快,可以通过高

如何解决安卓系统吃内存、侵占ram的问题?

我发现安卓吃内存的问题确实存在。有图为证。 搞过 android 底层的应该都懂得那部分内存是哪来的。是的,那部分是 Linux 程序占用的内存,包含内核,驱动,C 应用程序框架,C++ API 等等所有不属于 Java 程序的进程。要想看到这些进程,shell 进去 ps 一下就好了。想 kill 的可以 kill ,因为这都是 Linux。 从某种程度上说,你可以把 an

单片机上FLASH、EEPROM、RAM区别

FLASH主要是程序存储器,在运行过程中不能改,使用的时候我们是把所编写的程序烧录到flash中去,RAM主要做运行时数据存储器, EEPROM是用来保存掉电后用户不希望丢的数据,运行过程中可以改变,可以理解为数据存储器。比如一个时钟闹铃初始化设定为15:00,后来在运行中改为8:00,这是保存在EEPROM里,不怕掉电。 以下是详细介绍: FLASH的全称是FLASH EEPROM,

【FPGA项目】bin文件ram存取回环测试

🎉欢迎来到FPGA专栏~bin文件ram存取回环测试 ☆* o(≧▽≦)o *☆嗨~我是小夏与酒🍹 ✨博客主页:小夏与酒的博客 🎈该系列文章专栏:FPGA学习之旅 文章作者技术和水平有限,如果文中出现错误,希望大家能指正🙏📜 欢迎大家关注! ❤️ 🎉 目录-bin文件ram存取回环测试 一、效果演示🥝演示视频🥝结果分析 二、说明三、bin文件的生成🔸bin

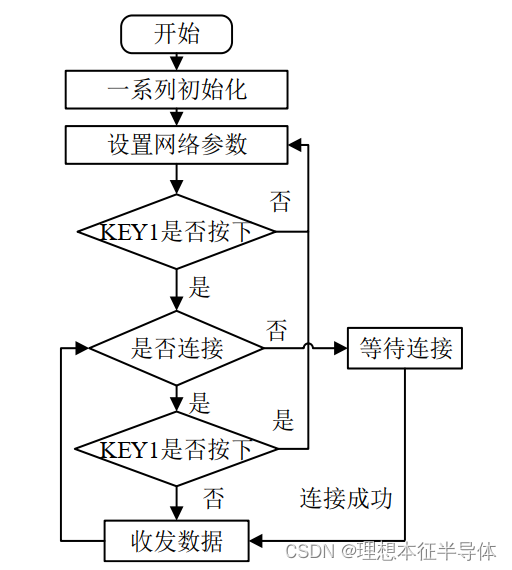

STM32F4_HAL_LWIP_RAM接口UDP实验

目录 RAW 的 UDP 接口简介 RAW 的 UDP 实验 硬件设计 例程功能 软件设计 UDP 配置步骤 软件设计流程图 RAW 的 UDP 接口简介 UDP 协议的 RAW 的 API 功能函数,我们使用这些函数来完成 UDP 的数据发送和接收功能。 (1) udp_new 函数 此函数用来创建一个 UDP 控制块,这个控制块用来描述 IP

Insufficient RAM for Flash Algorithms出错原因及解决方案

“Insufficient RAM for Flash Algorithms”错误一般会有一个“cannot load flash programming algorithm !”的提示窗口,如下图: “Insufficient RAM for Flash Algorithms”从字面上解释是:“装载FLASH算法的RAM空间不足”。 这个错误一般出现在添加了新的FLASH

keil程序在外部RAM中调试的问题总结(个人的一点经验总结)

keil程序在内部RAM调试的基本步骤网上已经有很多了,我就不再赘述,大家可以在网上搜到很多。 但是有些时候内部RAM并不够用,这就需要将程序装入外部RAM中调试,而在这个过程中可能会出现各种各样的问题,在这里我将会把我遇到过的一些问题和需要注意的地方总结一下,希望能够对大家有所帮助。 有错误的地方也希望大神们能够不吝赐教,提前表示感谢··· 转载请注明出处:waitig'

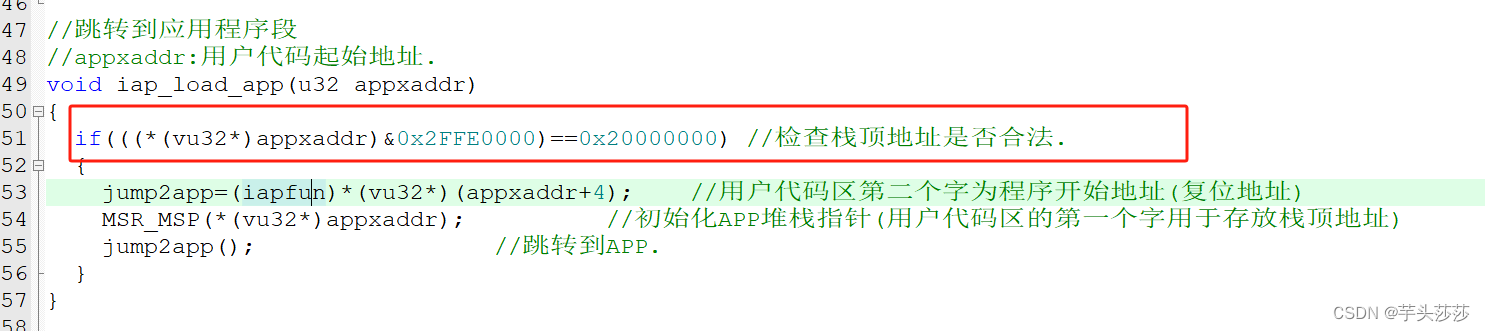

BOOT程序与APP程序的RAM共享问题与栈顶地址判断合法

一、我们在进行BOOT程序和APP程序,会想到这里面的RAM他们之间是怎么分配的,会不会有冲突? 答案是:从BOOT程序跳转到APP程序后,相当于执行了新的程序,所以BOOT里边的内存是全部释放了。所以是相互不影响的 二、在BOOT程序跳转时候,这个栈顶地址顶栈合法是怎么判断编写的 ((*(__IO uint32_t*)appxaddr)&0x2FFE0000)==0x20000000/

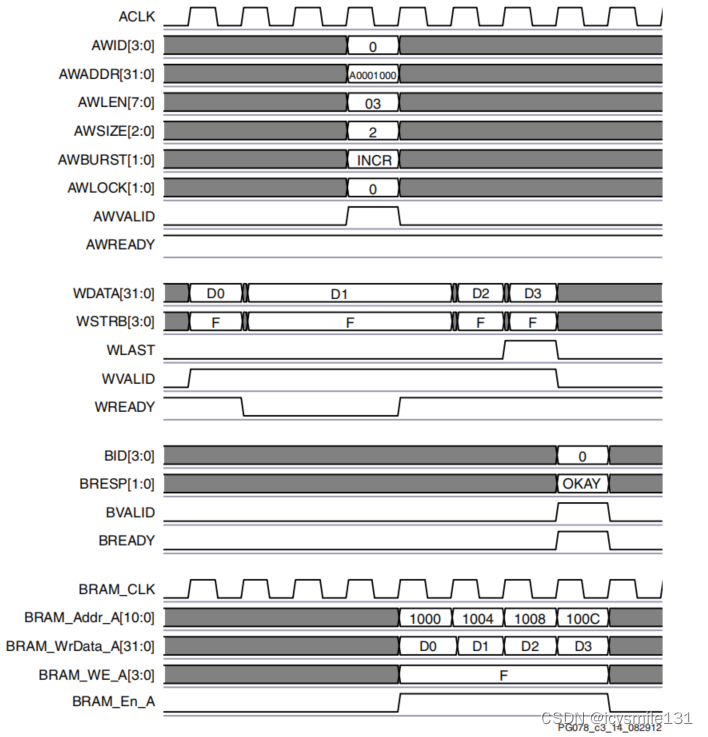

AXI4写时序在AXI Block RAM (BRAM) IP核中的应用

在本文中将展示描述了AXI从设备(slave)AXI BRAM Controller IP核与Xilinx AXI Interconnect之间的写时序关系。 1 Single Write 图1是一个关于32位宽度的BRAM(Block RAM)的单次写入操作的例子。这个例子展示了如何向地址0x1000h的BRAM写入数据,其中C_S_AXI_BASEADDR被设置为0xA000 0000,并

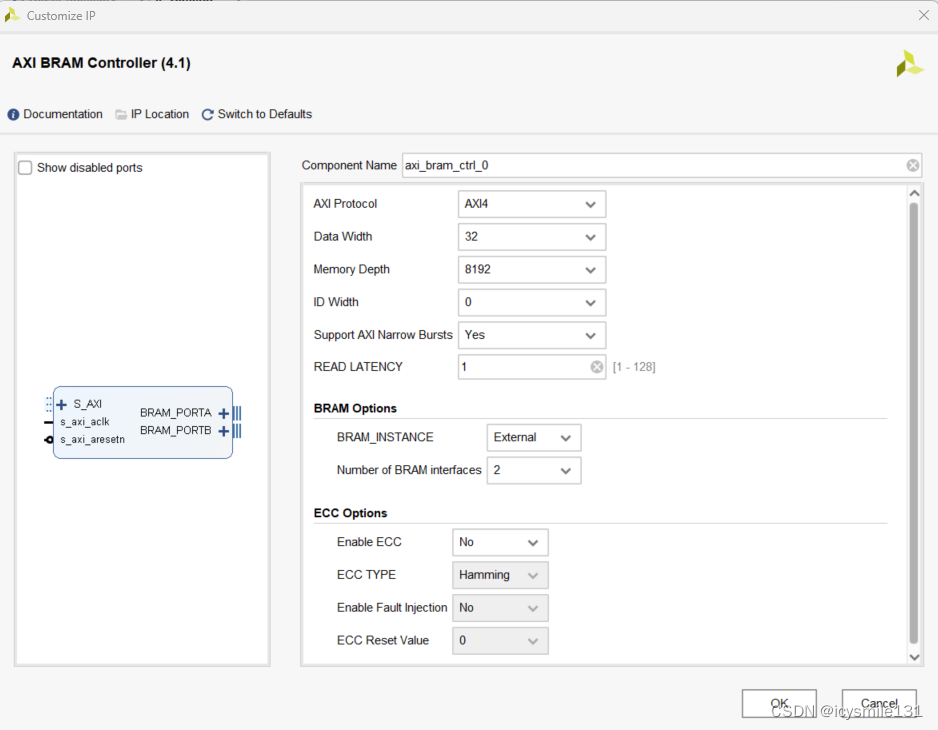

AXI Block RAM 控制器IP核的用法详解

本文描述了如何使用Xilinx的Vivado Design Suite环境中的工具来定制和生成AXI Block RAM (BRAM) IP 核。Vivado Design Suite是一个强大的FPGA设计和开发环境,它允许用户定制和配置各种IP核以适应他们的特定设计需求。 以下是针对如何定制IP核的步骤的简要概述: 1. 从IP Catalog中选择IP。 2. 定制IP核 双击选

存储器简介(RAM/ROM/FLASH/NVRAM)

memory 内存 RAM(Random Access Memory)随机存储器。掉电后数据会消失 SRAM((Static RAM)写入的数据不会消失,直到下次写入或掉电。常用于CPU的一级缓存、二级缓存。价格昂贵。DRAM(Dynamic RAM)写入的数据不能长期保持,必须在一定时间内进行刷新才能保持。常用作内存。价格低于SRAM SDRAM(Synchronous DRAM,同步动

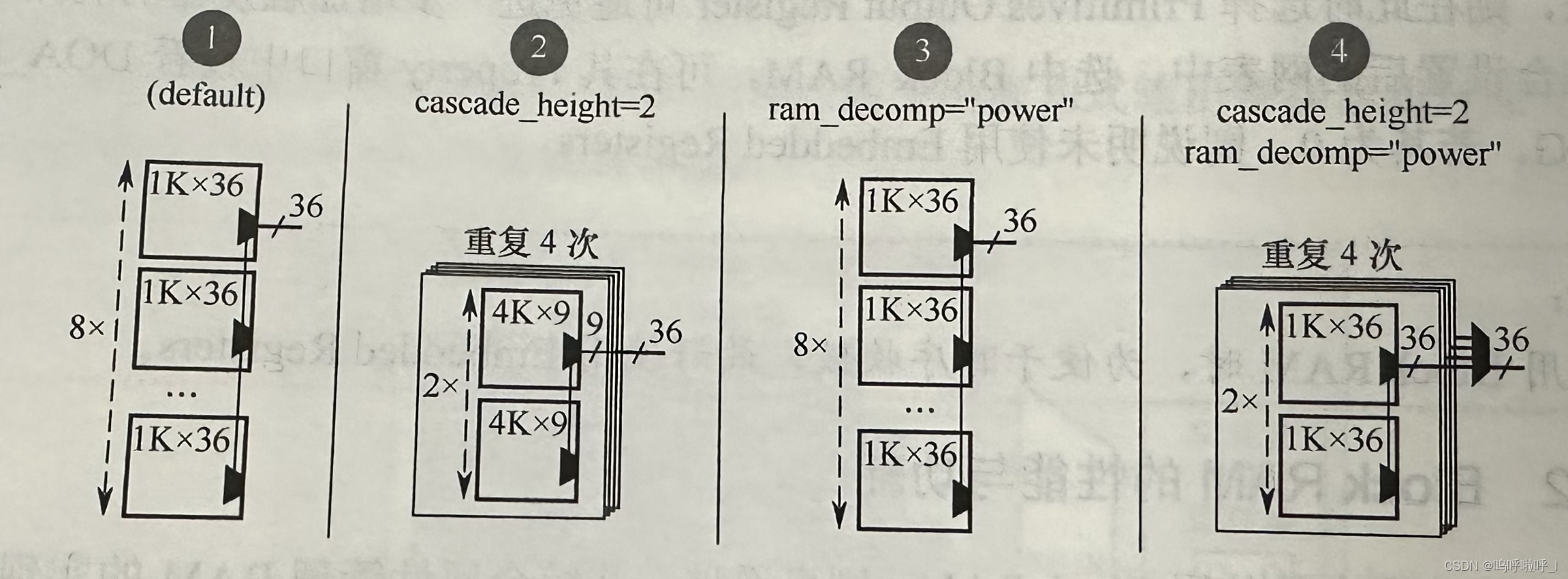

Xinlinx FPGA如何降低Block RAM的功耗

FPGA中降低Block RAM的功耗有两种方式,分别是选择合适的写操作模式以及Block RAM的实现算法及综合设置。我们知道对于采用IP核生成对应的RAM时,会有最小面积算法、低功耗算法以及固定原语,但是采用最小功耗算法有时由于级联长度导致无法实现,我们可以通过综合选项得到一个折中的效果,下面将具体介绍。 一、写操作模式 之前我们介绍过BRAM的各种设计细节,可以参考如下文章: Xinl

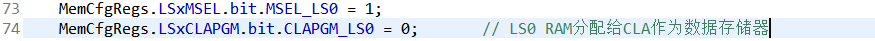

TI的C28x系列芯片的存储结构(2)——CLA的RAM

CLA有自己的程序和数据总线,它的RAM存储区分三种:程序RAM(program RAM)、数据RAM(data RAM)和信号RAM(message RAM)。 ①program RAM CLA的程序必须复制到RAM中才能快速执行。CLA的程序可导入到任意一个LSx RAM中,由CPU完成。 将LSx RAM映射成CLA的program RAM: 例如: 一旦LSx RAM

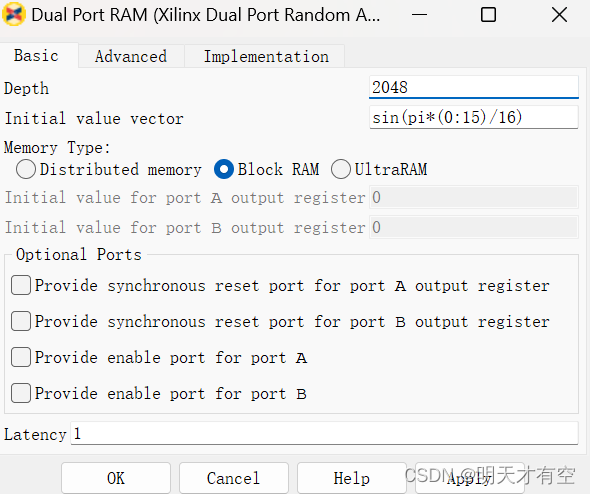

从零开始利用MATLAB进行FPGA设计(五)详解双口RAM

创作于谱仪算法设计过程中的数字能谱生成模块设计。 往期回顾: 从零开始利用MATLAB进行FPGA设计(四)生成优化HDL代码 从零开始利用MATLAB进行FPGA设计(三)将Simulink模型转化为定点数据类型 目录 1.关于双口RAM 2.System Generation中的双口RAM 2.1模块接口 2.1.1形态因素 2.1.2写模式 2.1.3冲突行为 2.2块

CCS7.2中如何切换烧写RAM和Flash版本程序

仿真模式:在工程的 cmd 文件夹选中 F2833x_custom_ram.cmd 文件,且并在工程的 source 文件夹取消选择 DSP28xxx_CodeStartBranch.asm 和 DSP28xxx_SectionCopy_nonBIOS.asm 文件; 烧写模式:在工程的 cmd 文件夹选择 F2833x_custom_flash.cmd 文件,且并在工程的 source 文件夹选

![[IMX9]Suspend to RAM](/front/images/it_default.jpg)