本文主要是介绍AXI4写时序在AXI Block RAM (BRAM) IP核中的应用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在本文中将展示描述了AXI从设备(slave)AXI BRAM Controller IP核与Xilinx AXI Interconnect之间的写时序关系。

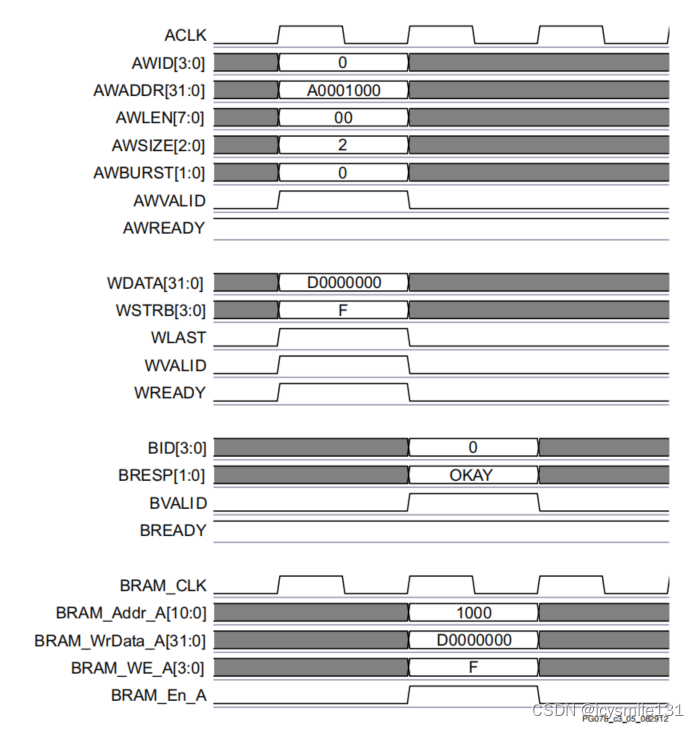

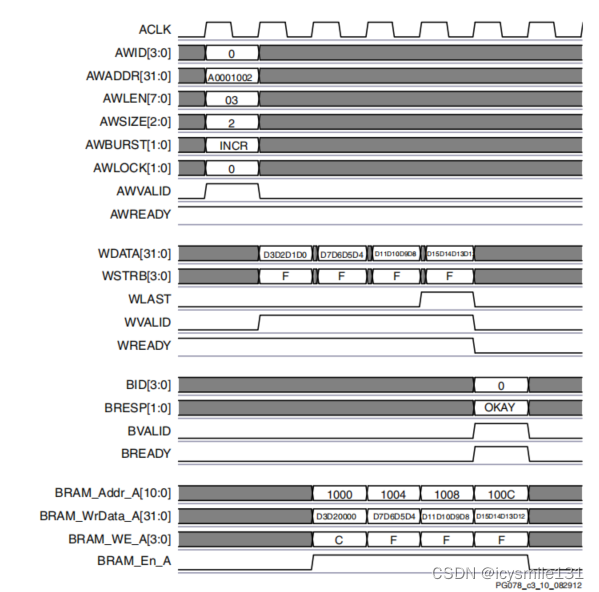

1 Single Write

图1是一个关于32位宽度的BRAM(Block RAM)的单次写入操作的例子。这个例子展示了如何向地址0x1000h的BRAM写入数据,其中C_S_AXI_BASEADDR被设置为0xA000 0000,并且C_S_AXI_HIGHADDR允许超过4k的可寻址BRAM空间。

图1 AXI单次写事务时序图

在AXI BRAM Controller的操作中,有几个关键点需要注意:

(1)AWREADY信号

AXI BRAM Controller通常会在总线上保持AWREADY信号断言(即置高),以便在S_AXI_AWVALID和S_AXI_AWREADY信号都被断言的时钟周期内捕获地址。一旦写地址流水线(通常有两个深度)满了,从设备(slave)AXI BRAM Controller就会否定(即置低)AWREADY信号。

(2)写数据通道

同样的原则也适用于写数据通道。当数据正在写入块RAM的流水线满时,AXI BRAM Controller会否定WREADY信号。这种情况可能在AXI BRAM Controller正在处理先前的burst写数据操作时发生。

(3)ECC(Error Correction Code)

当在全数据宽度的BRAM写传输中启用ECC时,事务的时序与C_ECC = 0(即ECC被禁用)时相同。这是因为ECC的处理通常在内部进行,对外部接口的时序影响很小或没有影响。ECC通常用于检测和纠正数据在传输或存储过程中可能出现的错误。

在AXI协议中,写数据通道(W通道)上的数据确实有可能在写地址通道(AW通道)上的地址信息之前到达AXI BRAM Controller。然而,在这种情况下,AXI BRAM Controller不会立即启动写事务(即它会忽略这些数据),直到写地址通道上有了有效的地址信息供AXI BRAM Controller接受。

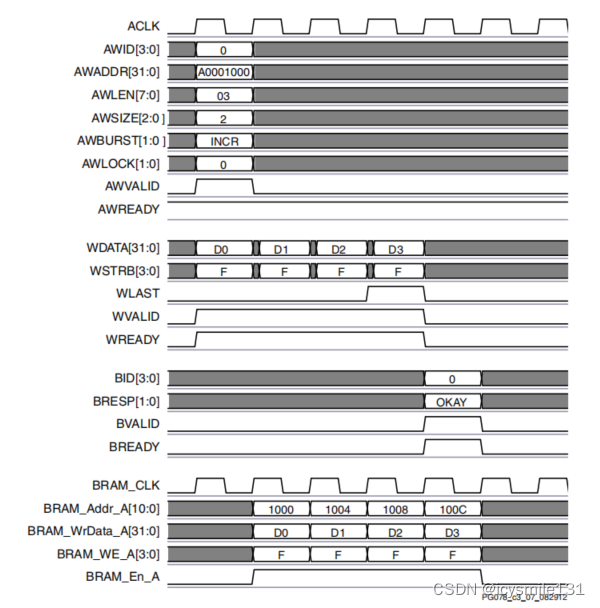

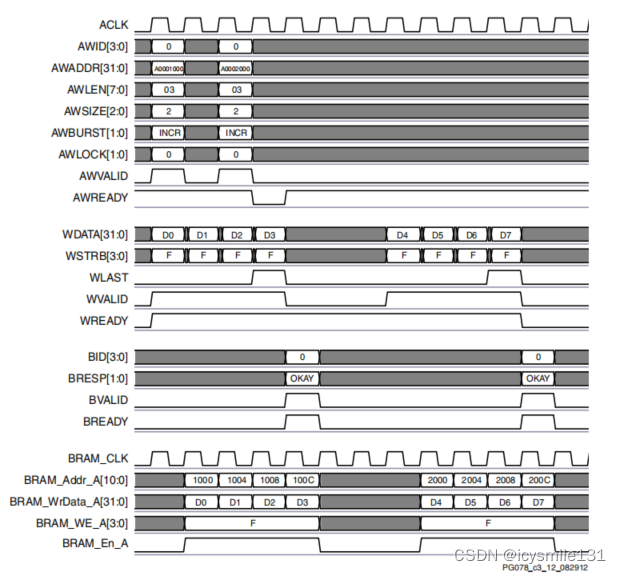

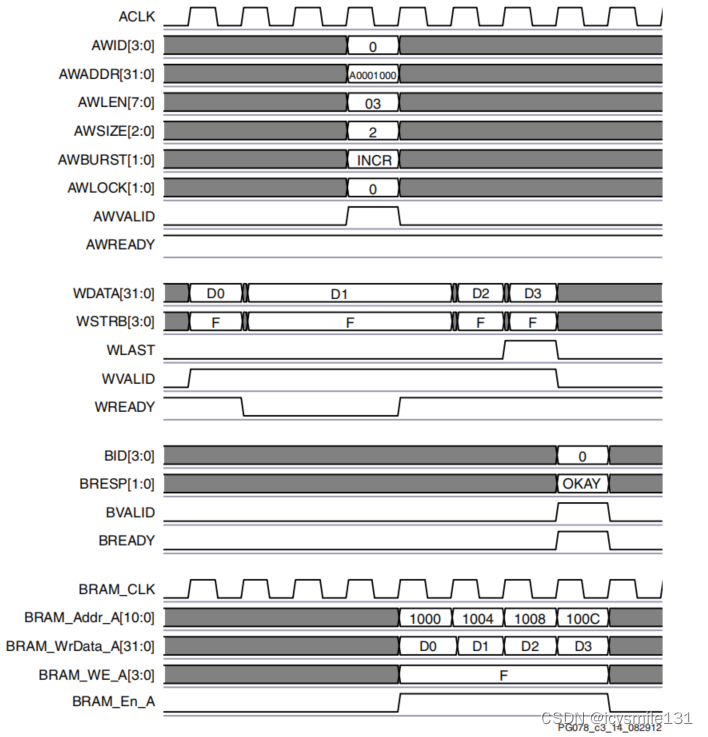

2 Write Burst

图2展示了一个AXI写突发(burst)操作的时序示例,该操作向32位BRAM写入四个字。在地址写通道握手阶段,它传达了突发类型为INCR(递增),突发长度为4个数据传输(AWLEN = 0011b)。写突发操作利用了AXI数据总线的所有字节通道(AWSIZE = 010b)向块RAM传输数据。图3中显示的写突发操作被设置为从BRAM地址0x1000h开始,前提是C_S_AXI_BASEADDR设计参数被设置为0xA0000000,并且C_S_AXI_HIGHADDR允许的地址空间大于4k的可寻址块RAM。

图2 AXI突发写时序图

在AXI写事务中,从设备(slave)不会等待写数据通道上的WVALID信号被断言后再断言写地址通道上的AWREADY信号。这种情况可能会导致死锁条件,并且是不被允许的。AXI协议要求写地址通道(AW通道)和写数据通道(W通道)之间的握手必须正确进行,以确保数据被写入正确的地址,并且不会被错误地丢弃或覆盖。

在正常的AXI写操作中,主设备(master)首先通过AW通道发送写地址和突发信息(如突发类型和长度)。从设备在接收到这些信息并准备好接受数据后,会断言AWREADY信号。一旦AWREADY信号被断言,主设备就可以开始通过W通道发送数据。数据通过W通道传输时,主设备会断言WVALID信号,而从设备在准备好接收数据时会断言WREADY信号。只有当WVALID和WREADY信号在同一时钟周期内都被断言时,数据才会被传输。

如果从设备不等待WVALID信号被断言就断言AWREADY信号,那么主设备可能会在没有准备好发送数据的情况下开始通过W通道发送数据,这可能导致数据丢失或写入错误的地址。因此,AXI协议要求从设备必须等待WVALID信号被断言后再断言WREADY信号,以确保数据的正确传输。

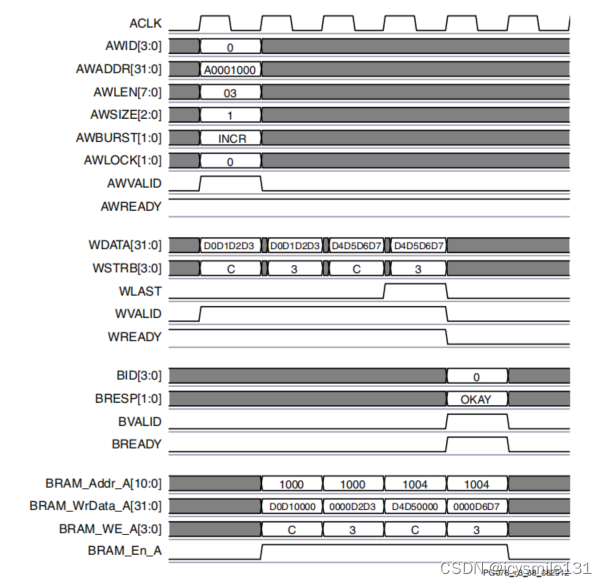

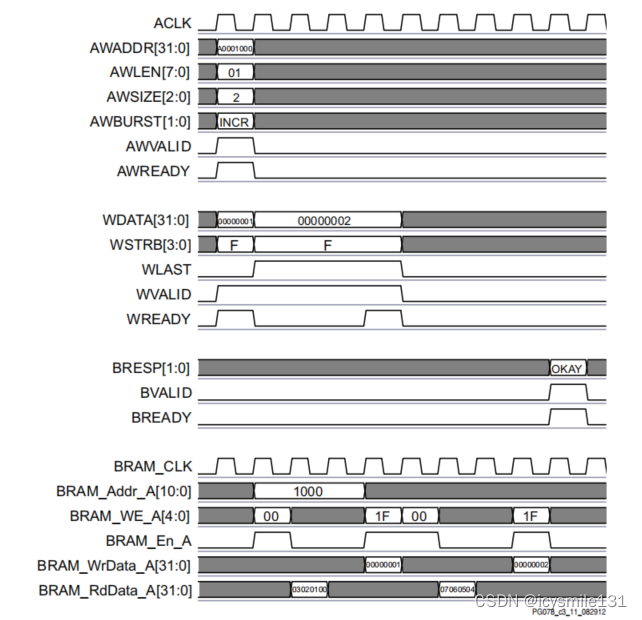

3 Narrow Write Bursting

图3展示了AXI BRAM Controller支持窄突发(narrow burst)操作的示例。窄突发是指主设备以小于BRAM数据宽度的数据大小进行突发传输。如果突发类型(AWBURST)被设置为INCR(递增)或WRAP(环绕),那么每个数据节拍(data beat)在AXI总线到BRAM接口的有效数据会进行旋转。AXI BRAM Controller会处理AXI上的每个数据节拍,作为对应到块RAM的数据节拍,无论有效字节通道的大小如何。

图3 AXI 窄突发写时序

在这种情况下,AXI WSTRB(Write Strobe,写选通)信号会被转换为BRAM的写使能(write enable)信号。只有当BRAM地址遇到全地址(数据)宽度边界时,才会进行递增,这是由于进行了窄突发写入块RAM。

在图3中,以一个32位BRAM为例,AXI主设备请求的是一个半字(halfword,即16位)突发,包含4个数据节拍。AWSIZE被设置为001b,这表示每次突发传输的数据大小是半字。在这种设置下,BRAM Controller会将每个16位的数据节拍映射到BRAM的适当位置,并且只在遇到32位边界时才会递增BRAM地址。这意味着尽管突发操作是以16位为单位进行的,但BRAM地址的更新是以32位为单位的。

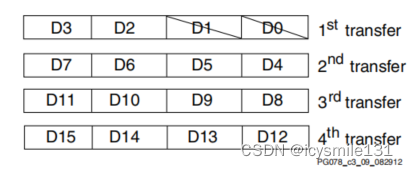

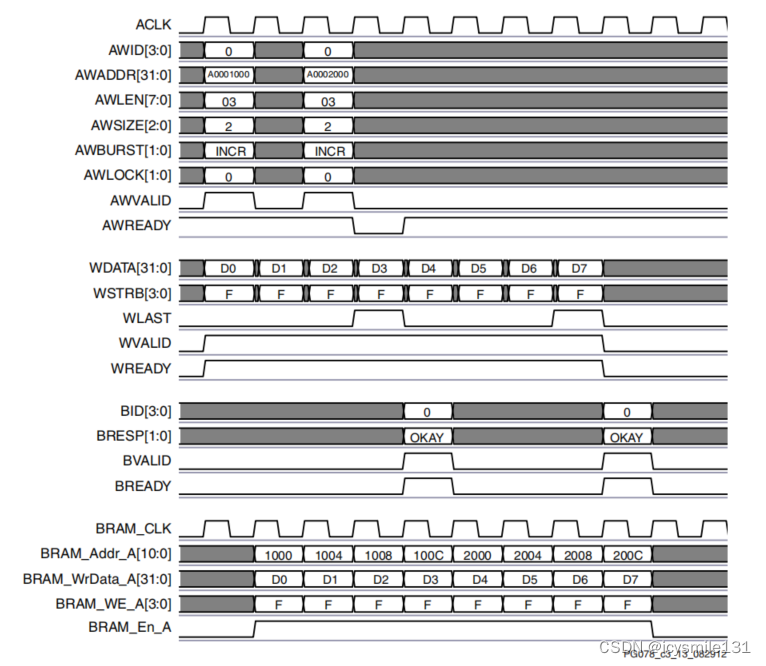

4 Unaligned Write Bursting

AXI BRAM Controller支持非对齐突发传输。非对齐突发传输发生在例如32位字突发大小不是从与字内存位置匹配的地址边界开始时。起始内存地址允许不是0x0h、0x4h、0x8h等。

图4所示的例子说明了一个非对齐的字突发传输,该传输包含4个数据节拍,从地址偏移量0x1002h开始(假设C_S_AXI_BASEADDR被设置为0xA000 0000,并且C_S_AXI_HIGHADDR允许超过4k的可寻址内存)。相关的时序关系如图5所示。

图4 AXI非对齐突发写传输

非对齐地址对应于写端口的BRAM_WE信号,以反映有效的字节通道。

在非对齐突发传输中,AXI BRAM Controller需要能够处理从非字边界开始的突发传输。也就是说,如果突发传输的起始地址不是字地址的整数倍(即不是0x0h、0x4h、0x8h等),那么传输的数据可能需要跨越多个内存位置。

AXI BRAM Controller通过检查每个数据节拍的字节使能(byte enable)或写选通(write strobe)信号来确定哪些字节是有效的,并将这些数据正确地写入BRAM。在写操作中,BRAM_WE信号用于指示哪些字节通道是活动的,并且应该被写入数据。

图5 AXI非对齐突发写时序

5 ECC Write Burst

图6展示了一个AXI写突发操作的两个数据节拍的时序。

由于需要执行读-修改-写序列以正确更新块RAM中的ECC(错误检查和纠正)校验位,所以存在额外的延迟。

图6 带ECC的AXI写突发

6 Write Pipeline

AXI BRAM Controller IP核支持两个活动的写操作,它可以同时接收两个写地址请求(通过写地址通道AW),但数据(通过写数据通道W)需要按照地址的顺序来传输。当写地址流水线已满时,控制器会通过否定AWREADY信号来通知总线。只有当第一个流水线操作完成后,新的写传输才可以发生(这通过AWREADY信号的断言来指示)。

AXI BRAM Controller不支持写数据的交织。在写数据通道上的数据必须与写地址通道上呈现的地址(对于该数据)顺序相同。

写数据通道通过断言WREADY信号来响应写传输。当写数据通道没有因前一个事务而忙碌时,AXI BRAM Controller会接受数据。它还支持在AWVALID和AWREADY之前提前断言WREADY到WVALID,以便在地址验证之前就开始准备接收数据。

当写地址(通过写地址通道AW)有效并被AXI BRAM Controller接收时,Controller可以在同一个时钟周期内从写数据通道(W)接收数据。写地址和相应的写数据可以在连续的时钟周期内几乎同时到达,只要Controller准备好(通过WREADY信号指示)并且遵循AXI协议的时序要求。

WREADY信号是AXI BRAM Controller中用于指示接收端何时准备好接收写数据的一个信号。当WREADY被断言(即设置为高电平或逻辑真)时,发送端(如AXI Interconnect或其他AXI主设备)知道它可以在下一个时钟周期发送写数据(通过WVALID信号和WDATA总线)。

AXI BRAM Controller确保BREADY信号(用于指示接收端准备好接收从BRAM读取的数据)不会在WVALID和WREADY之前被断言。这是为了确保在数据被写入BRAM之前,任何潜在的读取操作都不会开始。这有助于防止数据冲突和不一致,并确保系统的正确性和可靠性。

图7展示了AXI BRAM Controller中写地址的流水线能力。这个示例说明了AXI BRAM Controller从AXI Interconnect看到写数据通道上的间隙时的情况。

图7 AXI流水线突发写传输

AXI BRAM Controller确实支持连续数据流下的背靠背(back-to-back)突发写操作,这是AXI协议的一个重要特性,可以显著提高数据传输的效率和吞吐量。

当AXI Interconnect为AXI BRAM Controller提供连续的数据流时,两个流水线化的突发写操作之间在BRAM接口上没有空闲的时钟周期,即数据可以连续不断地写入BRAM,而无需等待前一个操作完成。

图8展示了四个数据节拍(data beats)的背靠背流水线化突发写操作的时序。

为了实现AXI BRAM Controller写端口的100% BRAM接口利用率,需要满足以下条件:

● 没有单个写突发

● 写突发必须大于两个数据节拍

● 写突发操作必须是INCR或WRAP突发类型

图8 AXI背靠背写突发时序

7 Delayed Write Address

在接收到有效的写地址之前,会对写数据进行节流(throttle)的行为。具体来说,这意味着在接收到下一个有效的写地址之前的一个数据节拍(data beat)之后,AXI BRAM Controller会暂停接受新的写数据。

在双端口模式下,当ECC(错误检查和纠正)功能被禁用时,AXI BRAM Controller会接收提前的WVALID和WDATA信号。这允许在写地址到达之前就开始准备写数据,从而提高了数据传输的效率。即使在这种情况下,写数据也不会在接收到有效的写地址之前被写入BRAM。

图9 AXI延迟写地址时序

这篇关于AXI4写时序在AXI Block RAM (BRAM) IP核中的应用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!