bram专题

BRAM IP Native模式使用

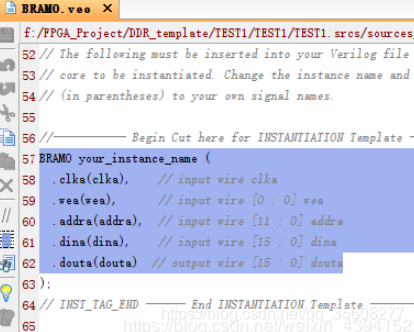

简介 BRAM(Block RAM)是FPGA(Field-Programmable Gate Array)中的一种专用RAM资源,固定分布在FPGA内部的特定位置。该内容主要对BRAM(Block RAM”的缩写)Native模式下IP界面做详细描述和使用。 界面介绍 Basic界面 1、选择对外接口,可以是AXI总线控制读写也可以是Nativ

模拟14位相机输出输入到bram Verilog代码

1 模拟输出代码 `timescale 1ns / 1psmodule simulate_camera_out (input clk,input rest_n,output camera_clk, //像素时钟output [13:0] camera_data, //像素值数据output [19:0] pixel_xy, //此时输出的像素值坐标output reg frame_vali

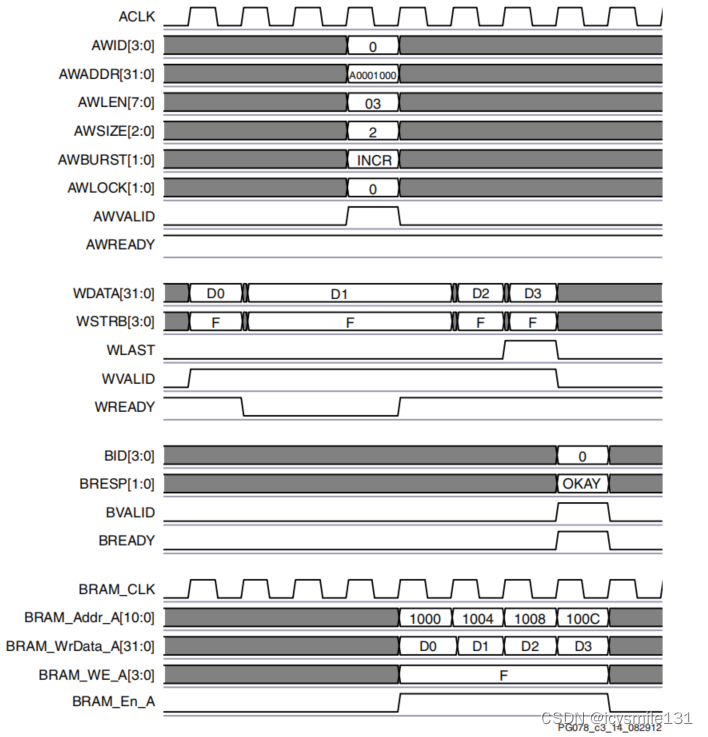

AXI4写时序在AXI Block RAM (BRAM) IP核中的应用

在本文中将展示描述了AXI从设备(slave)AXI BRAM Controller IP核与Xilinx AXI Interconnect之间的写时序关系。 1 Single Write 图1是一个关于32位宽度的BRAM(Block RAM)的单次写入操作的例子。这个例子展示了如何向地址0x1000h的BRAM写入数据,其中C_S_AXI_BASEADDR被设置为0xA000 0000,并

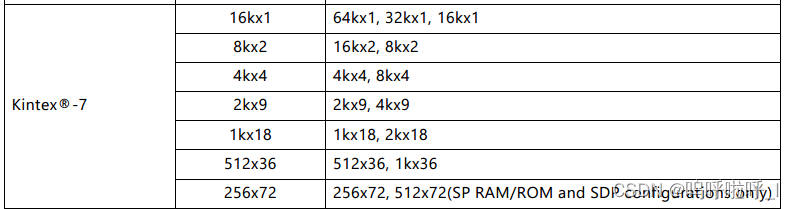

Xinlinx FPGA内的存储器BRAM全解

目录 一、总体概述1.7系列FPGA的BRAM特点2.资源情况 二、BRAM分类1.单端口RAM2.简单双端口RAM3.真双端口RAM 三、BRAM的读写1、Primitives Output Registers读操作注意事项2.三种写数据模式(1)Write_First(2)Read_First(3)No_change 3.读写冲突(1)读写时钟同步(2)读写时钟异步 四、三种BRAM实

Block Design AXI BRAM Error

1、现象: 在Block Design 中添加AXI BRAM ,如图: 点击validate design 后,提示如下报错: ERROR: [axi_bram_cntlr-1] Port-A interface property <CONFIG.READ_WRITE_MODE> is not defined. ERROR: [Common 17-39] 'send_msg_id'

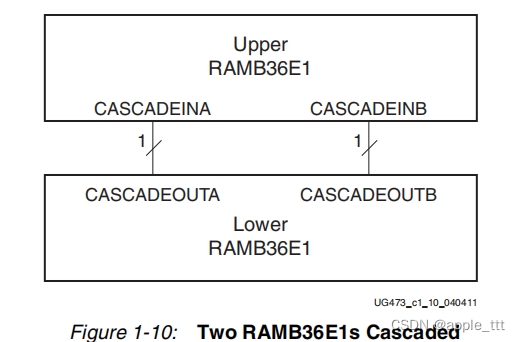

BRAM底层原理详细解释(1)

目录 一、原语 二、端口简述 2.1 端口简介 2.2 SDP端口映射 三、端口信号含义补充说明 3.1 字节写使能(Byte-Write Enable)- WEA and WEBWE: 3.2 地址总线—ADDRARDADDR and ADDRBWRADDR 3.3 数据总线—DIADI, DIPADIP, DIBDI, and DIPBDIP & DOADO, DOPADOP,

Zynq 7000 PL和PS通信——使用BRAM

Zynq 7000 PL和PS通信——使用BRAM 介绍1 准备工作2 PL搭建BRAM3 下载PL程序4 编写Linux应用程序5 问题5.1 BRAM的寻址的问题5.2 PS地址映射 介绍 Xilinx公司的Zynq 7000系列SoC除了有功能强大的FPGA,还集成了带有双核ARM Cortex A9的PS。在协同使用PS和PL时,就不免需要在PS和PL之间进行数据交互。

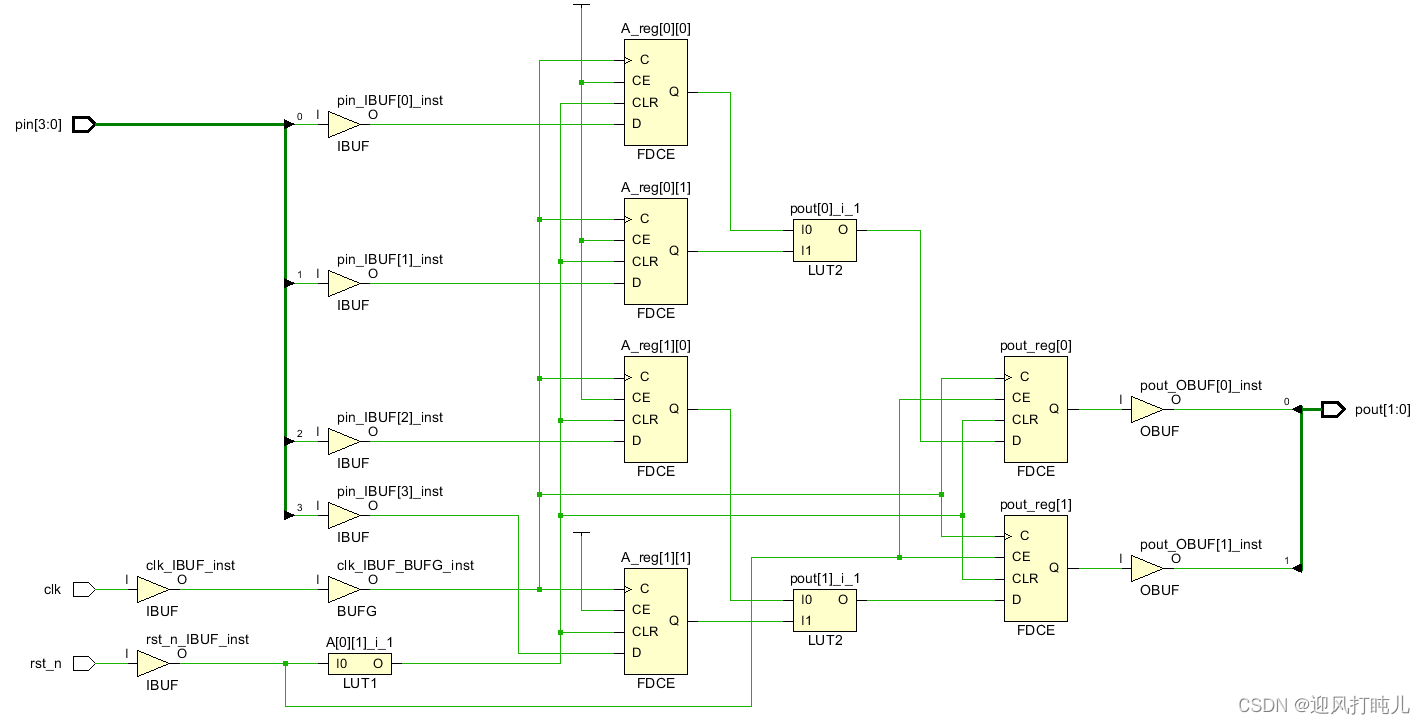

vivado里的LUT、LUTRAM、FF、BRAM、DSP、IO、BUFG、MMCM资源介绍

vivado里的LUT、LUTRAM、FF、BRAM、DSP、IO、BUFG、MMCM资源介绍 提示:以下是本篇文章正文内容,写文章实属不易,希望能帮助到各位,转载请附上链接。 vivado实现电路用到的资源类型 LUT(Look-Up Table):查找表,它接收一组输入信号,并根据预先定义的逻辑函数表(Look-Up Table)输出结果,LUT 可以实现任意逻辑函数,如与、或

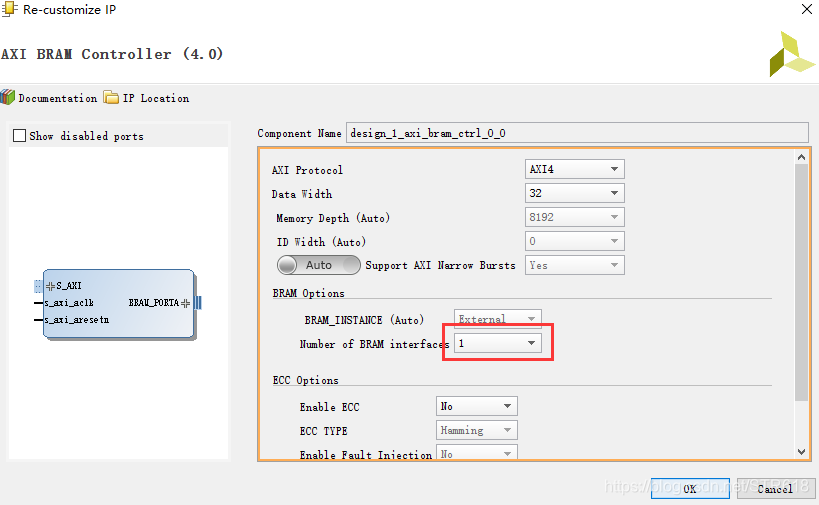

ZYNQ通过AXI_BRAM实现PL与PS数据互联

一、AXI BRAM Controller PS模块通过axi_bram模块,可以使用AXI接口读写PL内的Block RAM,实现PS与PL之间的数据互联.。 axi_bram需要与Block Memory Generator模块共同使用,axi_bram将PS的AXI操作转化为bram的控制接口时序。 二、配置 1、首先搭建好zynq的基础框架,保证设备可以正常启动,非此处讨论重点,略去

URAM和BRAM有什么区别

无论是7系列FPGA、UltraScale还是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我们所说的URAM。BRAM和URAM都是重要的片上存储资源,但两者还是有些显著的区别。 容量 BRAM的容量为36Kb,且可当作两个独立的18Kb BRAM使用。对于一个36Kb的BRAM,其最能

赛灵思(Xilinx)BlockRam(Bram)的结构与读逻辑解释

如图所示, bram的由很多latches和寄存器构成的bram块构成,通过Mux数据选择器,将数据送入输出寄存器,最终输出。由此图可知,bram的reset仅仅对输出寄存器重置,而不会重置内部存储数据。 对于Bram的读逻辑,由图可以发现,en有效后,数据会在下一个时钟上升沿后,出现在输出寄存器上。也可以看到reset信号,并不影响下一个时钟信号到来后输出的值(MEM(bb)),

BRAM对应的IP核调用和使用

Vivado软件中包含有三种类型的 IP核,包括数据处理类IP核、驱动类IP核、存储类IP核。 与BRAM对应的存储型IP核是Block Memory Generator(BMG) 调用BRAM 首先在Vivado界面的右侧选择IP Catalog 选项。然后就可以在IP 目录中,选择想要的IP核,此处在搜索框输入BRAM,选择我们要使用的BRAM IP核。basic设置 (1)在compo

ZYNQ linux下AXI_BRAM的使用方法,PS与PL端数据交互

1、AXI总线、AXI接口、AXI协议 总线是一组传输通道,是各种逻辑器件构成的传输数据的通道;接口是一种连接标准,又常被称为物理接口;协议是数据传输的规则。 PS与PL连接方式主要是通过AXI总线进行的。ZYNQ上的总线协议有AXI4, AXI4-Lite, AXI4-Stream三种总线协议。而PS与PL之间的接口(AXI-GP、AXI-HP、AXI-ACP)只支持AXI4与AXI4-Lit

zynq入门系列(1)AXI_Lite总线使用方法—上(PS PL通过BRAM双工通信)

(一)引言 第一次写博客,算是记录一下2021年开始zynq和fpga方向入门学习的东西吧,算是督促自己学习。 为什么突然想起写博客,在学习过程中,所有店铺的教程的pdf,都讲了如何去使用搭建一个例程,有部分关键信息没有给讲解。比如正点原子zynq 教程 sdk篇 bram的工程,对初学者最重要的其实是AXI_Lite总线的使用,但是官方并没有

ZYNQ学习之路(二):PS与PL通过BRAM交互

在 ZYNQ SOC 开发过程中, PL 和 PS 之间经常需要做数据交互。对于传输速度要求较高、数据量大、地址连续的场合,可以通过AXI DMA 来完成。而对于数据量较少、地址不连续、长度不规则的情况,此时 AXI DMA 便不再适用了。针对这种情况,可以通过 BRAM 来进行数据的交互。 实验目的:将数据从PS端写入PL部分的BRAM,然后将数据从BRAM读出来与原数据进行比较,判断是否写入