本文主要是介绍zynq入门系列(1)AXI_Lite总线使用方法—上(PS PL通过BRAM双工通信),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

(一)引言

第一次写博客,算是记录一下2021年开始zynq和fpga方向入门学习的东西吧,算是督促自己学习。

为什么突然想起写博客,在学习过程中,所有店铺的教程的pdf,都讲了如何去使用搭建一个例程,有部分关键信息没有给讲解。比如正点原子zynq 教程 sdk篇 bram的工程,对初学者最重要的其实是AXI_Lite总线的使用,但是官方并没有过多的讲这部分的原理,我们只是按照教程复制黏贴,回过头来在恍然发现错过了非常重要的东西,我想写的第一个就是bram当中AXI_Lite总线的使用,

至于基础理论我就不写了,主要 参考正点原子,黑金,米连等教学资料。我主要讲如何去使用,以及某些例程上为什么会这么写,例程的逻辑点,寻址驱动方向等等。 我写的方向主要是如何去使用,至于基础理论还得看官方资料和各大教程

(二)总览

例程来自正点原子启明星或领航者ZYNQ嵌入式开发篇(SDK篇)BRAM的ps与pl数据交互。

如图,这就是正点原子官方的例程bd。没什么问题,他实现的功能是ps向pl发送数据,而后ps和pl读取ps发送的数据。例程我认为这只是单工通信,因为通信是ps主导的,如果我们要把pl的数据发送至ps,那么这个实验例程就行不通了。本次的目标就是把此例程改成双共通信,pl定时向ps发送数据,ps读取。ps也能向pl发送数据。

(三)PL部分修改

首先、ps要能读取pl发起的通信,那么为了方便,每次pl发起时都应当产生一个中断信号给ps,然后ps收到信号后读取bram的数据,完成pl向ps发送数据的过程。那么zynq的arm核上一个添加一路中断,如图。

中断来自bram b端口的控制ip,每完成一次pl数据发送,就会输出一个脉冲信号。如图,rd为正点原子提供的ip核(只能读取ps发送的数据),wrrd为我修改后的ip(pl定时发送数据给ps,同时能读取ps发的数据),wrrd多了一个中断端口intr。

, 修改后总bd工程如下,wrrd ip核的中断接到ps上,ila为在线调试ip,这里不多讲

接下来就是wrrd ip的讲解,也是本文重点,主要是理解怎么使用AXI_Lite总线。

很多新同学觉得,axi4是一个接口,一个总线。所以按理来说ip核和axi接口的关系是如下图所示的

其实并不然,在官方给的带axi4总线的自定义ip核里,官方给出的结构是如下所示

在这里打开它的RTL似乎更容易理解,我们先来看看这个ip核有哪些接口

不知有没有看明白,左图的左边核右上对应的是axi所需要的接口,而右下一串ram_xxx是我们自定义功能的ip。我们继续打开它的RTL

这么大一串是不是有点吓人,这些我们暂时不用关心。这些黄色的都是axi总线的握手协议,我们看右下角有一个蓝色的方块,那就是我们自定义功能的模块,我们找到它

由此可以看出,带axi接口的自定义ip核,其实就是官方给了我们一个axi握手协议的模块,我们需要在这个模块下例化我们自己写的功能模块就行了。

现在来看一下详细的代码,我们先来看实现axi总线的代码

首先就是定义我们需要的模块,我们自定义模块例化的接口给引到上层模块去,然后中间有一大陀,具体原理参考axi协议的内容,在这里我只说明用法以及我们需要关注的东西。

我们需要关注的就是slv_reg这个寄存器,他的位宽设置在创建自定义ip时选择。slv_reg这个寄存器的作用就是建立ps与pl之间的通信,如图slv_reg0是读开始信号(也是ps向pl写数据完成信号)slv_reg2寄存器是ps向pl写数据的长度。

那么,axi接口里都用的slv_reg寄存器,而有一个不是呢?因为slv_reg寄存器是pl接收信号的寄存器,而ip核当中,为了验证ps是否发送正确,官方的接口做了个环回,也就是说,slv_reg是接收信号的寄存器,但是他又发送给了pl,如果pl要用ps发送来的数据,那么我们直接在例化当中连接slv_reg寄存器即可,如果要把pl的信息发送给ps,如wr_len信号,那么就需要我们自己去更改线信号了。

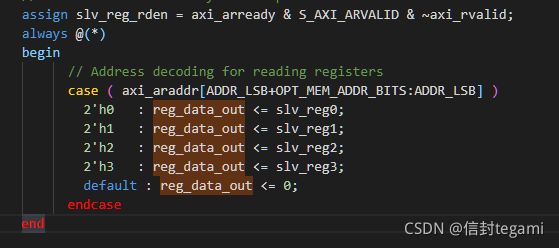

如下图,我们先找到pl的信号是如何发送给ps的。如图,slv_reg是官方接收ps端数据的寄存器,官方在这里做了一个回环,让ps发送来的数据再次传回ps,我们如果需要用pl给ps发数据,那么修改也很简单,slv_reg3是空出来的寄存器,我们把它定义成我们需要输出的信号就行了

修改前

修改后

接下来就是自定义模块例化的接口,我们来看看,在这里接口分了两类,上面6个连接的是axi的接口,通过这里的数据会从axi总线通向ps端,如上图1橙色的线,intr以下是rom端口,连向bram,如下图橙色的线。

(四)总结

pl部分就先说到这,下一期讲讲ps端是如何与pl进行联系的,以及他们实现的效果也会在下期展示。

总而言之,AXI4_lite是一个轻量级的总线,多用于控制和小数据量传输,我们在使用的时候主要关注他slv_reg寄存器,至于哪个slv_reg寄存器实现什么功能,还需要通过ps去配合使用。

这篇关于zynq入门系列(1)AXI_Lite总线使用方法—上(PS PL通过BRAM双工通信)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!