zynq专题

ZYNQ LWIP (RAW API) UDP函数学习

1 RAW API接口 RAW API是基于回调函数实现的API接口,它是很底层的API接口,这需要开发者对LwIP有较深的了解才能很好使用它,RAW API的核心就是对控制块的处理,因为对于报文数据的处理、注册回调函数等都是需要开发者自己去实现,都是比较麻烦的,但是有一个优点,那就是处理数据效率高。 2 RAW API的UDP函数说明 udp_new()–新建控制块 在使用UDP协议进行通

ZYNQ MPSOC FPGA 仿真 教程

1. **FPGA与MPSOC**: FPGA (Field Programmable Gate Array) 是一种可以通过编程配置的集成电路,适用于各种应用和功能。MPSOC (Multi-Processor System on Chip) 是集成了多个处理器(通常是微处理器)的系统芯片,用于处理复杂的应用,如图像处理、网络通信等。 2. **仿真与分析**: - **仿

【ZYNQ MPSoC开发】lwIP TCP发送用于数据缓存的软件FIFO设计

设计背景 任务是在ZYNQ的PS上使用裸机运行lwIP协议栈使用TCP把PL端通过AXI DMA传来的将近100K采样率的ADC数据发送出去,但由于数据带宽很大,有853.3mbps,所以在每一次AXI DMA简单传输结束后,lwIP未必有足够的发送buffer立即把数据发送走,如果是发送完再进行下一次简单传输的思路,则会很大地限制了整个系统的带宽,一个简单的思路是每次传输完成后判

petalinux,Zynq UltraScale+ MPSoC;WARNING: Failed to load PMUFW, doesn't exist in pre-built.

petalinux-package --pmufw ./images/linux/pmufw.elf 这个参数貌似没有生效; 解决办法: cp images/linux/pmufw.elf ./pre-built/linux/images/

江山易改本性难移之ZYNQ SDK API函数笔记(UART)

初学Xilinx ZYNQ SDK的开发,下面记录使用到的API函数及自己的理解。若有误,还请指教。 UART函数 常用编程步骤: 1.查找输入设备的ID查找设备; 2.输入的配置信息初始化; 3.设置工作模式; 4.设置波特率; 5.设置RxFIFO的中断触发等级; 6.设置接收超时时间; 7.设置UART的中断触发方式 配置UART只需要以上5个步骤,其中6、7是笔者做串口不定

江山易改本性难移之ZYNQ SDK API函数笔记(Timer)

初学Xilinx ZYNQ SDK的开发,下面记录使用到的API函数及自己的理解。若有误,还请指教。 Timer函数 常用编程步骤: 1.查找输入设备的ID查找设备; 2.输入的配置信息初始化; 3.加载计数周期; 4.设置自动装载模式; 5.启动定时器; 配置GPIO只需要以上5个步骤。 1、XGpioPs_Config *XGpioPs_LookupConfig(u16 Devi

万变不离其宗之ZYNQ串口介绍

导语 串口是我们在设计程序中最常用的接口,串口是硬件系统运行状态的忠实打印者,可以完成数据的传输、log输出等功能。 1.串口介绍 通信的两种方式:串行通信、并行通信 串行通信方式分为:同步通信、异步通信 关于传输方向:单工、半双工、全双工 UART(异步串行通信) ZYNQ的

4 - ZYNQ 信号、接口与引脚

文章目录 1 ZYNQ信号、接口与引脚1.1 电源引脚1.2 PS信号引脚1.3 PL信号引脚1.4 PS和PL交互接口 1 ZYNQ信号、接口与引脚 ZYNQ的信号、接口与引脚如下图所示,主要分为: PS部分PL部分PS和PL交互部分PS和PL共用部分(如JTAG) 1.1 电源引脚 PS与PL部分均需要多种电平的供电电源,电源需要从特定的电源引脚接入芯片,相关电源

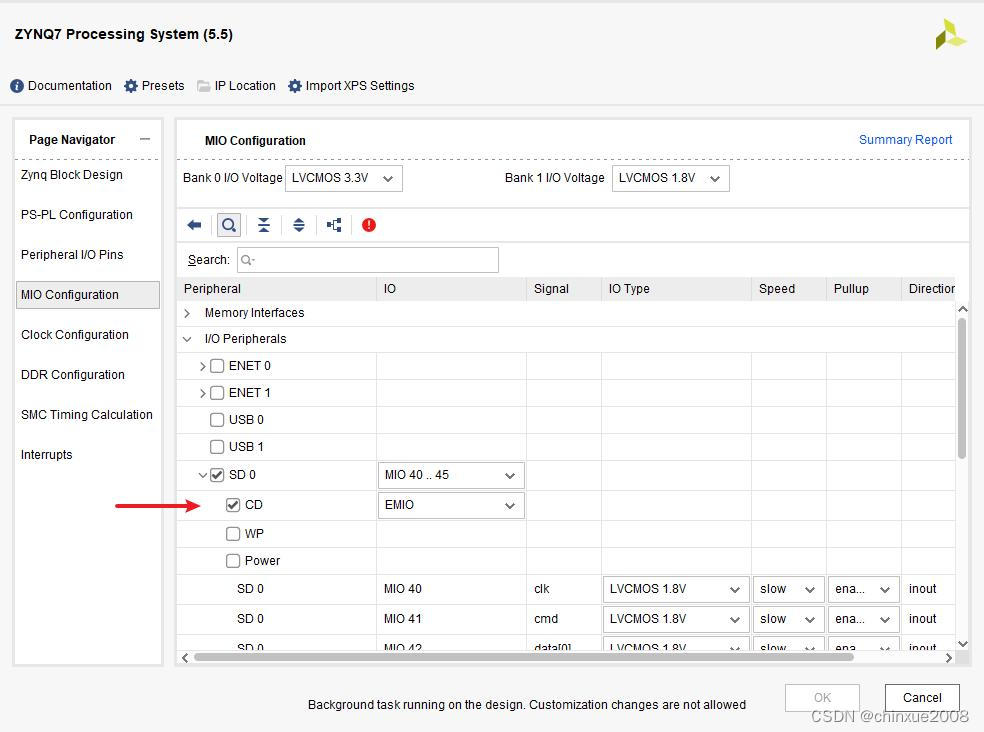

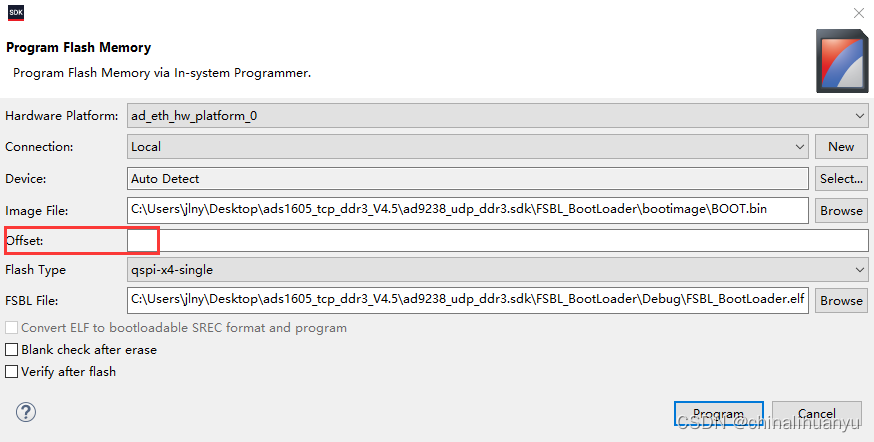

【ZYNQ MPSoC开发】PS裸机多核程序的固化

写在前面 多核程序的固化总体操作流程与单核程序固化相同,针对本文中的一些操作,大家如果有不清楚的,可以参考我之前写的单核固化的博客。 共通前置步骤 这是区别于单核固话的主要不同之处。以我的程序为例,我用到了两个核心,分别跑在A53_0和A53_1上,结构如下图所示: 1,首先对各个核心的应用程序都build好,生成.elf文件。

ZYNQ 7020 学习记录-1点灯

系列文章目录 1.点灯 文章目录 系列文章目录前言一、ZYNQ是什么?二、FPGA开发流程1.流程图2.工程管理3.需求分析4.系统框图5.编写RTL代码6.Modelsim 手动仿真7.Vivado工程 总结 前言 由于研究生课题组所研制的设备HIGH-POWER SHM SYSTEM是基于ZYNQ的,以下是本人自学ZYNQ的学习记录,所用板卡为:基于 XILINX Z

【1213工作日志】ZYNQ的中断应用

【1213工作日志】ZYNQ的中断应用 /** main.c** Created on: 2018年12月3日* Author: xizi.cheng*//** main.c** Created on: 2018年10月7日* Author: xizi.cheng*//** main.c** Created on: 2018年9月27日* Author: xi

zynq axi-dma 接口参考资料

参考资料: Xilinx官方参考文档:PG021_axi_dma、UG585_zynq_7000_TRM等 AXI DMA开发 http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html 黑金教程 course_s2_ALINX ZYNQ开发平台SDK应用教程V2.02.pdf 米联客教程 S03_CH01_AXI_D

Zynq AXI总线

S02_CH12_ AXI_Lite 总线详解 - 米联客 - 博客园 12.1前言 ZYNQ拥有ARM+FPGA这个神奇的架构,那么ARM和FPGA究竟是如何进行通信的呢?本章通过剖析AXI总线源码,来一探其中的秘密。 12.2 AXI总线与ZYNQ的关系 AXI(Advanced eXtensible Interface)本是由ARM公司提出的一种总线协议,Xilinx从6系列的FPG

Python与Zynq沟通的桥梁,米尔PYNQ开发板资料分享

前言:PYNQ全称为Python Productivity for Zynq,即在Zynq全可编程ARM&FPGA融合处理架构的基础上,添加了对Python的支持。 PYNQ希望能够借助Python语言本身易用易学、扩展库多而全、社区活跃贡献度高等特性,有效降低Zynq嵌入式系统的开发门槛,并为人工智能,ADAS,机器视觉等高拓展性/高复杂度应用需求提供更好支撑。PYNQ将ARM处理器与FPGA

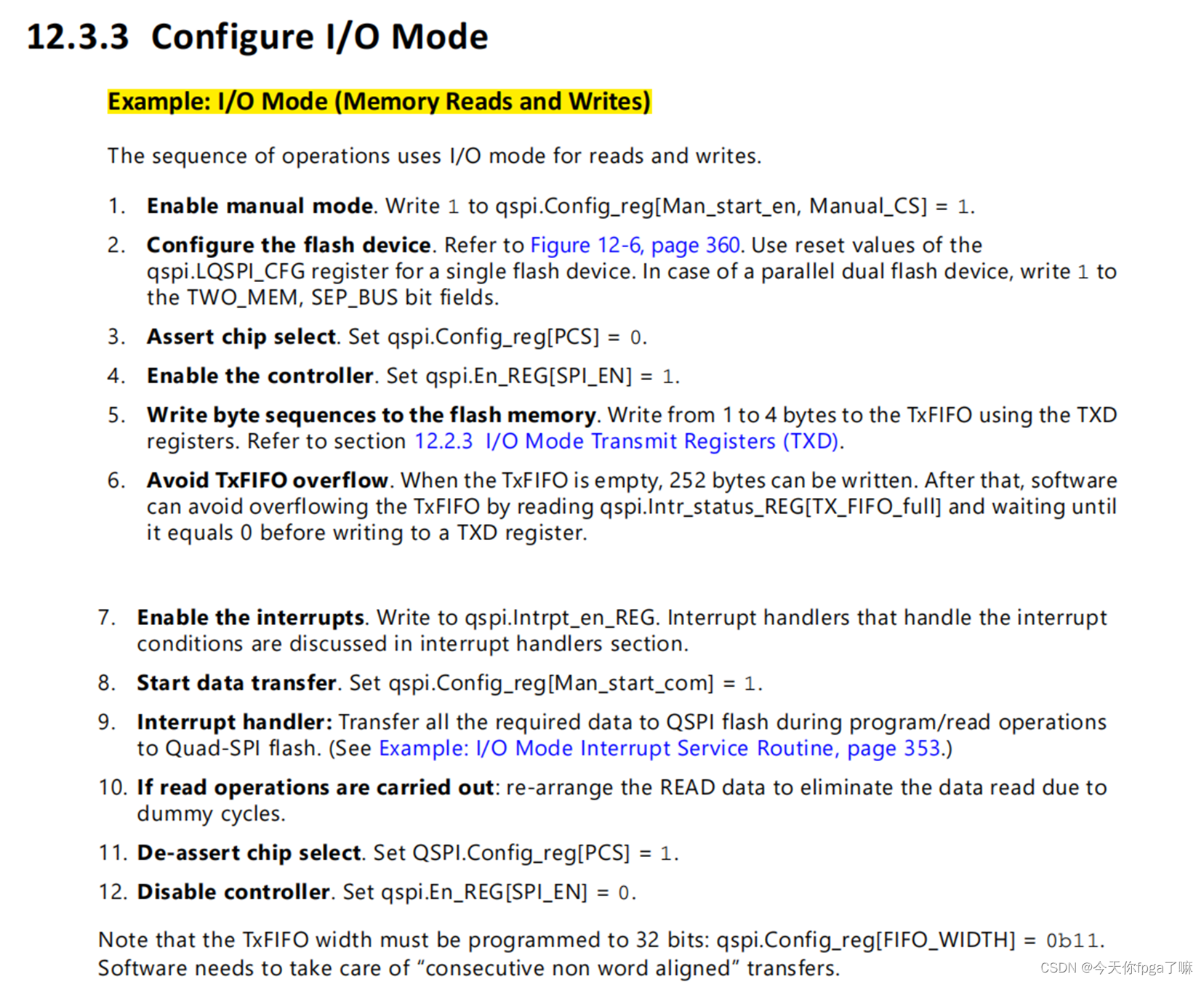

flash介绍(zynq篇)

简介:Flash存储器(又称闪存)是一种非易失性存储器. 页是读写的基本操作单位。(页写前需要进行擦除操作(全部为1),写操作是实现1→0操作) 注意:zynq中有板载flash控制器的ip核,所以相对于纯fpga来讲操作flash很简单 一、flash接口(主要:spi_flash) STD接口就是标准的SPI接口,在手写spi flash控制器里有介绍。 管脚的介绍: 常见的

zynq-7015启动分析及裸机BootLoader编写(未完待续)

使用lwip-tcp远程对QSPI进行更新、QSPI FLASH启动 W25Q128资料: W25Q128JV datasheet(1/78 Pages) WINBOND | 3V 128M-bit serial flash memory with dual/quad spi (alldatasheet.com) UG585资料: Zynq 7000 SoC Technical Referenc

基于Zynq 7000 SoC的迁移设计

基于Zynq 7000 SoC的迁移设计 Vivado IDE工具使用IP集成器进行嵌入式开发。各种IP Vivado IDE IP目录中提供,以适应复杂的设计。您也可以添加 自定义IP到IP目录。 您可以将基于Zynq 7000平台处理器的设计迁移到Vivado design Suite中 使用以下步骤。 1.生成系统基础设施。 a.使用所需的板或可编程设备创建Vivado项目。 b.在Flow

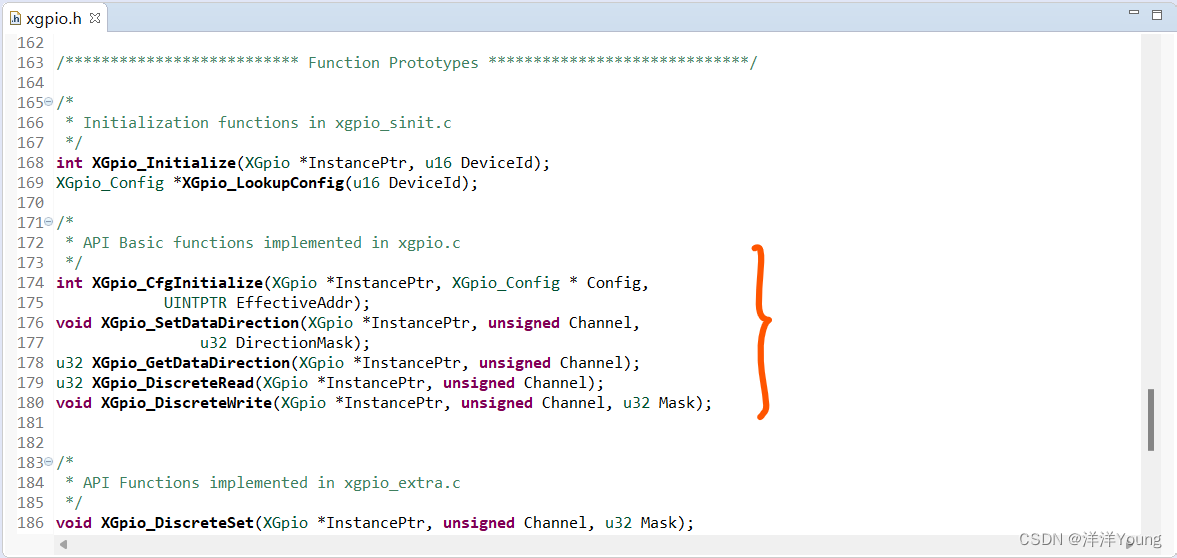

【ZYNQ】GPIO 与 AXI GPIO

在嵌入式开发中,GPIO 是最常见的外设。GPIO 是 General Purpose I/O 的缩写,译为通用输入/输出。GPIO 用于连接外部设备,例如按键、传感器等,实现数字信号的输入或输出功能。本文主要介绍 Zynq GPIO 的基本概念,并对比 GPIO 与 AXI GPIO 的使用方法。 GPIO Zynq GPIO 被称为 MIO,是 Multiplex

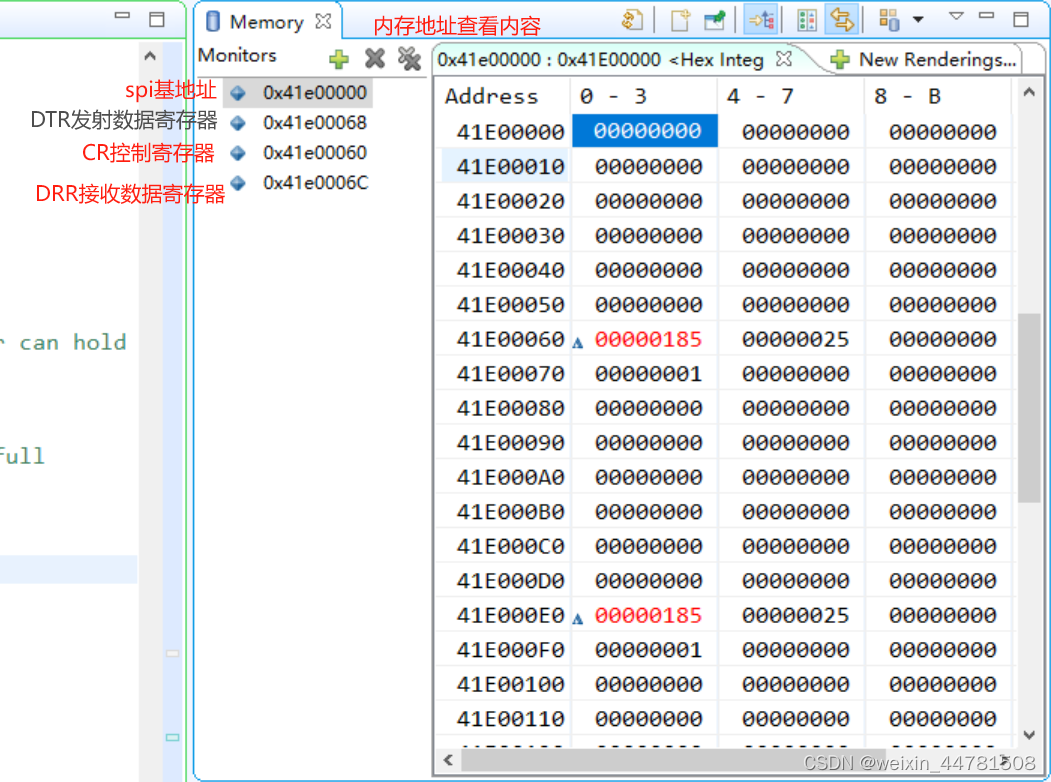

【ZYNQ】AXI-Quad-SPI SDK 开发记录 测试

前人工作 如前人工作,在Navigate to BSP Settings中找到历例程 file:///F:/Xilinx/Vitis/2019.2/data/embeddedsw/XilinxProcessorIPLib/drivers/spi_v4_5/doc/html/api/example.html 使用XSpi_LowLevelExample例子,源代码的AI解析 int

ZYNQ HLS 高层综合xilinx soc fpga

https://blog.csdn.net/cjx_csdn/article/details/101634273 一、引言 ZYNQ 是来自 Xilinx 公司 ZYNQ-7000 所有可编程片上系统的开发板,具有开发片上系统能力。 在 ZYNQ 上,ARM Cortex-A9 是一个应用级的处理器,能运行完整的像 Linux 这样的操作系统,而可编程逻辑是基于 Xilinx 7 系列的 FP

Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)-overlay设计

目录 1. 简介 2. Overlay 设计 2.1 总体设计 2.2 MIPI 子系统 2.3 去马赛克 2.4 AXI_IIC 3. 注意事项 4. 总结 1. 简介 本文是关于《Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)-CSDN博客》的博客文章,涉及了overlay设计的Vivado工程细节。在使用PYNQ调试MIPI驱动之前,需要搭建

Zynq开发-使用PYNQ快速入门摄像头MIPI驱动(OV5640)

目录 1. 简介 2. 配置代码 2.1 初始化寄存器 2.2 分辨率寄存器 2.3 白平衡寄存器 2.4 配置寄存器代码 2.5 顶层代码 3. 细节指引 4. 总结 1. 简介 PYNQ是一种基于Python的开发环境,专门设计用于快速、简便地在Xilinx的Zynq平台上进行开发。在《Zynq开发之-PYNQ配置,XVC(Xilinx Virtual Cable

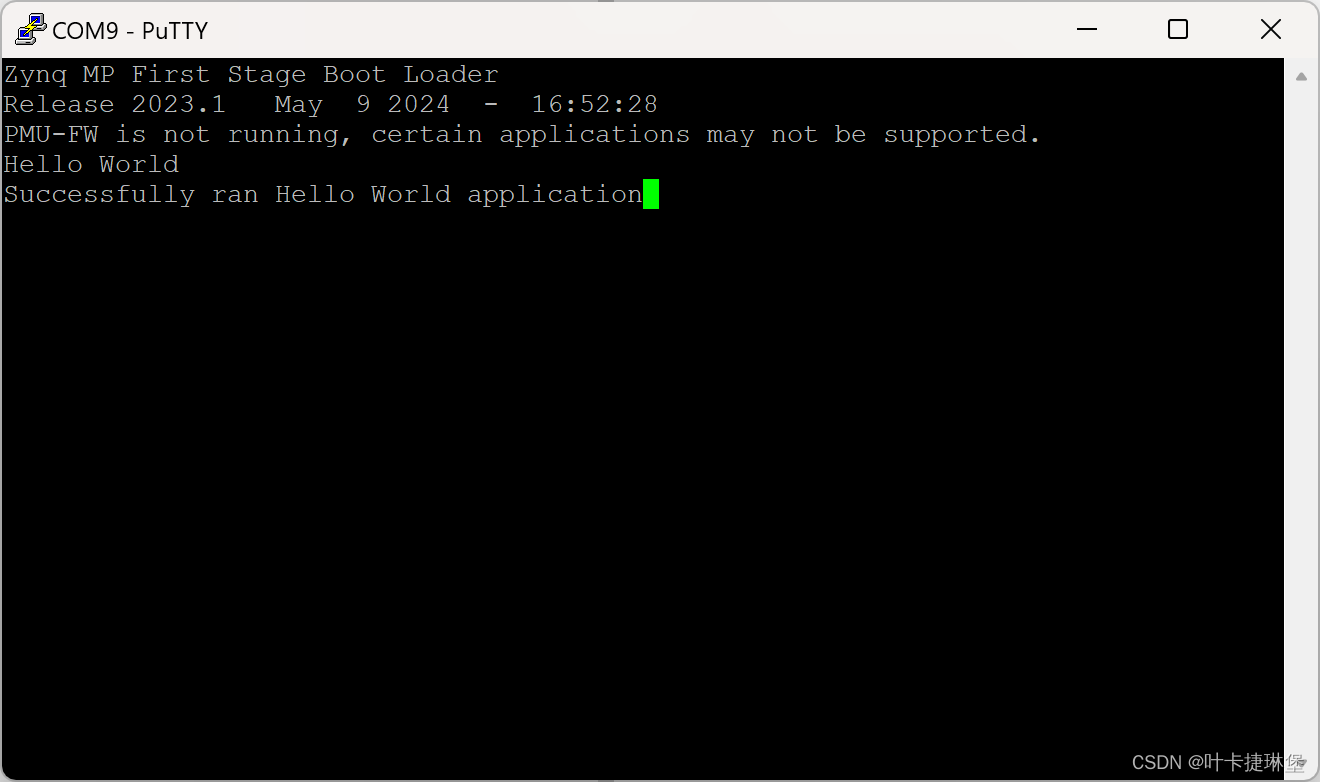

ZYNQ MPSoC zcu102 PS端运行helloworld

文章目录 一、参考资料二、需要注意的步骤三、运行结果 一、参考资料 1.zcu102 zynq Mpsoc uart hello world——CSDN博客 2.zcu102自学 —— 第一个实验 (纯PS 串口打印 Hello world)——CSDN博客 3.【02】ALINX Zynq MPSoC XILINX FPGA视频教程 SDK 裸机开发—MPSoC开发之Viva

产品推荐 | 基于 Zynq UltraScale+ RFSoC 的iW-RainboW-G42M 核心板

01 产品概述 Xilinx Zynq UltraScale+基于RFSoC的系统模块采用带有FFVF1760封装的Zynq Scale+RFSoC ZU49/ZU39/ZU29设备。RFSoC支持高达1.3GHz的Quad Cortex A53和高达533MHz的Dual Cortex R5F。SOM支持高达16通道的射频ADC@2.5Gsps和16通道的RF DAC@10Gsps,所有这些都