本文主要是介绍ZYNQ HLS 高层综合xilinx soc fpga,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

https://blog.csdn.net/cjx_csdn/article/details/101634273

一、引言

ZYNQ 是来自 Xilinx 公司 ZYNQ-7000 所有可编程片上系统的开发板,具有开发片上系统能力。

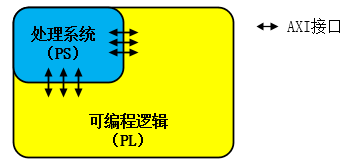

在 ZYNQ 上,ARM Cortex-A9 是一个应用级的处理器,能运行完整的像 Linux 这样的操作系统,而可编程逻辑是基于 Xilinx 7 系列的 FPGA ,两部分之间采用标准 AXI 接口实现了高带宽、低延迟连接。

二、ZYNQ与片上系统(SOC)

对于片上系统,我们比较熟悉的是:基于ASIC的片上系统,举例来讲PC、平板以及智能手机等都属于此类片上系统,其缺点主要是缺乏灵活性,升级能力差。因此,催生了一种可编程,硬件可重新配置的Soc。而FPGA恰好可以弥补这一缺点,可以被配置来实现任何芯片,甚至可以实现嵌入式处理器。

ZYNQ就是这样一种基于FPGA的Soc,主要包含两部分:PS(Processing System)部分是由双核ARM Cortex-A9构成的处理系统,PL(Programmable Logic)部分等价于一片FPGA可编程逻辑;另外集成了存储器,一些外设和高速通信接口。

PL部分主要用来实现高速逻辑、简单算术和数据流处理,PS部分支持软件设计或者操作系统。对于任意算法都可以在PL和PS部分恰当划分,通过软硬件协同设计思想在ZYNQ平台实现。PL和PS部分的连接是采用高级可扩展接口(Advanced eXtensible Interface,AXI)。处理器即 ARM Cortex-A9 作为 ZYNQ 的中央单元,运行软件系统,外设是除处理系统之外的部件,其功能为:1.协处理器---辅助主处理器,被优化用于特定任务或算法加速;2.与外部接口交互;3.存储器资源。

三、ZYNQ模块化设计

在ZYNQ上进行嵌入式系统开发除了具有灵活性高这一优势外,还具有可设计重用优势。IP(Intellectual Property)核,即知识产权模块,就是属于上面讲的外设部分,可以从Xilinx的设计工具中直接调用,也可以从其他项目中重用,或者从第三方开源库获得,然后将所有模块集成起来进行系统设计。ZYNQ就具有大量标准IP,因此开发时,这些IP部件无需我们再次设计,而是直接引用,从而加速开发,降低成本。

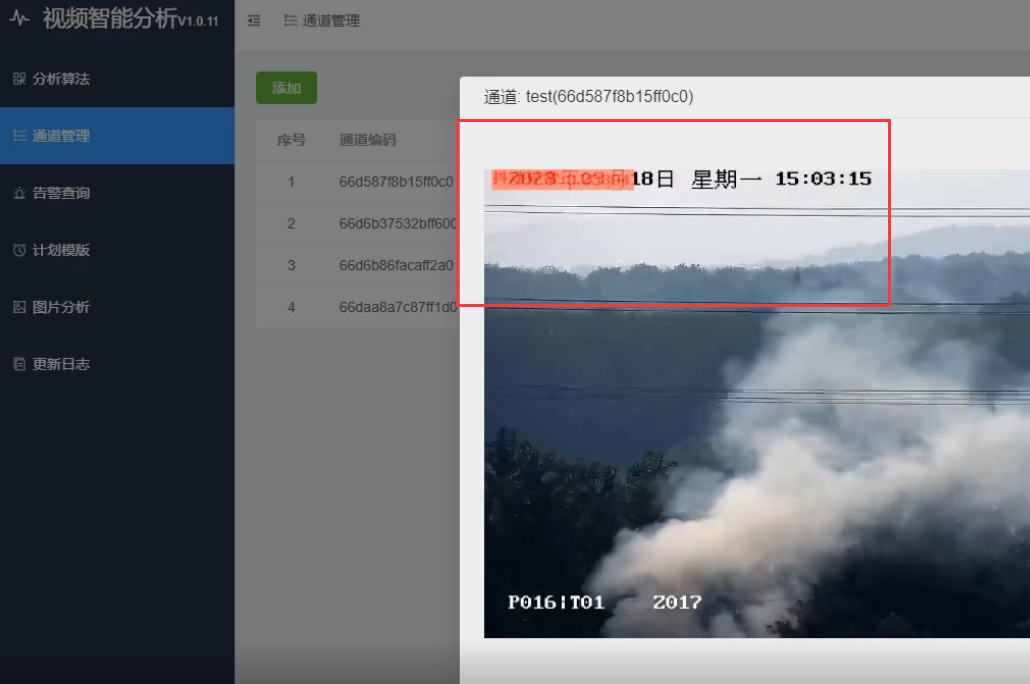

如果ZYNQ标准库中没有的IP,我们也可以自己封装,接口采用AXI协议。在这儿就不得不提到高层次综合工具(High Level Synthesis),可以用比传统的寄存器传输级 (Register Transfer Level,RTL)方式 更少的细节来创建系统部件,进一步提高了我们对ZYNQ的开发效率。不过,采用HLS工具封装的IP一般为AXI接口,灵活性差是一大缺点,当然采用该开发工具的缺点还有很多,但我关注的是采用 HLS 可以让我们快速的将算法布置在FPGA端,尤其是针对一些复杂的算法,如果采用RTL级逻辑代码设计,难度较大,需要设计人员具备丰富的开发经验。随着算法功能变得愈发复杂,开发周期也愈发漫长。设计人员现在往往需要在给定项目中实现数十万行 HDL 代码,逐次综合,仿真每个模块,以确保设计实现细节正确,把大部分时间花在细节的实现工作上,而不是设计更具价值的算法。高层次综合 HLS 是一种全新的逻辑设计思想,可直接从算法级对硬件电路进行描述,设计者可在更高层次上进行设计,仿真和验证,不用过多关心具体的电路设计,因此可以将更多精力放在设计结构的优化上,将数字系统设计从繁琐的底层硬件系统构建和设计中解放出来,把更多精力放在寻求最佳的设计方案上。

原文链接:https://blog.csdn.net/cjx_csdn/article/details/101634273

这篇关于ZYNQ HLS 高层综合xilinx soc fpga的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!