axi4专题

XDMA - AXI4 Memory Mapped

目录 1. What is SG DMA2. Descriptor3. Transfer for H2CStep 1. The host prepares stored data and creates descriptors in main memoryStep 2. The host enables DMA interruptsStep 2. The driver initializes

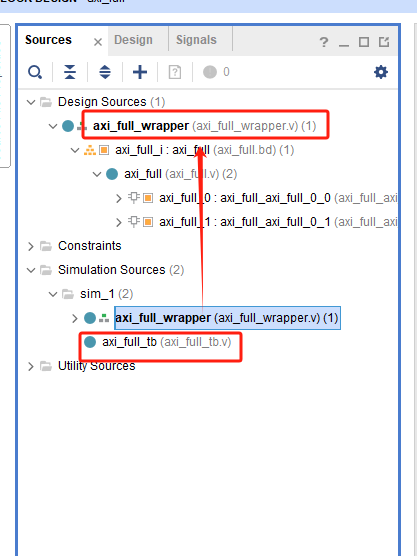

详解并掌握AXI4总线协议(四)、AXI4_FULL_SLAVE接口源码分析以及仿真验证

系列文章目录 详解并掌握AXI4总线协议(一)、AXI4-FULL接口介绍 详解并掌握AXI4总线协议(二)、AXI4_FULL_MASTER接口源码分析以及仿真验证 详解并掌握AXI4总线协议(三)、基于AXI4_FULL接口的BRAM读写仿真验证 文章目录 系列文章目录一、前言二、生成axi4_full_slave接口模板三、分析axi4_full_slave接口代码3.1 输入输出

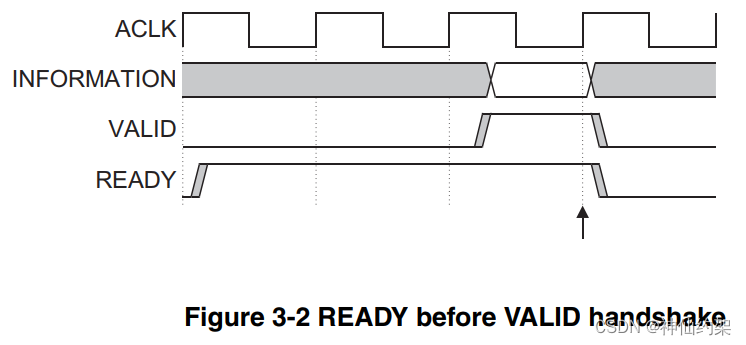

【总线】AXI4第三课时:握手机制

大家好,欢迎来到今天的总线学习时间!如果你对电子设计、特别是FPGA和SoC设计感兴趣,那你绝对不能错过我们今天的主角——AXI4总线。作为ARM公司AMBA总线家族中的佼佼者,AXI4以其高性能和高度可扩展性,成为了现代电子系统中不可或缺的通信桥梁。 上一课时我们了解到AXI4的AXI的基础事务,对他们有了初步的认识,这一课时我们来聊一聊AXI4总线中的“社

AXI Quad SPI IP核AXI4-Lite接口的部分操作指南

1 AXI4-Lite接口标准SPI模式——传统模式下可选FIFO的使用 当AXI Quad SPI IP核配置为标准SPI模式时,可以选择在设计中包含16或256深度的可选FIFOs。由于AXI Quad SPI是全双工的,所以发送和接收FIFOs都作为一对被实例化,并且可以包含在IP核中。 当实现FIFO时,要求所有的从选择地址都相同缓冲在FIFO中的数据。这是必要的,因为从机选择地址没有

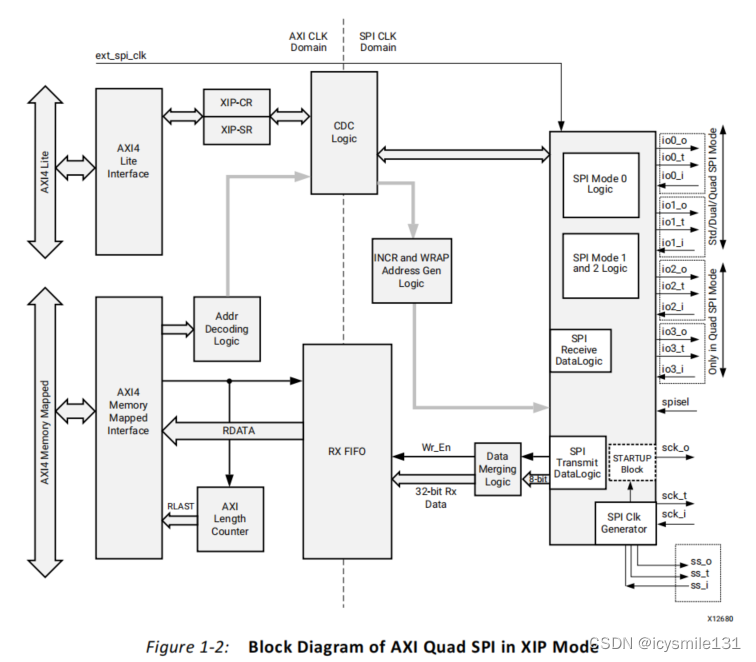

AXI Quad SPI IP核AXI4接口下的三种操作模式

当选择Enable Performance Mode选项时,AXI4接口包括在内。在该模式下,IP核可以在增强模式下操作(未选择启用XIP模式)或XIP模式(选择启用XIP模式)。在性能模式下,AXI4接口用于在DTR和DRR位置的突发事务。 1 增强模式 在这种模式下,原先用于IP核的AXI4-Lite接口被AXI4接口所取代。AXI4接口支持更复杂的数据传输方式,包括突发传输。根据“Mod

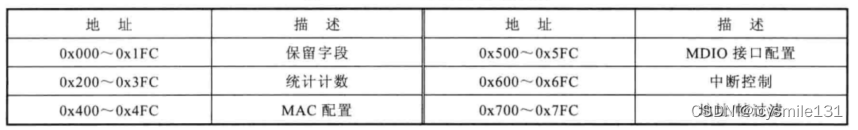

Xilinx 千兆以太网TEMAC IP核 AXI4-Lite接口信号

在AX4总线标准中,AXI4-Lite主要由向她址映射型通信。TEMAC的管理法口采用AXI4-Lite标准接口,TEMAC核的AX14-Lite接口信号如表1所示,根据AX14-Lite标准,接口角色分为主接口(Maser Interface)和从接口(Slave Interface)。主接口为通节发起方,这里指的是用户端控制的AX14-Lite接口;从接口为通信接收方,这里指的是MAC核内部的

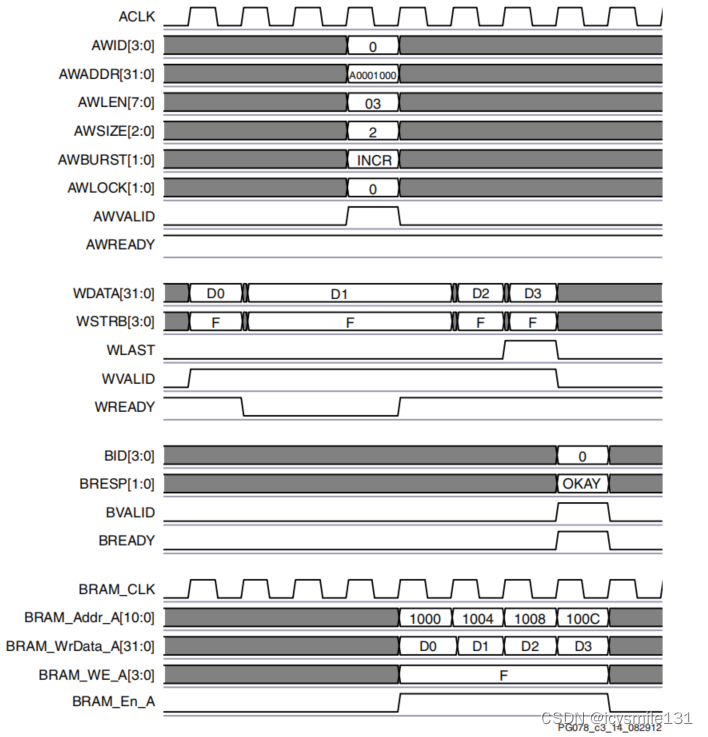

AXI4写时序在AXI Block RAM (BRAM) IP核中的应用

在本文中将展示描述了AXI从设备(slave)AXI BRAM Controller IP核与Xilinx AXI Interconnect之间的写时序关系。 1 Single Write 图1是一个关于32位宽度的BRAM(Block RAM)的单次写入操作的例子。这个例子展示了如何向地址0x1000h的BRAM写入数据,其中C_S_AXI_BASEADDR被设置为0xA000 0000,并

Vitis HLS 学习笔记--AXI4 主接口

目录 1. 简介 2. 认识MAXI 3. MAXI突发操作 3.1 全局/本地存储器 3.2 MAXI优势与特点 3.3 查看MAXI报告 3.3.1 HW Interfaces 3.3.2 M_AXI Burst Information 3.4 MAXI 资源消耗 4. 理解 Volatile 4.1 标准C/C++中的 volatile 4.2 HLS 中的 vola

FPGA实现AXI4总线的读写_如何写axi4逻辑

FPGA实现AXI4总线的读写_如何写axi4逻辑 一、AXI4 接口描述 通道信号源信号描述全局信号aclk主机全局时钟aresetn主机全局复位,低有效写通道地址与控制信号通道M_AXI_WR_awid[3:0]主机写地址ID,用来标志一组写信号M_AXI_WR_awaddr[31:0]主机写地址,给出一次写突发传输的写地址M_AXI_WR_awlen[7:0]主机突发长度,给出突发传输的

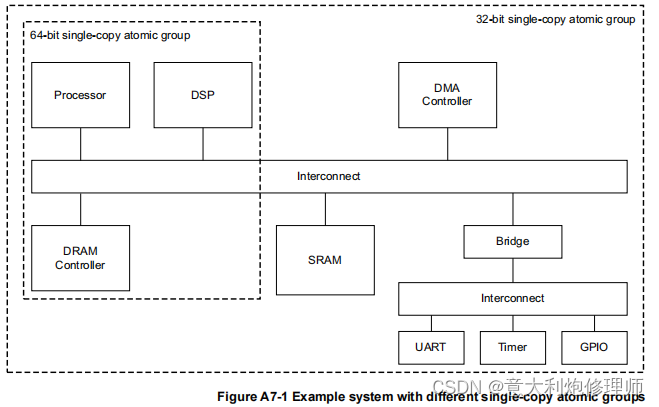

AXI4---原子访问

先理解一下什么是Single-copy atomicity size: "Single-copy atomicity size"(单副本原子性大小)是一个概念,它定义了事务必须原子性地更新的最小数据块的大小,以字节为单位。原子性意味着在事务执行期间,数据的任何更改要么全部完成,要么完全不做,从而保证了数据的一致性和完整性。 这里的“单副本”指的是在一次事务中,数据的更新操作是作为一个整体进行的

Zedboard 如何从PL端控制DDR3(二)--AXI4总线

虽然Xilinx已经将和AXI时序有关的细节都封装起来,给出了官方IP和向导生成自定义IP,用户只需要关注自己的逻辑实现,但是还是有必要简单了解一下AXI的时序,毕竟咱是做硬件设计的。 AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3

AXI4-Stream Interconnect模块的使用

显示AXI4-Stream互连核心框图。 在AXI4-Stream互连中,AXI4-Stream交换机核心路由从接口(SI)和主接口(MI)之间的通信。 在连接SI或MI到交换机的每一条路径上,一个可选的AXI4-Stream基础设施核心(耦合器)系列可以执行各种转换和缓冲功能。 两个耦合器包括:AXI4-流寄存器切片、AXI4-流数据FIFO、AXI4-流时钟转换器、AXI4-流数据宽度转换器

AXI4与AXI3的主要区别

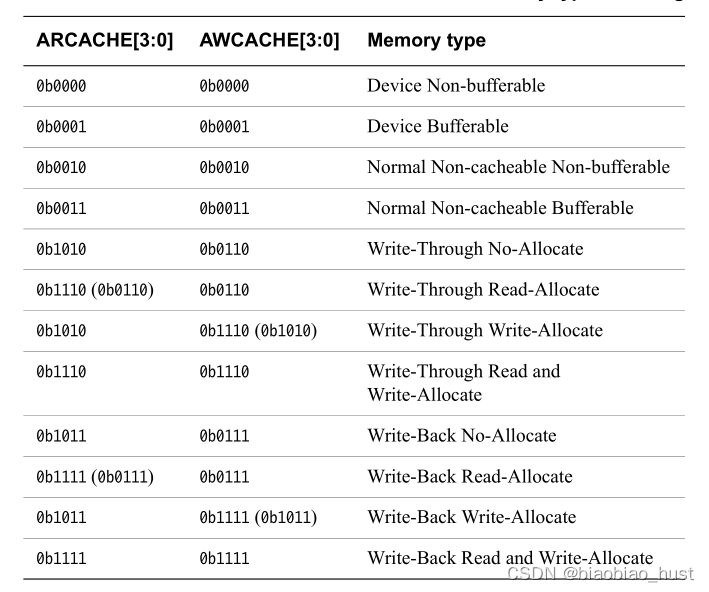

1. 前言 在SOC各种总线中,AXI是最重要的总线,没有之一。不管是在工作中,还是在面试中,AXI协议是一个必须精通的知识点。ARM 从AMBA1到AMBA5一共五代的AMBA总线中,AXI有两代,分别是AMBA3 的AXI3和AMBA4的AXI4。可能很多刚入门的工程师即使把协议读了很多次,还是不能深入理解。这是因为,ARM 没有告诉你,需要你去了解CPU架构,了解cache

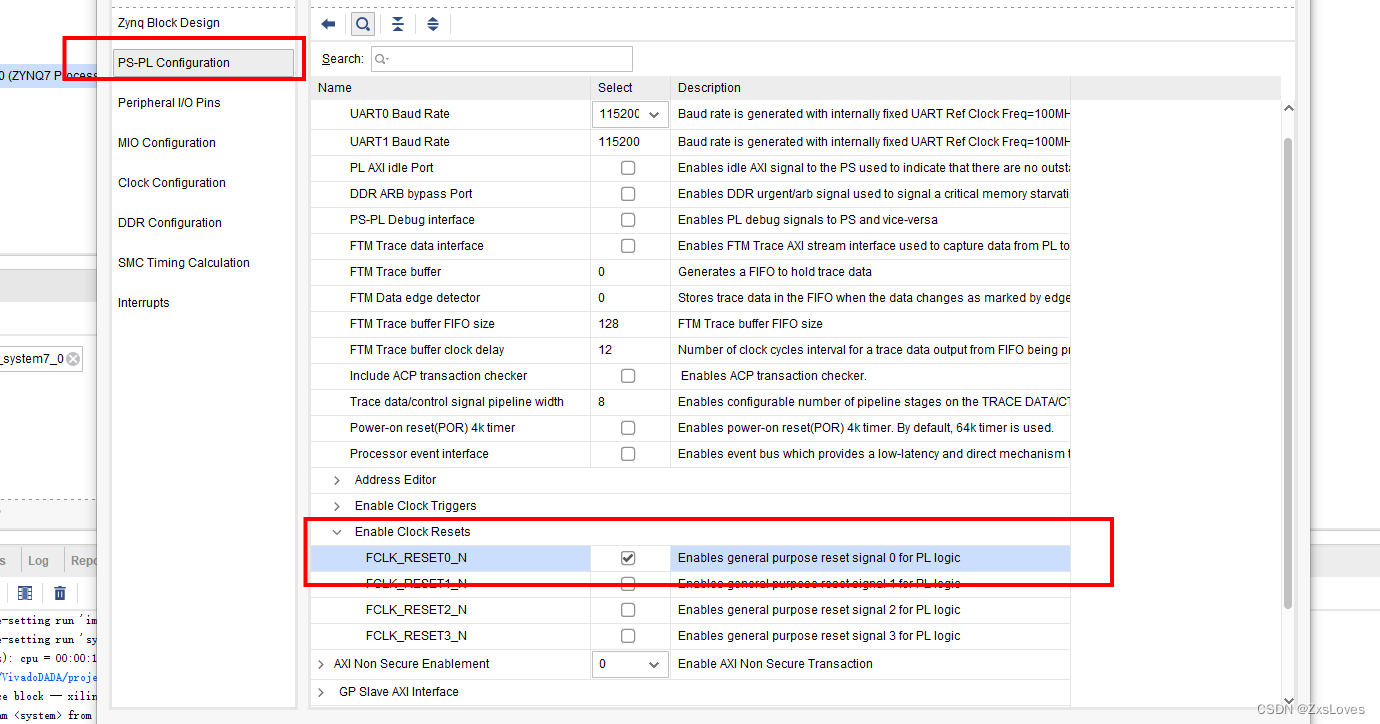

AXI4的网格设计Block Design

一、引出时钟和时钟复位 然后同样的把主接口和从接口的两个时钟和两个reset信号连接在一起。 二、分配地址 三、验证设计 点击图中的Validate Design验证设计,如果不对的话会有报错 报错如下 四、Generate Output Product和Creat HDL Wrapper 4.1 Generate Output Product(产生ver

Zynq-PS-SDK(11) 之 AXI4-Stream To Video Out

目录 1、Architecture 2、Signals 3、Timings 4、General Design Guidelines 1、Architecture 前面介绍了《Zynq-PS-SDK(9) 之 VDMA》和《Zynq-PS-SDK(10) 之 VTC》,数据流和时序流;从 VDMA 出来的是 AXI-Stream 流式数据,从 VTC 出来的是像素时钟得到的 Hsyn

FPGA----UltraScale+系列的PS侧与PL侧通过AXI-HP交互(全网唯一最详)附带AXI4协议校验IP使用方法

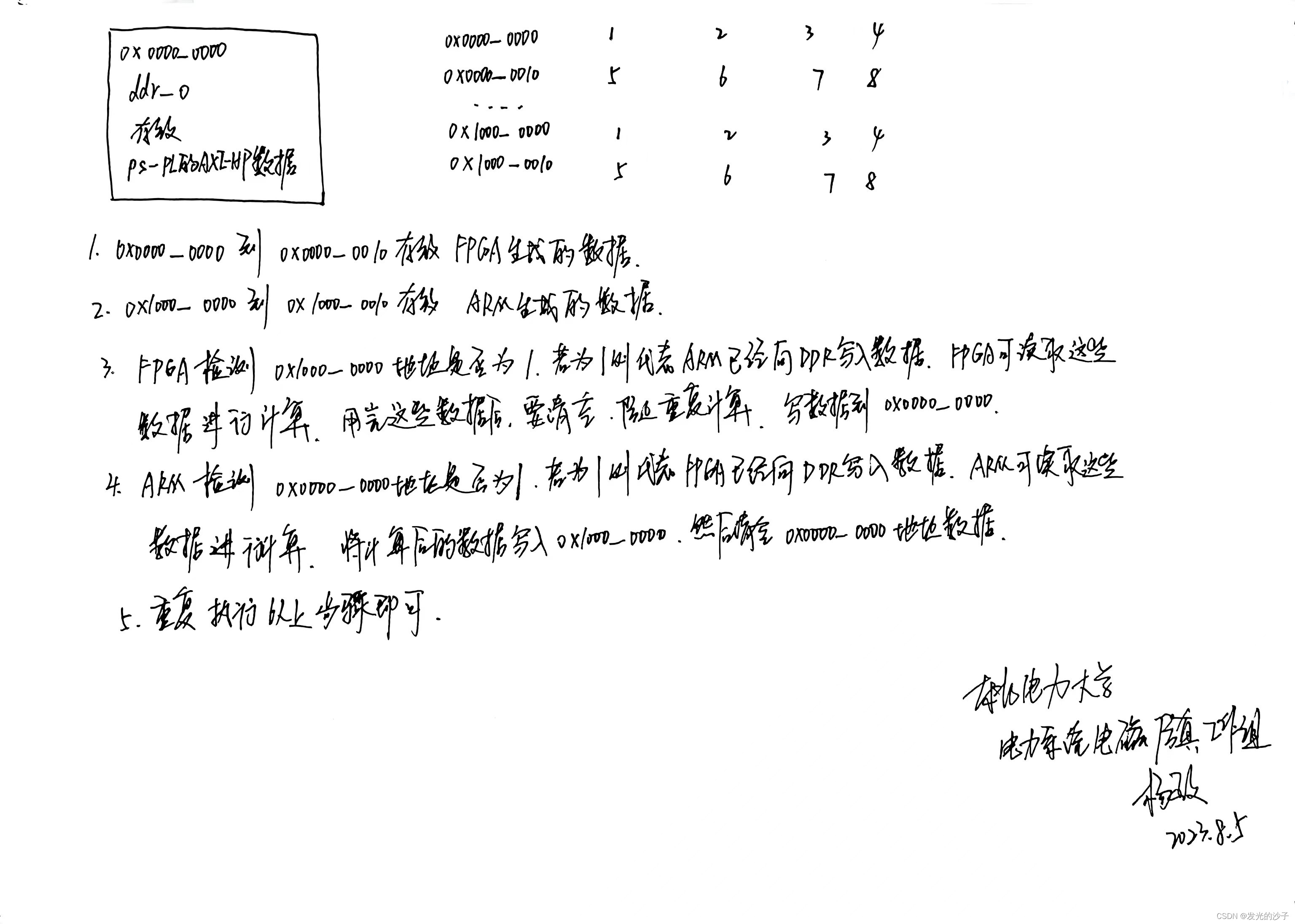

1、之前写过一篇关于ZYNQ系列通用的PS侧与PL侧通过AXI-HP通道的文档,下面是链接。 FPGA----ZCU106基于axi-hp通道的pl与ps数据交互(全网唯一最详)_zcu106调试_发光的沙子的博客-CSDN博客大家好,今天给大家带来的内容是,基于AXI4协议的采用AXI-HP通道完成PL侧数据发送至PS侧(PS侧数据发送至PL侧并没有实现,但是保留了PL读取PS测数据的接口)本

紫光FPGA DDR3 IP使用和注意事项(axi4协议)

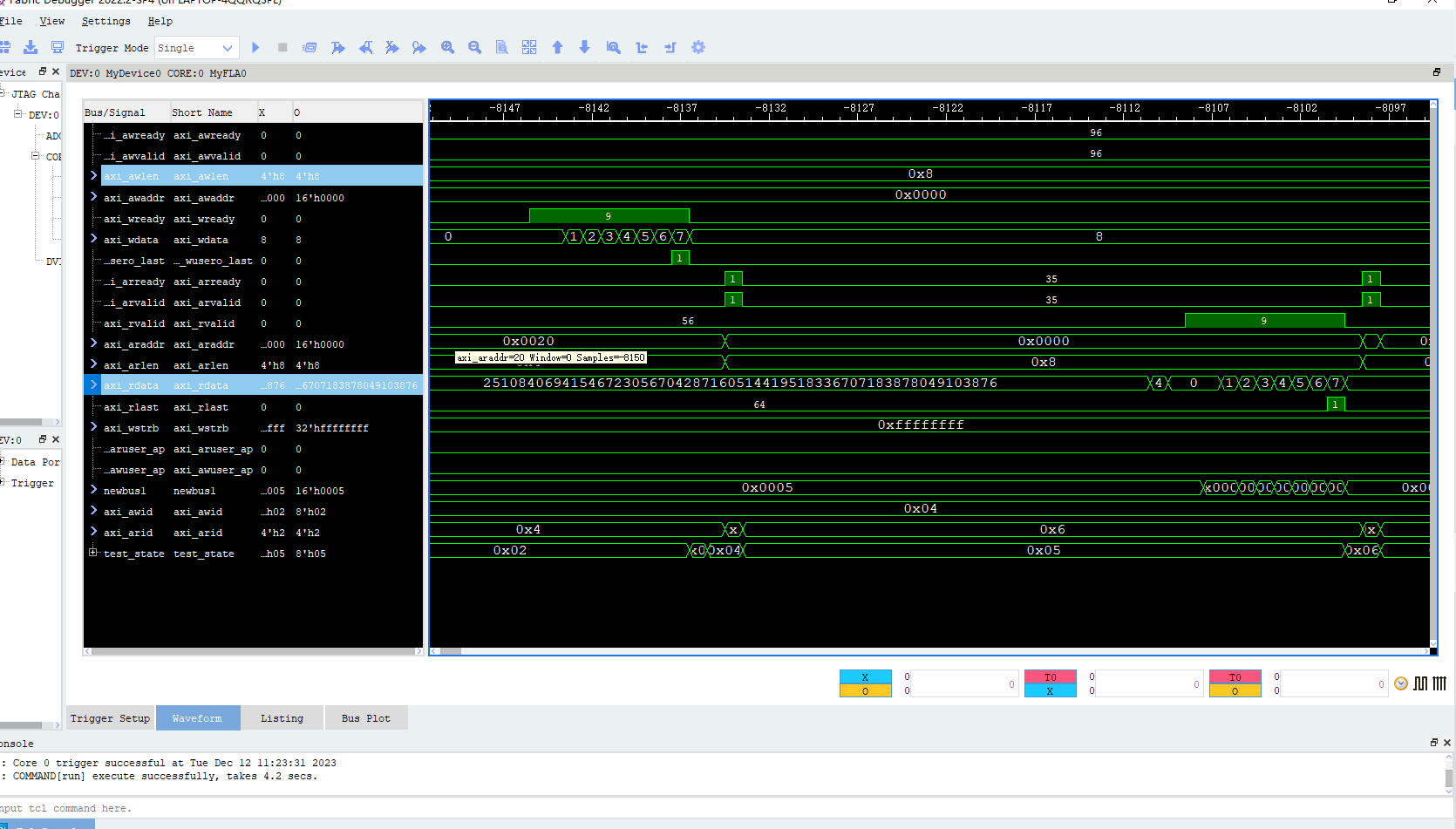

紫光DDR3 IP使用 对于紫光ddr3 IP核的使用需要注意事情。 阅读ddr ip手册: 1、注意:对于写地址通道,axi_awvalid要一直拉高,axi_awready才会拉高。使用的芯片型号时PG2L100H-6FBG676,不同的型号IP核接口和axi的握手协议也不一样(一定要注意),这点要注意,这也给我挖了一个很大的坑,一把心酸一把泪啊。下图是上板之后通过deb

紫光FPGA DDR3 IP使用和注意事项(axi4协议)

紫光DDR3 IP使用 对于紫光ddr3 IP核的使用需要注意事情。 阅读ddr ip手册: 1、注意:对于写地址通道,axi_awvalid要一直拉高,axi_awready才会拉高。使用的芯片型号时PG2L100H-6FBG676,不同的型号IP核接口和axi的握手协议也不一样(一定要注意),这点要注意,这也给我挖了一个很大的坑,一把心酸一把泪啊。下图是上板之后通过deb

【ZYNQ】AXI4总线接口协议学习

建议翻看着底部的参考文档资料和本文一起辅助阅读 本文带你详细的了解AXI总线协议,并且基于官方手册,能够提高你的手册阅读能力。 什么是AXI AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分 AMBA(

【【深入浅出了解AXI4协议 - 2】】

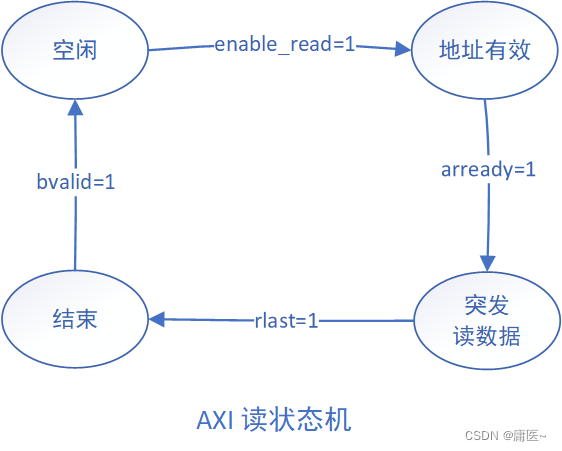

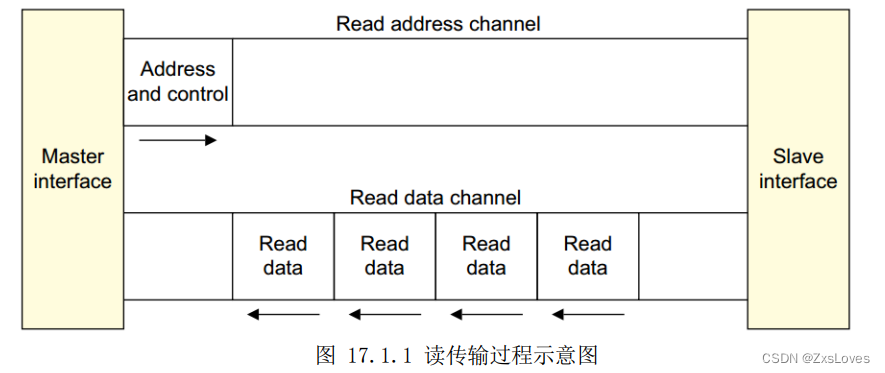

深入浅出了解AXI4协议 - 2 AXI总线共有五个通道 read address channel write address channel read data channel write data channel write response channel 信息源 通过VALID 信号 来指示 通道中的 数据和 控制信号 什么时候 有效 目的源 READY 表示何时接收数据 读数据 和

【【深入浅出了解AXI4协议 一】】

深入浅出了解AXI4协议 一 AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的 AMBA (Advanced Microcontroller Bus Architecture)协议的一部分。在介绍 AXI 协议之前,我们首先要对通信协 议有一个基本的概念。 AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特

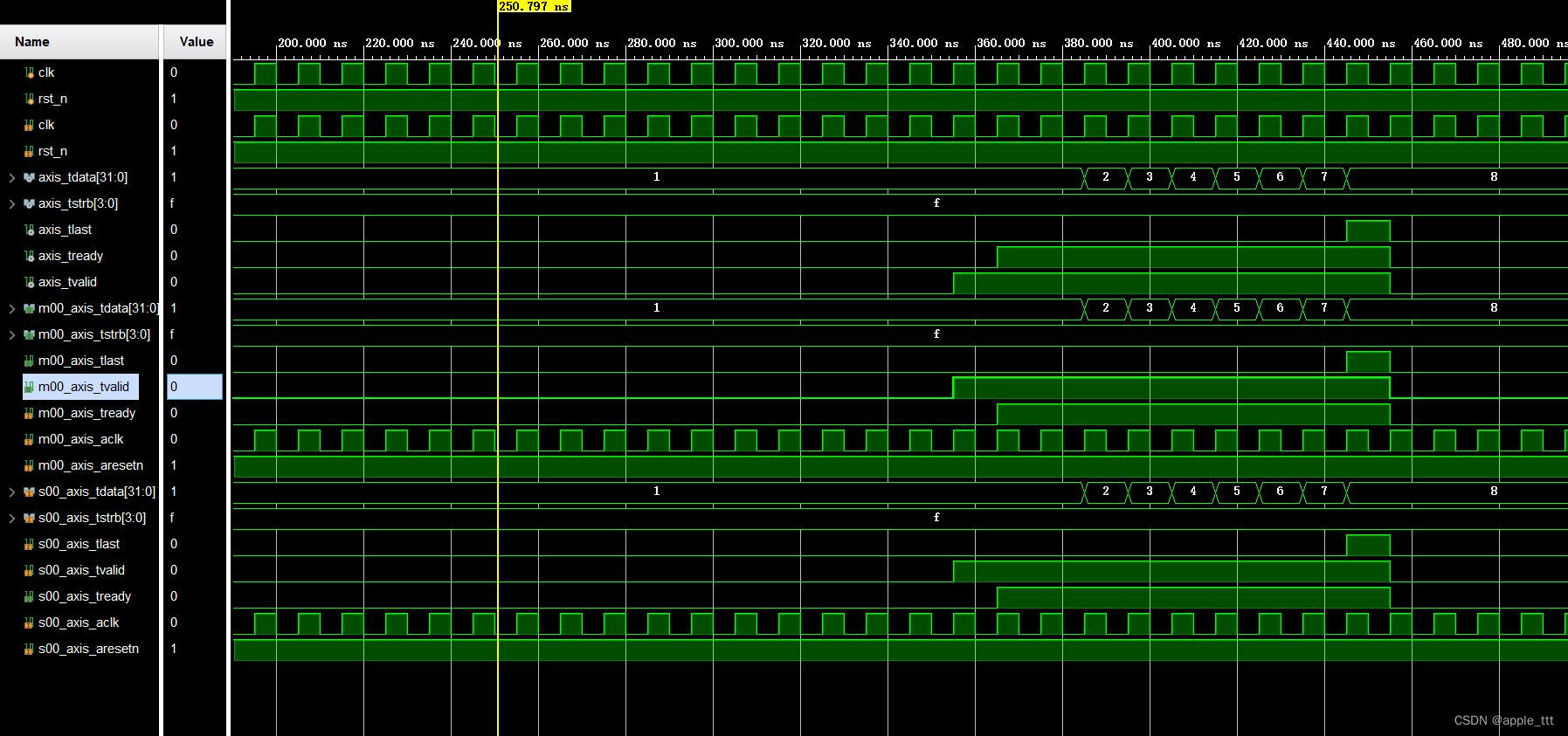

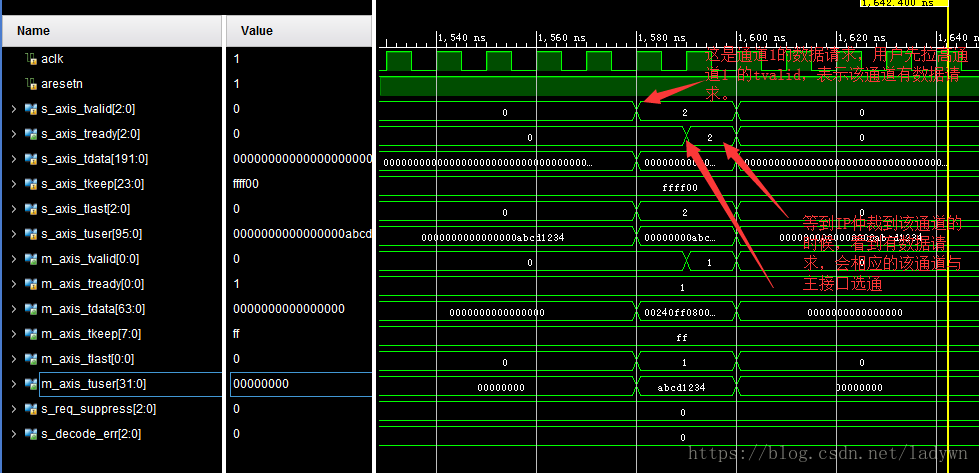

AXI-Stream协议详解(3)—— AXI4-Stream IP核原理分析

一、前言 在之前的文章中,我们介绍了AXI-S协议的一些基础知识,这是我们进行本文学习的前置基础,因此建议在开始本文章的学习前,完整阅读以下两篇文章: AXI-Stream协议详解(1)—— Introductionhttps://blog.csdn.net/apple_53311083/article/details/134058532?spm=1001.2014.3001.

AXI4-stream 协议学习-接口信号

2.1信号列表接口 信号如表2-1所示。有关这些信号的更多信息,请参阅本章的进一步章节。表2-1使用以下参数定义n 信号宽度:以字节为单位的数据总线宽度。 i TID宽度。建议最大长度为8位。 d dtd宽度。建议最大长度为4位。 u TUSER 宽度。推荐位数是接口宽度的整数倍,单位是字节。 2.2传输信号 这一节给出了握手信号的详细信息,并定义了TVALID和TREADY握手信

【【萌新的SOC学习之自定义IP核 AXI4接口】】

萌新的SOC学习之自定义IP核 AXI4接口 自定义IP核-AXI4接口 AXI接口时序 对于一个读数据信号 AXI突发读 不要忘记 最后还有拉高RLAST 表示信号的中止 实验任务 : 通过自定义一个AXI4接口的IP核 ,通过AXI_HP接口对PS端 DDR3 进行读写测试 。 S_AXI_HP0 是 PS 端的 AXI 高性能接口,它是一个从接口,连接到 PS 内的存储

与aurora 64B66B 发送端 AXI4-Stream接口 相连的FIFO设置

目录 1 背景1.1 关于Aurora 64b66b IP核1.2 关于FIFO的读操作模式1.3 遇到的问题 2 与Aurora 64b66b IP核AXI4-S发送接口相连的FIFO的设计 1 背景 1.1 关于Aurora 64b66b IP核 在【PG074】1 简略学习Aurora 64B/66B IP核中2.3.3 Streaming接口章节学习了Aurora 64

AXI4 Stream Switch使用心得

关于这个ip的内容讲解,在 https://blog.csdn.net/xdczj/article/details/72058100 上面已经讲解的比较详细了,刚接触这个ip可以先看一下,这个博客是关于我使用这个ip的一些小注意事项。 第一点是IP的生成,官方的IP显示应该是有BUG,我的使用需求是3从1主做仲裁,然后在IP显示图中显示了三组AXIs从接口,但是每个从接口是主接口的位