本文主要是介绍AXI4-Stream Interconnect模块的使用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

显示AXI4-Stream互连核心框图。 在AXI4-Stream互连中,AXI4-Stream交换机核心路由从接口(SI)和主接口(MI)之间的通信。 在连接SI或MI到交换机的每一条路径上,一个可选的AXI4-Stream基础设施核心(耦合器)系列可以执行各种转换和缓冲功能。 两个耦合器包括:AXI4-流寄存器切片、AXI4-流数据FIFO、AXI4-流时钟转换器、AXI4-流数据宽度转换器和AXI4-流协议转换器。

可以将AXI4-Stream互连核心配置为多达16个从接口(SI)和多达16个主接口(MI)。 每个SI连接到一个AXI4-Stream主设备并接受transfe来自连接的主设备的RS。 每个MI连接到一个AXI4-Stream从设备,并发出传输到从设备。 在中心是开关核心,路由之间的SI和MI传输。 在SI和开关之间的每条通路上,或者在开关和MI之间,可以有一个或多个AXI4-Stream基础设施核心来执行各种转换和存储功能。

该开关有效地将AXI4-Stream互连核心从SI相关功能单元(SI半球)和MI相关单元(MI半球)之间的中间分割开来)。 可能的话,ADO系统设计工具自动将耦合器插入SI或MI半球,以解决连接的主从设备的配置差异。

为AXI4-Stream互连生成一个项目

AXI4-Stream互连v2.1需要IP积分器。 要访问IP,首先创建Vivado项目,然后从Vivado流导航器中选择CreateBlockDesign。 在块设计画布中,从工具栏中选择AddIP选项,并从IP积分器IP目录窗口中选择AXI4-Stream互连。 在块设计画布中添加了一个AXI4-Stream互连IP实例。 单击图中的IP实例将打开其自定义窗口。

Toplevel Settings

Number of Slave Interfaces

此参数指定IP上存在的AXI4-Stream从接口的数量。 值可以在1到16之间。

Number of Master Interfaces

此参数指定IP上存在的AXI4-Stream主接口的数量。 值可以在1到16之间。

Enable ACLKEN

如果设置为“是”,则此参数指定所有AXI4-Stream接口时钟是否存在可选的ACLKEN信号。

Use Control Register Routing

使用控制寄存器路由

此参数指定路由模式。 控制寄存器路由使AXI4-Lite控制寄存器接口能够处理传输路由。 如果此选项设置为No,则内联TDEST值用于路由。

Data Flow Properties

数据流属性

只有当从接口的数量大于1时,数据流属性选项修改。

Arbitrate on Maximum Number of Transfers

最高转让次数仲裁

此设置指定在放弃授予的仲裁之前要计算多少传输,并直接传递到AXI4-Stream互连实例中的AXI4-Stream交换机。 领事有关有效值范围和此参数的使用的更多详细信息,请参阅AXI4-StreamSwitch参数描述。

Arbitrate on Number of LOW TVALID Cycles

对LOW TVALID周期数进行仲裁

此设置允许在没有传输的情况下放弃授予的仲裁,并直接传递到AXI4-Stream互连实例中的AXI4-Stream交换机。 请参阅AXI4-Stream有关有效值范围和此参数的使用的更多详细信息,请切换参数描述。

Arbitrate on TLAST Transfer

对TLAST传输进行仲裁

此设置允许在接收到具有TLAST断言的传输并直接传递到AXI4-Stream互连insta中的AXI4-Stream交换机时放弃授予的仲裁NCE。 有关此参数的有效值范围和使用的更多细节,请参阅AXI4-StreamSwitch参数描述。

Arbiter Algorithm

仲裁算法

此设置允许选择仲裁算法,并直接传递到AXI4-流互连实例中的AXI4_Stream开关。 请参阅AXI4-Stream开关参数有关有效值范围和此参数使用的更多详细信息的说明。

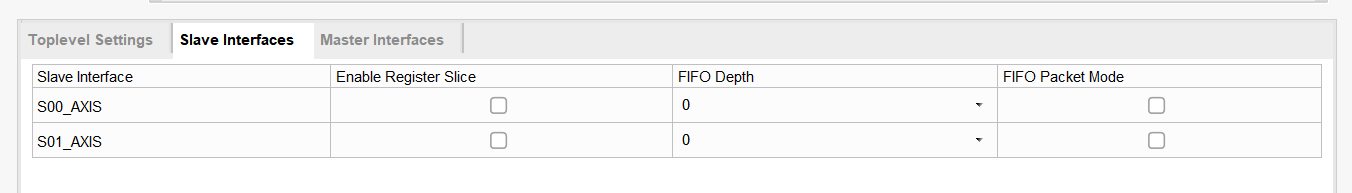

Enable Register Slice

启用寄存器切片

如果选中,则在Snn_AXIS接口和AXI4流开关之间的SI半球耦合器中插入AXI4流寄存器切片。

FIFO Depth

如果选择大于0的值,则在Snn_AXIS接口和AXI4流开关之间的SI半球耦合器中插入AXI4流数据FIFO。 FIFO的选定深度直接配置到AXI4-流数据FIFO实例中。

FIFO Packet Mode

FIFO分组模式

如果检查并选择大于0的FIFO深度进行Snn_AXIS,则启用AXI4流数据FIFO的分组模式。 有关Packet的更多细节,请参阅AXI4-Data FIFO参数描述分组模式操作。

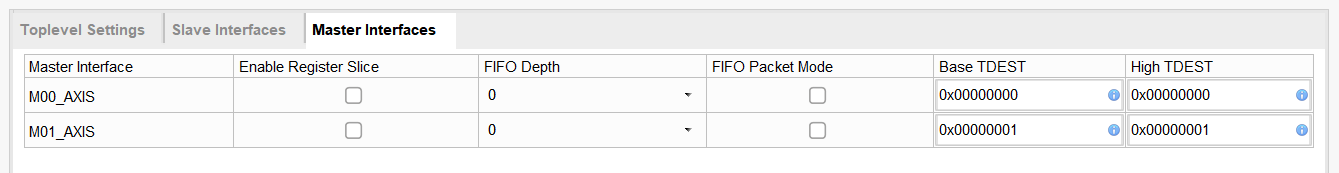

Enable Register Slice

如果选中,则在AXI4流开关和Mnn_AXIS接口之间的MI半球耦合器中插入AXI4流寄存器切片。

FIFO Depth

如果选择大于0的值,则在AXI4流开关和Mnn_AXIS接口之间的MI半球耦合器中插入AXI4流数据FIFO。 FIFO的选定深度直接配置到AXI4-流数据FIFO实例中。 有关FIFO深度的有效范围的更多细节,请参阅AXI4-流数据FIFO参数描述。

FIFO Packet Mode

如果检查并选择大于0的FIFO深度进行Snn_AXIS,则启用AXI4流数据FIFO的分组模式。 有关更多细节,请参阅AXI4-流数据FIFO参数描述在分组模式操作上。

Base TDEST and High TDEST

上图所示的路由参数设置了解码,根据TDEST信号将从接口传输到主接口,并直接传递给AXI4-StreamSwitchI在AXI4-Stream互连中的状态。 有关路由的有效范围和使用,请参阅AXI4-StreamSwitch参数描述。 当使用控制寄存器路由设置为“是”时,这些参数是不可配置的。

参考:pg085 AXI4-Stream Interconnect部分

仿真部分:

在AXI4_Stream_Interconnect中,AXI4-Stream交换机核心路由从接口和主接口之间通信。

首先,在IP Catalog里添加模块:

设置为2个Slave接口和2个Master接口,分别为S0,S1,M0,M1。其他设置保持不变。

设置为2个Slave接口和2个Master接口,分别为S0,S1,M0,M1。其他设置保持不变。

上图为S0,S1,M0, M1传输方式。可以在S接口与M接口之间相互传输。在S0==>M0, S1==>M1传输模式时,得到的仿真结果如下:

上图为S0,S1,M0, M1传输方式。可以在S接口与M接口之间相互传输。在S0==>M0, S1==>M1传输模式时,得到的仿真结果如下:

从仿真结果可以看出,ARESETN低位有效,在S_AXIS_ARESETN复位后的两个时钟周期后 S_TREADY拉高,同时M_AXIS_TVAILD拉高,S0==>M0,S1==>M1数据成功传输。

从仿真结果可以看出,ARESETN低位有效,在S_AXIS_ARESETN复位后的两个时钟周期后 S_TREADY拉高,同时M_AXIS_TVAILD拉高,S0==>M0,S1==>M1数据成功传输。

注意:TDEST是选择通道的信号,使用 TDEST信号确定要将每个传输发送到哪个Mxx_AXIS接口。所以转换接口传输(如S0==>M1,S1==>M0)的时候要改变对应的S_TDEST的值。

这是最基本的数据传输,我在学习这个模块的过程中还遇到过下面的问题,可以进行参考。不一定完全正确,欢迎大家指正!

Tips:

1.如果能够读取数据,但是数据不连续,去看teatbench里给数据的延迟问题,多给一个延迟周期。

2.若从coe里面读取数据,输出端M_DATA可以成功读取,但是缺少S_VAILD前面的部分,要去看S_TLAST信号是不是给的太早,适当延迟S_TLAST信号,就可以将S_DATA读取coe的数据延迟一段时间。

这篇关于AXI4-Stream Interconnect模块的使用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!