本文主要是介绍AXI Quad SPI IP核AXI4接口下的三种操作模式,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

当选择Enable Performance Mode选项时,AXI4接口包括在内。在该模式下,IP核可以在增强模式下操作(未选择启用XIP模式)或XIP模式(选择启用XIP模式)。在性能模式下,AXI4接口用于在DTR和DRR位置的突发事务。

1 增强模式

在这种模式下,原先用于IP核的AXI4-Lite接口被AXI4接口所取代。AXI4接口支持更复杂的数据传输方式,包括突发传输。根据“Mode”选项的设置,增强模式还支持标准、dual模式和quad模式。通过设置“Slave Device”选项为Mixed、Winbond、Micron、Macronix或Spansion,可以选择目标从设备内存。这提供了与不同类型存储设备的兼容性。

所有寄存器都映射到与AXI4-Lite接口相同的偏移量,这确保了从AXI4-Lite升级到AXI4接口时,原有的软件或固件代码不需要做太多修改。

AXI4接口只允许在数据发送寄存器(DTR)和数据接收寄存器(DRR)进行突发事务。其他所有寄存器应仅通过单次访问进行操作。这一点在设计IP核的应用程序时需要特别注意。

DTR和DRR的FIFO队列可以配置为16或256拍的深度。这提供了灵活的数据缓冲能力,以适应不同的数据传输需求。

该IP核支持与AXI4-Lite接口相同的功能。

增强模式的主要优势是在DTR和DRR位置具有突发能力。这减少了在AXI4接口侧从IP核读取和写入数据的开销,从而提高了整体的数据传输效率。

总的来说,增强模式通过引入更高效的AXI4接口和突发传输能力,显著提升了IP核的数据处理能力。这在需要高速、大量数据传输的应用场景中尤为有用。

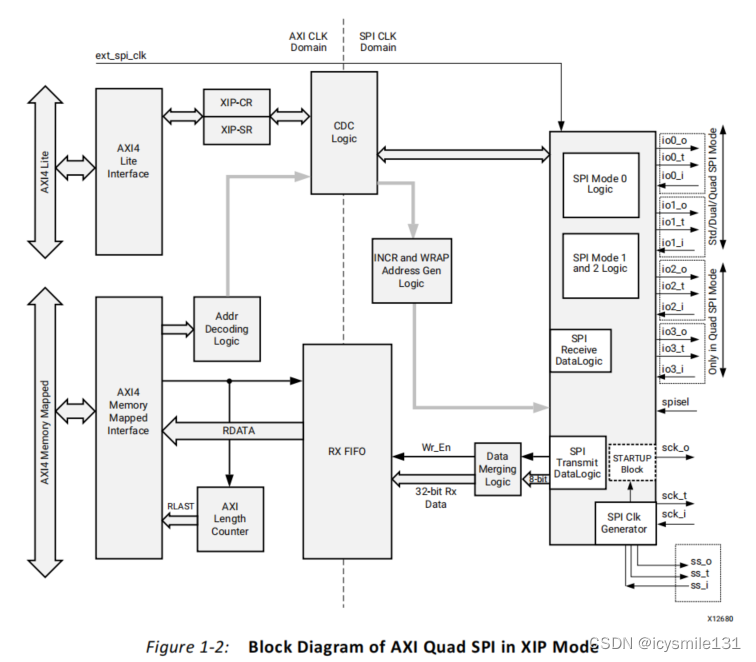

2 XIP模式

在XIP(Execute-In-Place)模式下,IP核同时配备了AXI4-Lite接口和AXI4接口,这两种接口在XIP模式下有特定的用途和功能限制。以下是关于XIP模式下这两种接口的具体说明:

- AXI4-Lite接口:

- 被用于访问配置寄存器和状态寄存器。

- 可以通过配置寄存器去更改时钟极性(CPOL)或时钟相位(CPHA)的配置。

- AXI4接口:

- 在XIP模式下仅用于读取操作,不支持写入交易。

- 支持读取通道,用于从SPI闪存中读取数据。

XIP模式下IP核支持以下两种操作模式:

- 高性能模式:

IP支持超过64拍事务,但要求读取数据始终准备好(read data ready should always high)。 适用于需要高数据吞吐量的应用场景。

- 正常模式:

IP支持最多64拍事务。

XIP模式适合引导操作(boot operation),因为IP核仅支持INCR和WRAP读取事务。

在XIP模式下,SPI闪存被视为只读存储器,并且IP核提供了三种主要的读取命令:快速读取(fast read,0x0Bh)、DIOFR(0xBBh)和QIOFR(0xEBh)。

在XIP模式下,为了确保IP核功能的正确性,AXI4-Lite接口和AXI4接口都被分配了相同的频率。

综上所述,XIP模式为嵌入式系统提供了一种高效的代码执行和数据读取方式,特别是在对性能和功耗有严格要求的场景中。通过AXI4-Lite接口和AXI4接口的配合,XIP模式确保了配置和状态监控的灵活性,同时优化了从SPI闪存中读取数据的性能。

3 Dual Quad SPI模式

Dual Quad SPI模式是一种特殊的SPI通信模式,在这种模式下,IP核具有两个SPI接口,这允许它同时与两个从设备进行通信,并且通过寄存器配置可以选择特定的从设备。此模式只能在支持UltraScale架构的设备上启用,且需满足特定条件:即SPI模式设置为Quad,启用STARTUP,并且从设备数量为2。

Dual Quad SPI模式相比传统的SPI模式具有更高的数据传输速率,因为它使用了更多的数据线(在Quad模式下,通常使用4条数据线,而不是传统的2条)。

通过同时与两个从设备通信,可以进一步增加数据吞吐量,适用于需要处理大量数据的应用场景。

总的来说,Dual Quad SPI模式是一种高性能的SPI通信模式,它通过提供两个SPI接口和更高的数据线数量,实现了更高效的数据传输和处理能力。然而,它也需要更复杂的硬件和软件支持,因此在实际应用中需要综合考虑性能和成本等因素。

这篇关于AXI Quad SPI IP核AXI4接口下的三种操作模式的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!