quad专题

科研绘图系列:R语言差异基因四分图(Quad plot)

介绍 四分图(Quad plot)是一种数据可视化技术,通常用于展示四个变量之间的关系。它由四个子图组成,每个子图都显示两个变量之间的关系。四分图的布局通常是2x2的网格,每个格子代表一个变量对的散点图。 在四分图中,通常: 第一个子图显示变量A和B的关系。第二个子图显示变量A和C的关系。第三个子图显示变量A和D的关系。第四个子图显示变量B和C的关系。 此外,第四个子图也可以显示变量

科研绘图系列:R语言单细胞差异基因四分图(Quad plot)

介绍 在单细胞分析领域,为了探究不同分组间同一细胞类型的基因表达差异,研究者们常采用四分图(Quad Plot)作为分析工具。该图形的横轴代表比较组1,而纵轴代表比较组2。通过这种布局,四分图能够有效地展示两组间共有的差异表达基因,从而为深入理解细胞类型在不同条件下的分子特性提供直观的视角。这种可视化方法不仅揭示了组间基因表达的异同,还有助于识别可能在生物学过程或疾病发生中起关键作用的基因。

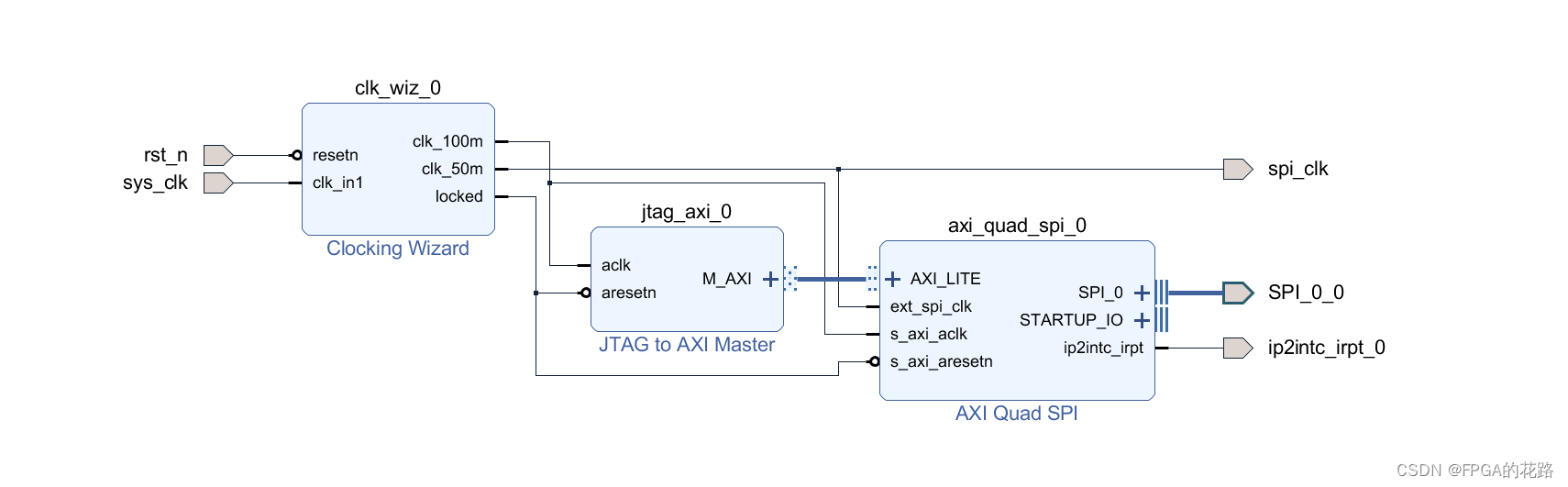

AXI Quad SPI IP核中的STARTUPEn原语参数

启动STARTUPEn Primitive (原语)参数在 FPGA的主 SPI模式下非常有用。当你启用这个参数时,对于 7 系列设备,STARTUPE2 原语会被包含在设计中;而对于 UltraScale™ 设备,则是 STARTUPE3 原语。这些原语在 FPGA 配置后成为IP核的一部分。 1 启用STARTUPEn 原语参数 STARTUPEn(如STARTUPE2或STARTUP

AXI Quad SPI IP核AXI4-Lite接口的部分操作指南

1 AXI4-Lite接口标准SPI模式——传统模式下可选FIFO的使用 当AXI Quad SPI IP核配置为标准SPI模式时,可以选择在设计中包含16或256深度的可选FIFOs。由于AXI Quad SPI是全双工的,所以发送和接收FIFOs都作为一对被实例化,并且可以包含在IP核中。 当实现FIFO时,要求所有的从选择地址都相同缓冲在FIFO中的数据。这是必要的,因为从机选择地址没有

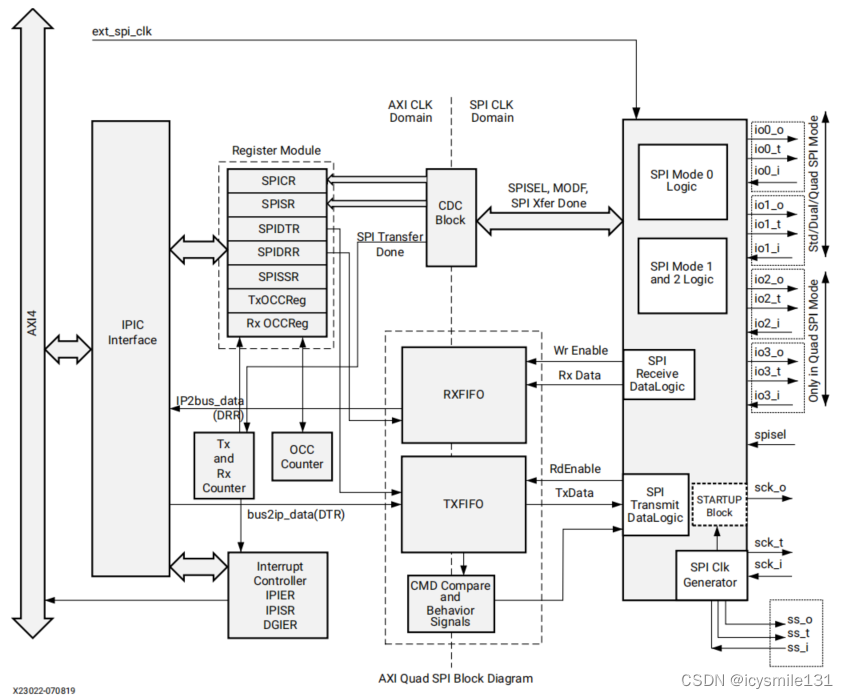

AXI Quad SPI IP核子模块

当选择Enable Performance Mode选项时,AXI Quad SPI IP核向后兼容所有早期版本的AXI Quad SPI IP核。该IP核包括以下子模块: AXI4-Lite 接口模块 AXI4-Lite接口模块为AXI4-Lite协议和IPIC提供接口。AXI4Lite接口上的读写事务被转换为等效的IP 互连(IPIC)事务。这是该IP核的默认组合。 SPI 寄存器模块

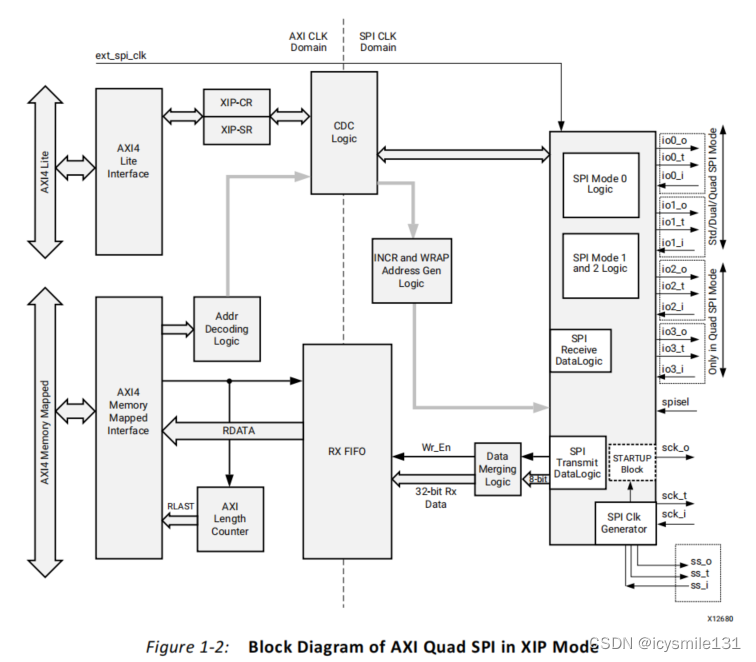

AXI Quad SPI IP核AXI4接口下的三种操作模式

当选择Enable Performance Mode选项时,AXI4接口包括在内。在该模式下,IP核可以在增强模式下操作(未选择启用XIP模式)或XIP模式(选择启用XIP模式)。在性能模式下,AXI4接口用于在DTR和DRR位置的突发事务。 1 增强模式 在这种模式下,原先用于IP核的AXI4-Lite接口被AXI4接口所取代。AXI4接口支持更复杂的数据传输方式,包括突发传输。根据“Mod

Blender + Marvelous Designer(MD)服装,Quad Remesher四边面拓扑布线、UV投射

Blender + Marvelous Designer(MD)服装,Quad Remesher四边面拓扑布线、UV投射_哔哩哔哩_bilibili Blender+MD服装,Quad Remesher四边面拓扑和UV投射 - 哔哩哔哩 https://i0.hdslb.com/bfs/article/b3f270cb02bb6de5cc080d732dc8283850669770.png

Quad Tiling

Description Tired of the Tri Tiling game finally, Michael turns to a more challengeable game, Quad Tiling: In how many ways can you tile a 4 × N (1 ≤ N ≤ 109) rectangle with 2 × 1 dominoes? For the

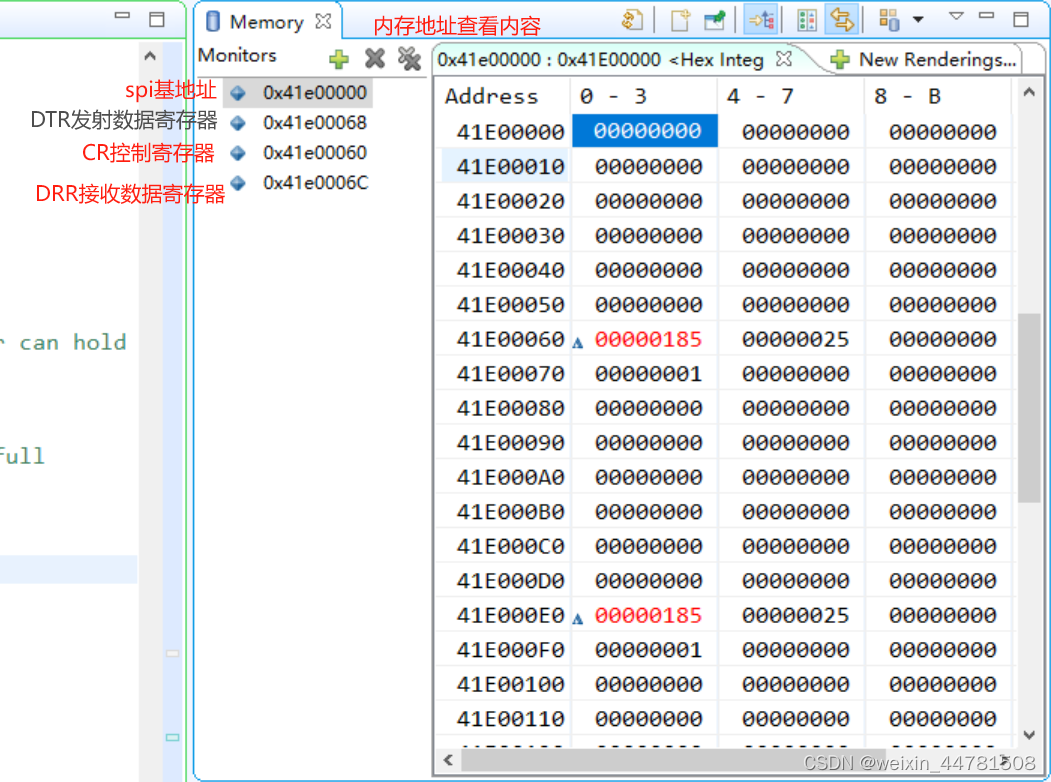

【ZYNQ】AXI-Quad-SPI SDK 开发记录 测试

前人工作 如前人工作,在Navigate to BSP Settings中找到历例程 file:///F:/Xilinx/Vitis/2019.2/data/embeddedsw/XilinxProcessorIPLib/drivers/spi_v4_5/doc/html/api/example.html 使用XSpi_LowLevelExample例子,源代码的AI解析 int

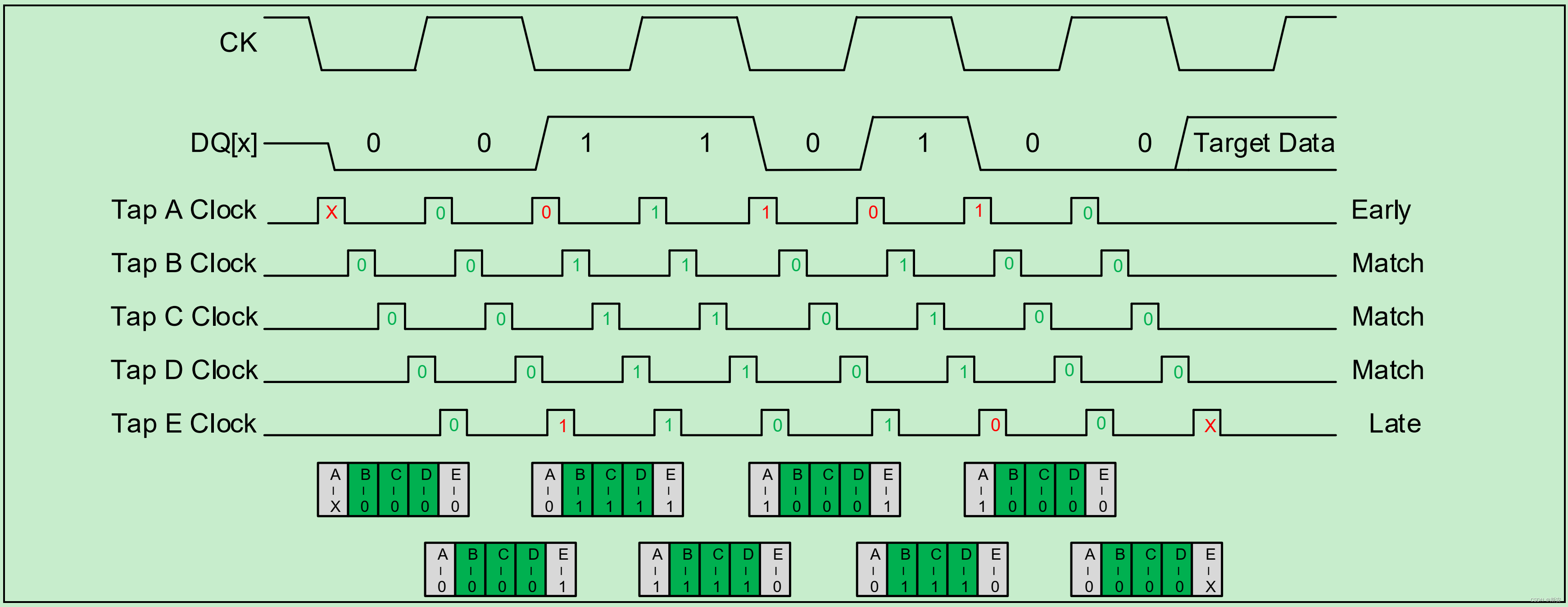

Quad SPI的DLP优化原理

1 前言 1.1 Quad SPI Flash QSPI的I/O接口如图1所示,其中: ① CS:片选信号,低电平有效(FLASH被选中); ② CK:时钟信号,由主设备产生; ③ SI/SO: SI,即MOSI(master out slave in);SO,即MISO(master in slave out);

Zynq 7000 系列之启动模式—Quad-SPI启动

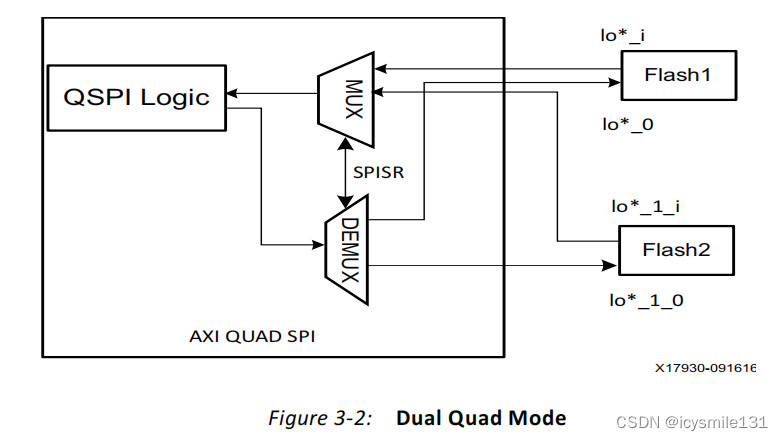

Quad-SPI启动是一种高效的闪存启动方式,它利用Quad-SPI接口的高速数据传输能力来加速启动过程。Quad-SPI(四路串行外设接口)是一种改进的SPI(串行外设接口)协议,通过使用四条数据线而不是传统的单条数据线,实现了更高的数据传输速率。 1 特点 Quad-SPI 启动的主要特点有: • 支持x1、x2和x4单设备配置。这些配置允许用户根据具体的存储需求和性能要求,灵活选择Qua

「Unity3D」UGUI Text <quad/> 使用详解:一种实现图文混排的策略

首先,我们看一下官方说明。 This is only useful for text meshes and renders an image inline with the text. 关键词在于:text meshes 和 image inline ——这说明,<quad/>设计是用在TextMesh而不是Text,并且它是一个文本内嵌图片,即可以自动图文混排。 其次,看一下官方例子

[Unity]关于大的Quad在移动设备上使用Unity自带雾效的问题

如果创建一个足够大的Quad(比如用作地形),然后给它使用Unity自带的雾效,会发现在PC上表现正常,到移动设备上就成了从Quad下方到上方逐渐变浓的雾,原因是Unity自带雾效在移动平台(#if defined(SHADER_API_MOBILE))的时候会强制做逐顶点插值而不是做逐像素插值,所以我们需要自己重写一下UNITY_TRANSFER_FOG和UNITY_APPLY_FOG这两个宏.

龙迅LT6911GX HDMI2.1 to Quad-port MIPI/LVDS with Audio规格简介

龙迅新推出HDMI转MIPI 4K@120Hz芯片完美体现8K屏价值应用 HDMI2.1 Receiver Compliant with HDMI2.1/2.0b/1.4 and DVI1.0Data rate up to 8GbpsSupport HDCP 1.4/2.2/2.3Support HDCP repeaterSupport 8K@30HzSupport 4K@120

CCTextureAtlas(Atlas地图集图册-表示将小纹理组成一张纹理集以达到批量渲染目的 方法-TextureAtlas维护了一个ccV3F_C4B_T2F_Quad数组)

纹理和地图集 供AtlasSpriteManager与AtlasSprite的材质类 从Texture2D继承而来,在其基础上增加了一个非常重要的成员变量 ccV3F_C4B_T2F_Quad * quads 实际上AtlasSprite相比Sprite能快更得进行大批量渲染也是因为这个 TextureAtlas维护了一个ccV3F_C4B_T2F_Quad数组,使用一张texture

axi_quad_spi

文章目录 系统框图正常模式XIP模式 性能IP 核配置AXI Interface OptionXIP ModePerformance Mode SPI OptionsModeTransaction WidthFrequency RatioSlave DeviceEnable Master ModeEnable STARTUP Primitive 寄存器映射0x40 (SRR) 软件复位0x

osg::DrawElements*系列函数及GL_QUAD_STRIP、GL_QUADS绘制四边形效率对比

目录 1. 前言 2. osg::DrawElements*系列函数用法说明 3. GL_QUADS、GL_QUAD_STRIP用法及不同点 4. 效率对比 5. 总结 6. 参考资料 1. 前言 利用osg绘制图元,如:三角形、四边形等,一般用osg::PrimitiveSet类。其派生出了很多子类,如下图所示: 图1 在开发中,用DrawEleme

leetcode 558. Logical OR of Two Binary Grids Represented as Quad-Trees | 558. 四叉树交集(分治法)

题目 https://leetcode.com/problems/logical-or-of-two-binary-grids-represented-as-quad-trees/ 题解 自己写的没通过,这题不方便构造测试用例,没有找到问题在哪儿。后来看了答案:https://leetcode.com/problems/logical-or-of-two-binary-grids-repr

Ultrascale+ GTY transceivers Quad pll

每个Quad 包含两个基于LC的PLL,称为Quad PLL(qpl0和qpl1)。任何一个QPLL都可以由同一个四路中的串行收发器信道共享,但不能由其他四路中的信道共享。当以高于CPLL工作范围的线路速率操作信道时,需要使用QPLL0/1。gtye3/4_common原语封装了gty qpll0/1,并且在使用qpll时必须实例化。 当信道运行速度超过16.375 GB/s时,QPLL0必须使

C#,数值计算——积分方程与逆理论Quad_matrix的计算方法与源程序

1 文本格式 using System; namespace Legalsoft.Truffer { public class Quad_matrix : UniVarRealMultiValueFun { private int n { get; set; } private double x { get; set; }