本文主要是介绍Ultrascale+ GTY transceivers Quad pll,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

每个Quad 包含两个基于LC的PLL,称为Quad PLL(qpl0和qpl1)。任何一个QPLL都可以由同一个四路中的串行收发器信道共享,但不能由其他四路中的信道共享。当以高于CPLL工作范围的线路速率操作信道时,需要使用QPLL0/1。gtye3/4_common原语封装了gty qpll0/1,并且在使用qpll时必须实例化。

当信道运行速度超过16.375 GB/s时,QPLL0必须使用GTREFCLK0,QPLL1必须使用GTREFCLK1。QPLL0/1输出为在同一个Quad 内的每个串行收发器信道的Tx和Rx时钟分频器数据块提供参考时钟,从而控制PMA和PCS数据块使用的串行和并行时钟的生成。

2-13说明了QPLL0/1体系结构的概念视图。在输入时钟被送入相频率检测器之前,它被一个系数m所除。反馈分压器n决定VCO的倍增比。对于低于28.1 GB/s的线速率,支持fractional-N除法器,其中有效比是n因子加分数部分的组合。QPLL0/1

输出频率取决于QPLL[0/1]CLKOUT_RATE的设置。当QPLL[0/1]CLKOUT_RATE设置为HALF时,输出频率为VCO频率的一半。当设置为FULL时,输出频率与VCO频率相同。一个lock indicator比较参考时钟和VCO反馈时钟,以确定是否已实现频率锁定。

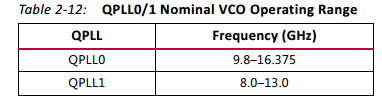

QPLL0/1 VCO在两个不同的频段内工作。表2-12描述了这些波段的额定工作范围。有关更多信息,请参阅UltraScale和UltraScale+设备数据表

向导根据应用程序要求选择适当的波段和qpll设置。

公式2-3显示了如何确定PLL输出频率(GHz)。对于高于28.1 GB/s的线速率,忽略小数部分。

![]()

公式2-4显示了如何确定线速率(GB/s)。d表示信道中Tx或Rx时钟分频器块的值。D的有效设置见第45页表2-9。

![]()

方程式2-5显示了如何确定方程式2-3中给出的反馈除法器的分数部分。

![]()

以10.3125G为例,Fpllclkin=64.453125M,N=160,M=1,QPLL_CLKOUTRATE=2,D=1。

fpllclkout=64.453125*160/2=5.15625G

flinerate=fpllclkout*2/D=10.3125G

这篇关于Ultrascale+ GTY transceivers Quad pll的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!