pll专题

紫光同创——PLL IP 的使用(Logos2)

本文档主要针对 Logos2 系列的 PLL 配置,至于 Logos 系列的 PLL,可以参考《PLLIP 的使用(Logos)》的文档。 一、PLL IP 介绍 1、PLL 基本配置模式 Basic Configurations PLL IP 是紫光同创基于 PLL 及时钟网络资源设计的 IP,通过不同的参数配置,可实现时钟信号的调频、调相、同步、频率综合等功能。 Logos2

【FPGA】clocking wizard配置(PLL/MMC内核配置)

明天准备更vivado的iserdes内核,ISE可能不怎么更了,由于毕设要开始搞了,准备直接转vivado,其实都差不多。今天先把ISE的始终管理内核说一下吧。 第一页,clocking features选项框中的 1.Frequency synthesis选项是允许输出与输入时钟不同频率的时钟。 2.Spread Spectrum选项是提供调制时钟输出,用来降低电子设备产生

1.PLL的原理,怎样用它倍频

PLL - PHASE-LOCKED LOOP 中文称锁相环, 简单来说就是用一个压控振荡器 (VCO - VOLTAGE CONTROLLED OSCILLATOR) 产生一个振荡频率, 经过 N 倍分频 (N - 包括 1 的正整数) 后在鉴相器上与被锁的已知频率比较, 比较结果波形通过低通滤波产生一个电压, 然后用这个电压控制 VCO 去改变振荡频率, 直到分频的振荡频率与已知频率相等并锁相

arm中的PLL,MPLL,UPLL,FCLK,HCLK,PCLK的作用概述

前言: 不同公司,不同等级的ARM架构也是有许多共同的地方,因此以最为广泛使用的2440为实例讲解。 一,PLL S3C2440 CPU主频可达 400MHz,开发板上的外接晶振为 12M,通过时钟控制逻辑的PLL(phase locked loop,锁相环电路)来倍频这个系统时钟。2440有 两个PLL(phase locked loop)一个是 MPL

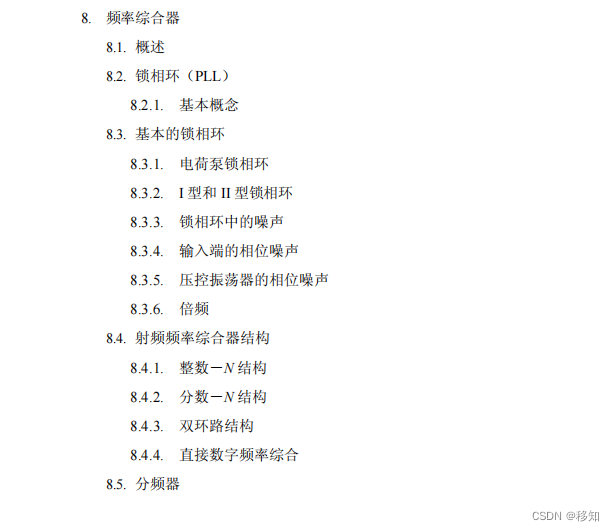

锁相环(PLL)经典书籍分享(可下载)

锁相环(PLL)作为一种确保系统同步的控制机制,广泛应用于频率合成、时钟恢复、信号调制与解调等多个方面。 探索锁相环(PLL)技术的深度和广度,最有效的途径之一便是通过专业书籍的系统学习。以下是为渴望掌握PLL知识的读者精心挑选的几本必备书籍,它们将引导您从基础理论到高级应用,全面深入地理解PLL的设计与应用。 《锁相环(PLL)电路设计与应用》 作者:远坂俊昭 对于想要深入学习PLL

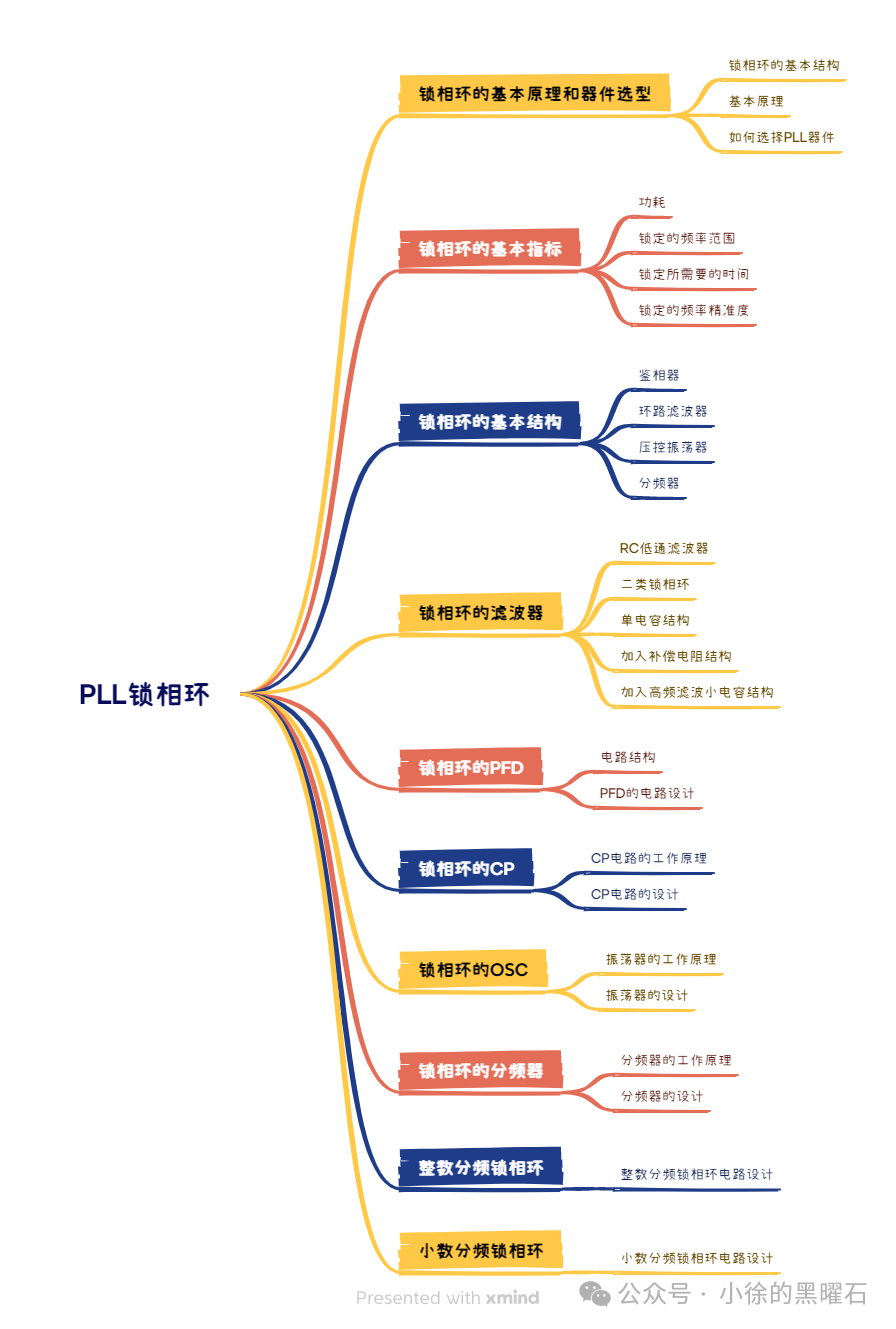

PLL深度解析第一篇——PLL的知识图谱

在硬件电路中,时钟就像心脏一样,在时钟的节拍下,不同的芯片、不同的电路、不同的接口都可以有序的进行工作或者通信(类似流水线一样,必须有节奏的运行)。 但是在芯片中,不同的模块和接口工作的频率并不一样,我们需要把提供的参考时钟转换到不同的模块和接口需要的频率上去,一般起到该功能的有分频器、PLL锁相环、CLK buffer等,一起组成了芯片复杂的CLK tree来对时钟频率进行转换和分配。

Xilinx 7系列MMCM/PLL端口简介

在FPGA设计中,MMCM和PLL的端口允许设计者进行各种配置,包括设置时钟源的选择、分频系数、相位偏移等参数。此外,这些端口还可以提供时钟信号的状态信息,如是否锁定、频率误差等,以便设计者进行监控和调试。 具体的端口包括: 1、CLKIN1 - 主参考时钟输入 可以由同一局部时钟域内的SRCC或MRCC I/O直接驱动,也可以通过CMT主干线由垂直相邻时钟区域内的SRCC或MRCC I/O驱

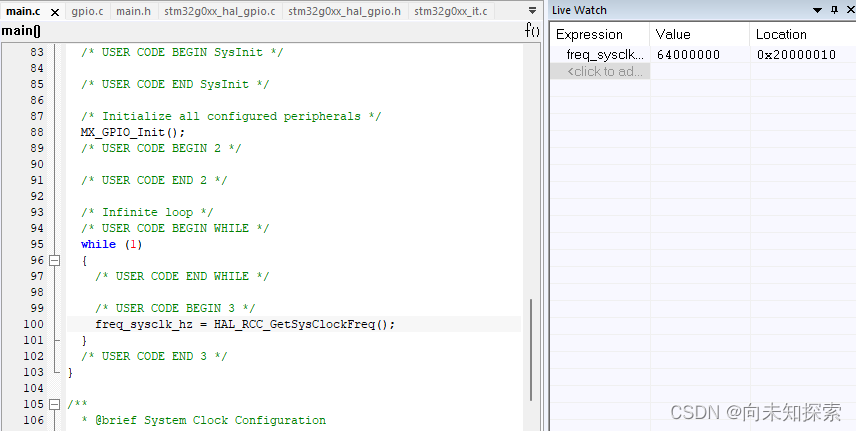

【NUCLEO-G071RB】005——RCC-PLL时钟配置

NUCLEO-G071RB:005——RCC-PLL时钟配置 设计目标芯片配置程序修改仿真测试 设计目标 将HSI通过PLL倍频到64MHz,并作为系统时钟。 芯片配置 切换到Clock Configuration选项卡,以图形化界面配置时钟。System Clock Mux是CPU核心的时钟源选择器,我们这里选择PLLCLKPLL Source Mux是PLLCLK的时钟

PEG(2K)-g-[3.5]-PLL(20k)-g[3.5]-PEG(3.4k)-Biotin 生物素修饰聚乙二醇聚赖氨酸聚乙二醇

PEG-g-PLL-g-PEG-BIOTIN是一种生物素修饰的三嵌段共聚物。 PLL(Poly-L-lysine)是一种阳离子聚合物,由L-赖氨酸单体组成的聚合物。它具有多种应用,包括细胞培养、基因转染、组织工程和生物传感器等领域。 生物素可以与蛋白质亲和结合,被广泛用于分析分离和纯化目标蛋白质。 PEG-g-PLL-g-PEG-Biotin是一种具有广泛应用潜力的化合物,可用于生物分析、生

11 PLL IP核

PLL IP 核简介 锁相环(PLL)作为一种反馈控制电路,其特点是利用外部输入的参考信号来控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环拥有强大的性能,可

[嵌入式软件][入门篇][仿真平台][STM32CubeMX] GPIO和PLL的介绍

文章目录 一、GPIO简介(1) IO类型和功能(2) 内部上下拉 二、PLL简介(1)什么是锁相环(2)我们只需知道什么? 三、STM32CubeMX配置四、HAL库的使用五、示例代码六、仿真效果(指示灯闪烁) 一、GPIO简介 GPIO是通用输入输出端口的简称,可以通过软件来控制输入和输出。 STM32的 GPIO 引脚与外部设备连接起来,从而实现与外部通讯、 控制以及数据

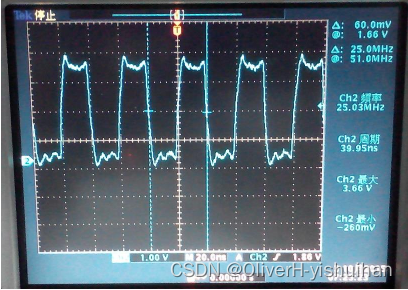

Quartus PLL分频

在Quartus中实现PLL分频,输入FPGA引脚上的25MHz的时钟,配置PLL使其输出四路分别为12.5Mhz,25Mhz,50Mhz和100MHz的时钟信号。 选择菜单Tools–>Mega Wizard Plug-In Manager选项 点击next 点击i/o中的ALT[LL,右上角的器件选择根据自己选择,保存路径建议先在整个工程文件夹中建立ip_core—>pll文件夹,这里

小梅哥Xilinx FPGA学习笔记18——专用时钟电路 PLL与时钟向导 IP

目录 一:IP核简介(具体可参考野火FPGA文档) 二: 章节导读 三:PLL电路原理 3.1 PLL基本实现框图 3.2 PLL倍频实现 3.3 PLL分频实现 四: 基于 PLL 的多时钟 LED 驱动设计 4.1 配置 Clocking Wizard 核 4.2 led 闪烁控制 4.2.1 LED闪烁代码设计 4.3 顶层模块代码设计 4.4 仿真测试文件 4.5

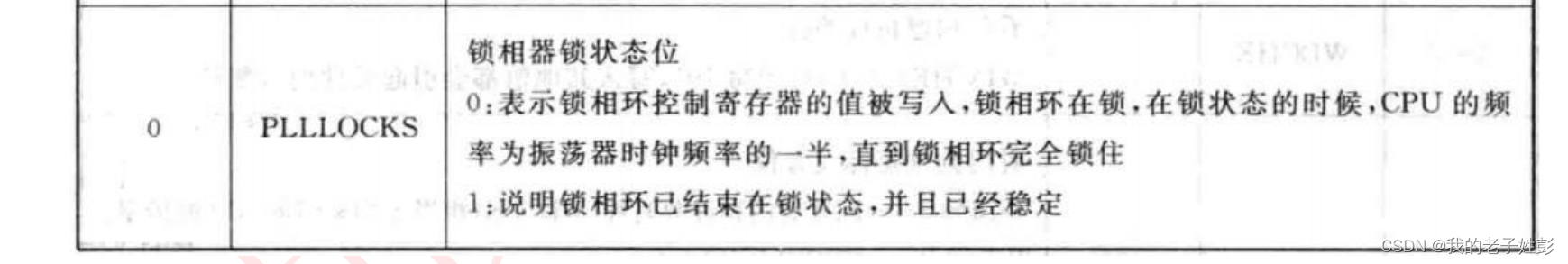

DSP2335的时钟PLL配置

PLL模块框图 xclkin是直接进来的外部时钟; 而下面的是振荡器(晶振出来)的时钟 PLLSTS 锁相环状态寄存器 PLLCR 锁相环控制寄存器 PLLSTS【oscoff】 决定着外部时钟的输入 PLLSTS【plloff】 锁相器关闭位 0使能PLL 锁相环控制寄存器用于控制芯片 PLL 的倍数,在向 PLL 控制寄存器进行写操 作之前,需要

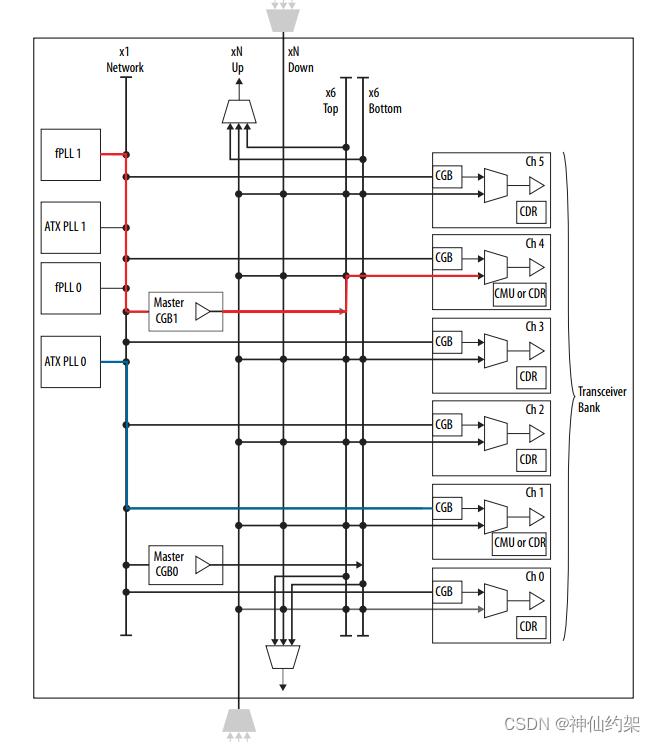

Ultrascale+ GTY transceivers Quad pll

每个Quad 包含两个基于LC的PLL,称为Quad PLL(qpl0和qpl1)。任何一个QPLL都可以由同一个四路中的串行收发器信道共享,但不能由其他四路中的信道共享。当以高于CPLL工作范围的线路速率操作信道时,需要使用QPLL0/1。gtye3/4_common原语封装了gty qpll0/1,并且在使用qpll时必须实例化。 当信道运行速度超过16.375 GB/s时,QPLL0必须使

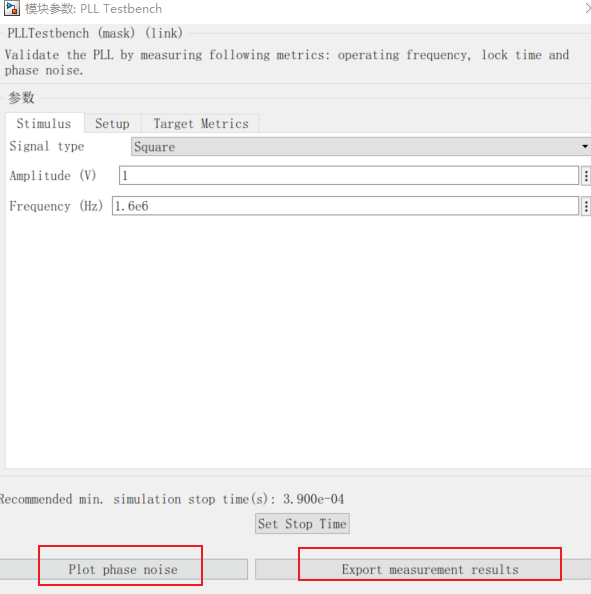

Matlab simulink PLL学习笔记

本文学习内容:【官方】2022小迈步之 MATLAB助力芯片设计系列(一):电路仿真与模数混合设计基础_哔哩哔哩_bilibili 时域模型 testbench搭建 菜单栏点击simulink 创建空白模型 点击库浏览器 在PLL里面选择一种架构拖拽到画布。 如图。 在testbench里面找到PLL的测试平台拖拽到画布。 如图。 连线 右击P

从Intel Cyclone10GX TransceiverPHY 高速收发器认识ATX PLL、FPLL、CMU PLL等PLL

文章目录 前言一、pandas是什么?二、使用步骤 1.引入库2.读入数据总结 前言 在使用Intel Cyclone10GX TransceiverPHY的过程中发现这个IP还是比较复杂的,特别是时钟系统,提到了多种PLL:ATX PLL、FPLL、CMU PLL,这里进行一下扩展学习。 关于TransceiverPHY Intel Cycl

Lattice FPGA在diamond的IPexpress中,在频率模式下配置PLL时,IPexpress工具是否可以使用小数N值?

完整版请点击 https://hifpga.com/问题/1093 向博主本人提问FPGA相关问题 Lattice FPGA在diamond的IPexpress中,在频率模式下配置PLL时,IPexpress工具是否可以使用小数N值? Ipexpress中的小数N值仅支持分频器模式,用于产生小数输出频率,但在频率模式下不支持。

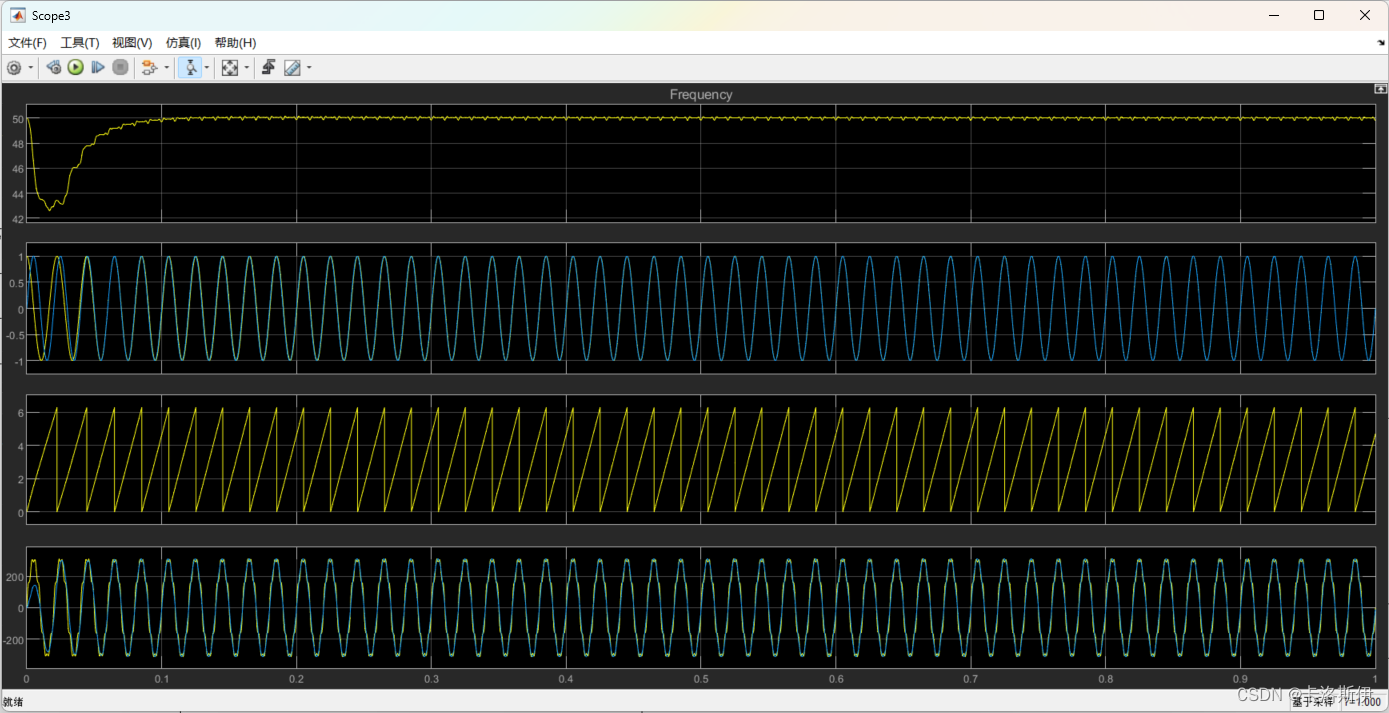

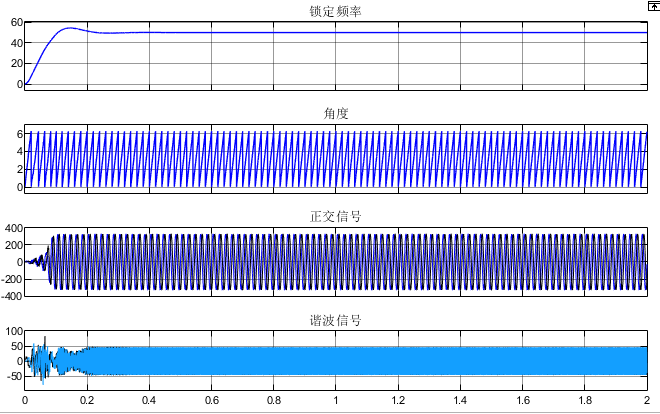

双向交错CCM图腾柱无桥单相PFC学习仿真与实现(2)SOGI_PLL学习仿真总结

目录 前言 SOGI基本原理 锁相环基本原理 仿真实现及说明 总结 前言 前面总结了双向交错CCM图腾柱无桥单相PFC系统实现,后面把问题细分,关于SOGI锁相环的应用和学习在这里总结下。 双向交错CCM图腾柱无桥单相PFC学习仿真与实现(1)系统问题分解_卡洛斯伊的博客-CSDN博客 SOGI基本原理 SOGI也叫做二阶广义积分器,也叫正交信号发生器,目的就是得到

FPGA学习——Altera IP核调用之PLL篇

文章目录 一、IP核1.1 IP核简介1.2 FPGA中IP核的分类1.3 IP核的缺陷 二、PLL简介2.1 什么是PLL2.2 PLL结构图2.3 C4开发板上PLL的位置 三、IP核调用步骤四、编写测试代码五、总结 一、IP核 1.1 IP核简介 IP核(知识产权核),是在集成电路的可重用设计方法学中,指某一方提供的、形式为逻辑单元、芯片设计的可重用模组。 IP核通常已经

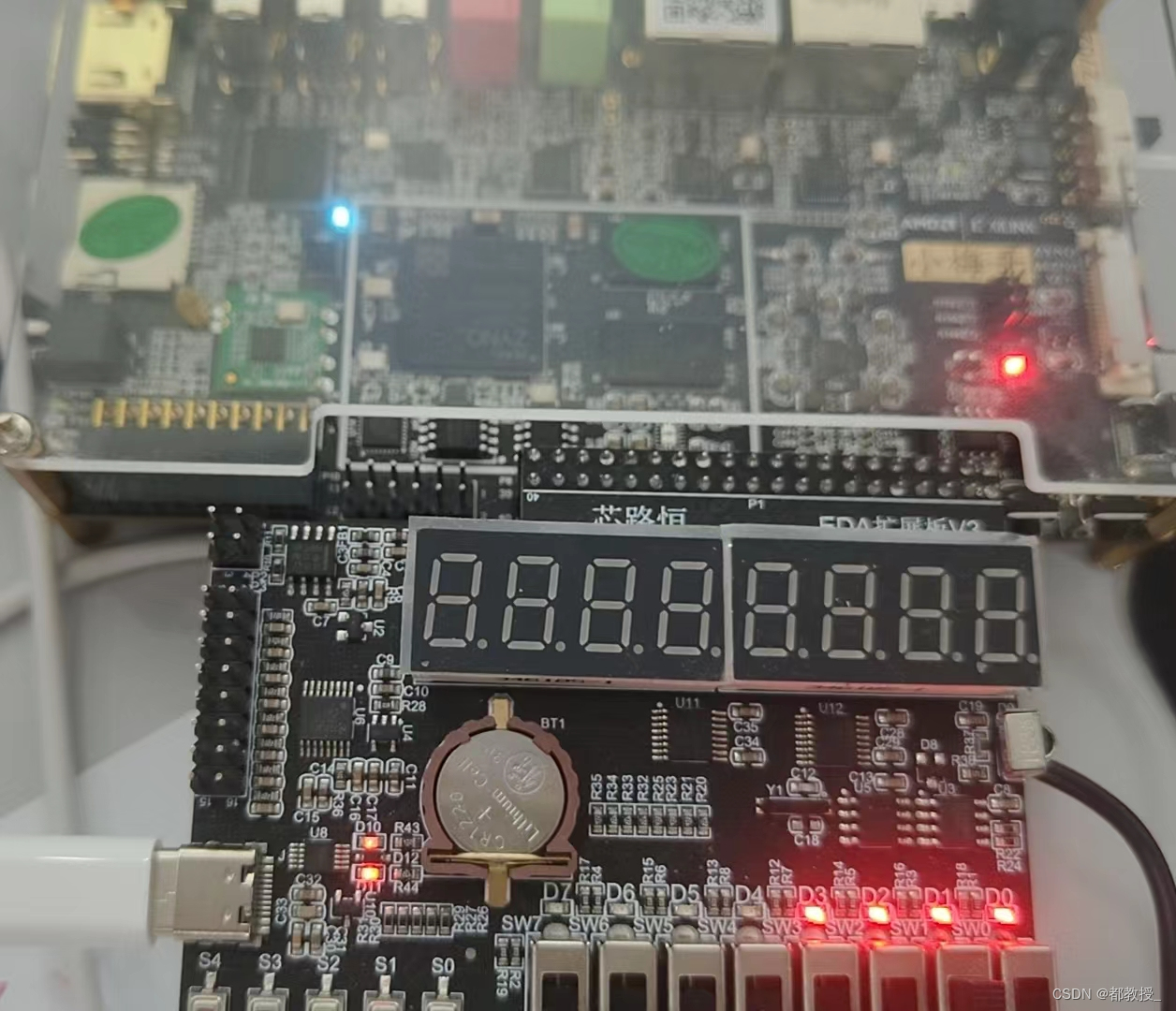

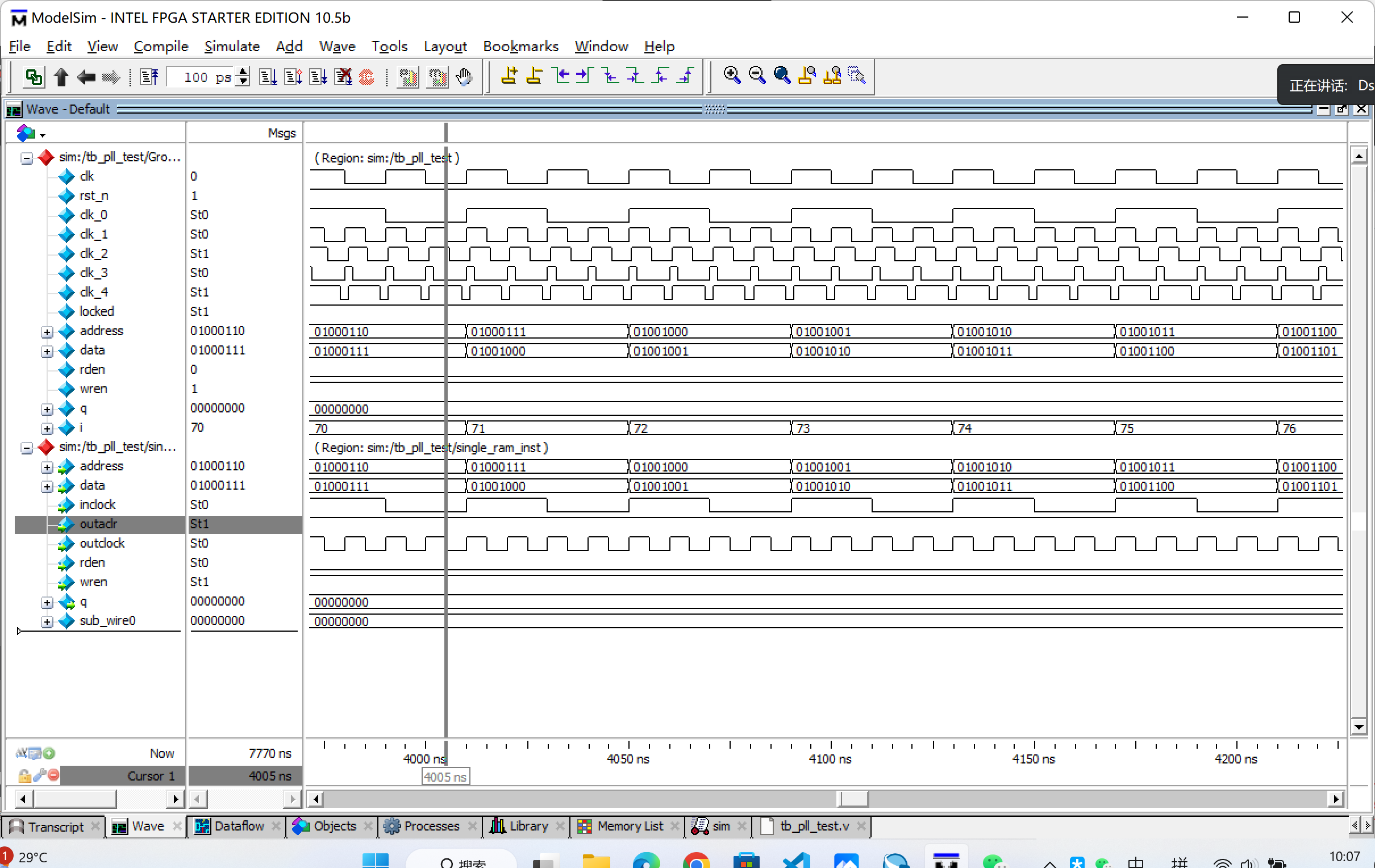

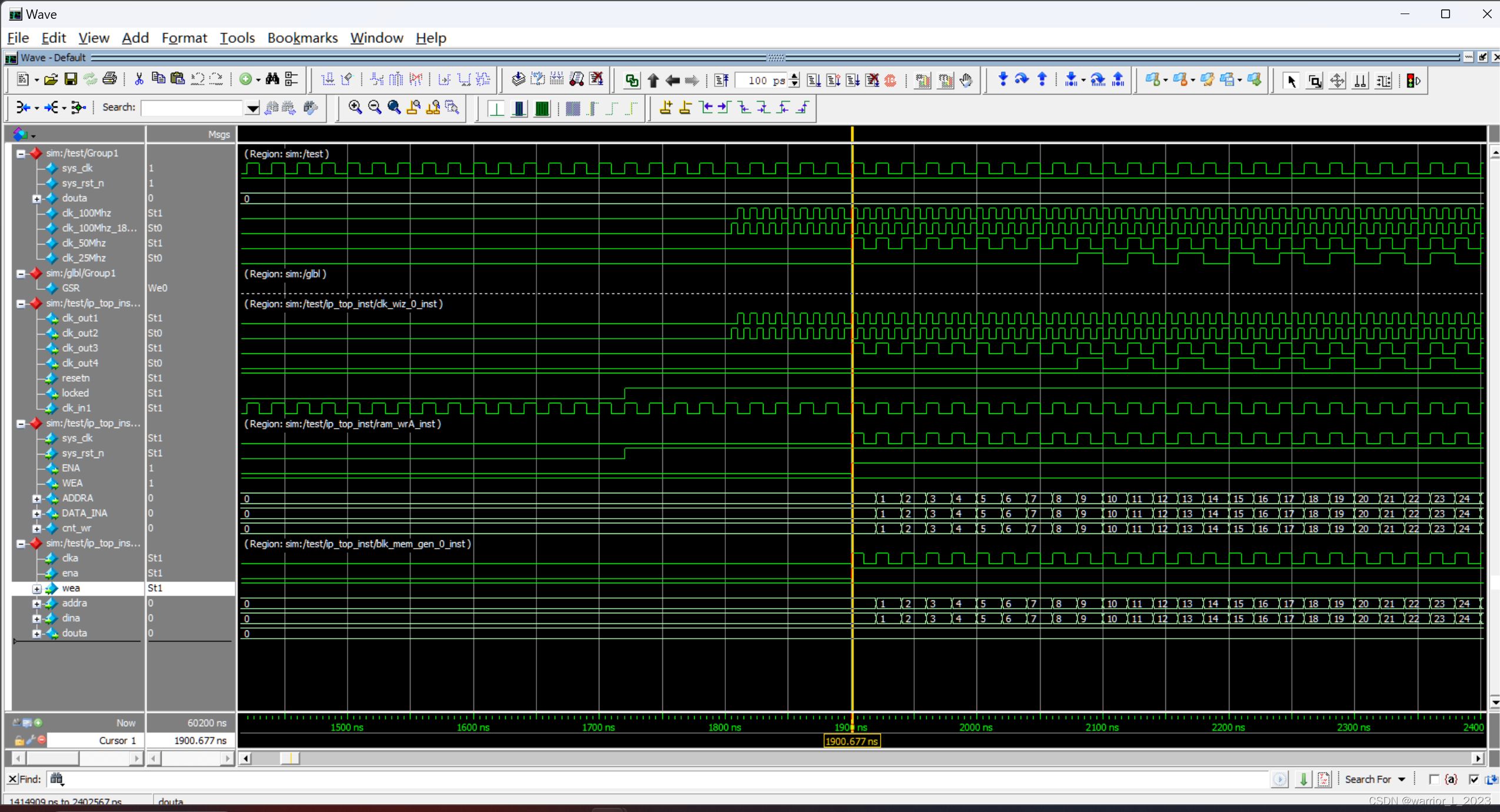

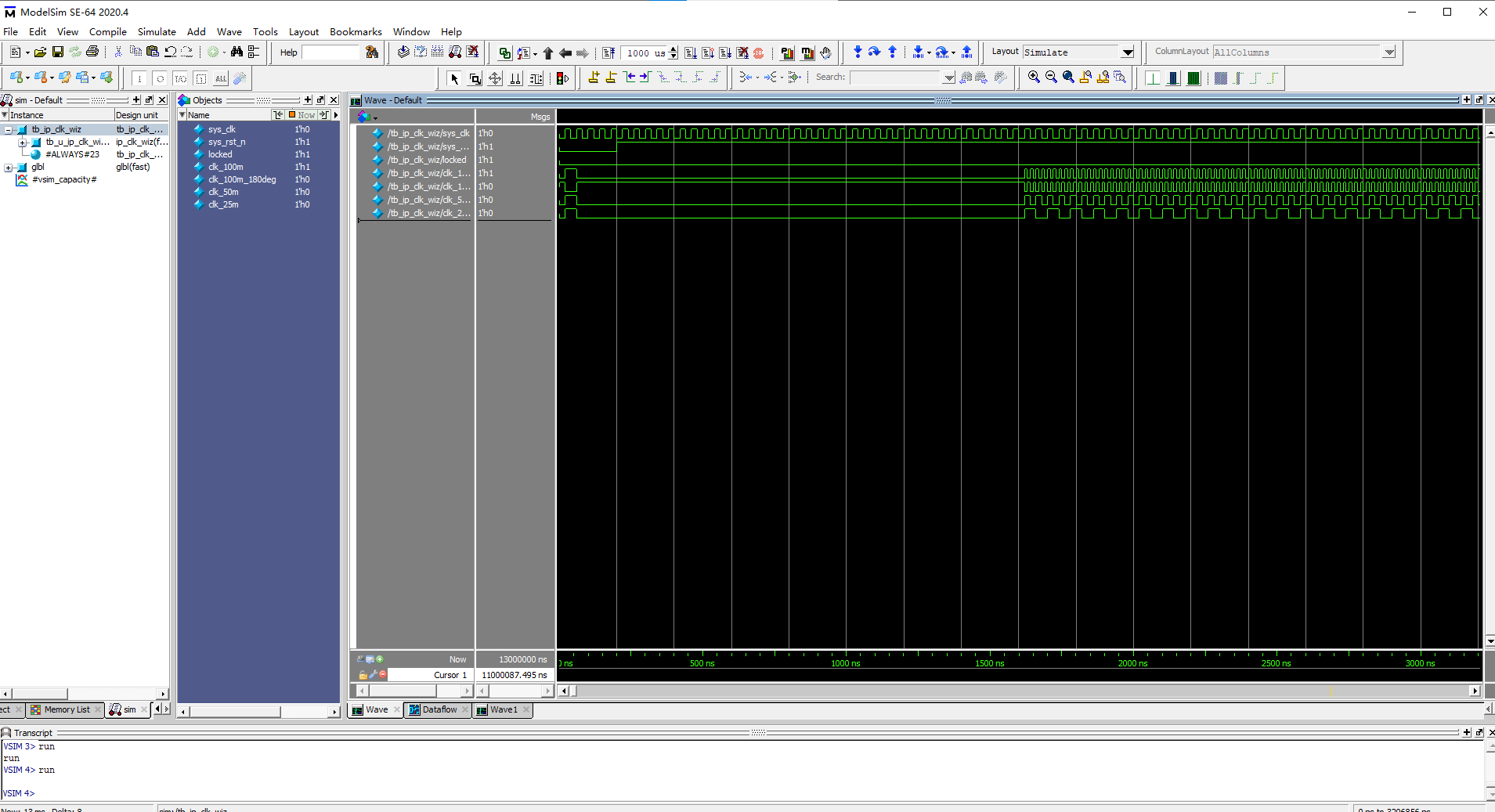

ZYNQ_project:IP_ram_pll_test

例化MMCM ip核,产生100Mhz,100Mhz并相位偏移180,50Mhz,25Mhz的时钟信号。 例化单口ram,并编写读写控制器,实现32个数据的写入与读出。 模块框图: 代码: module ip_top(input wire sys_clk ,input wire sys_rst_n ,out

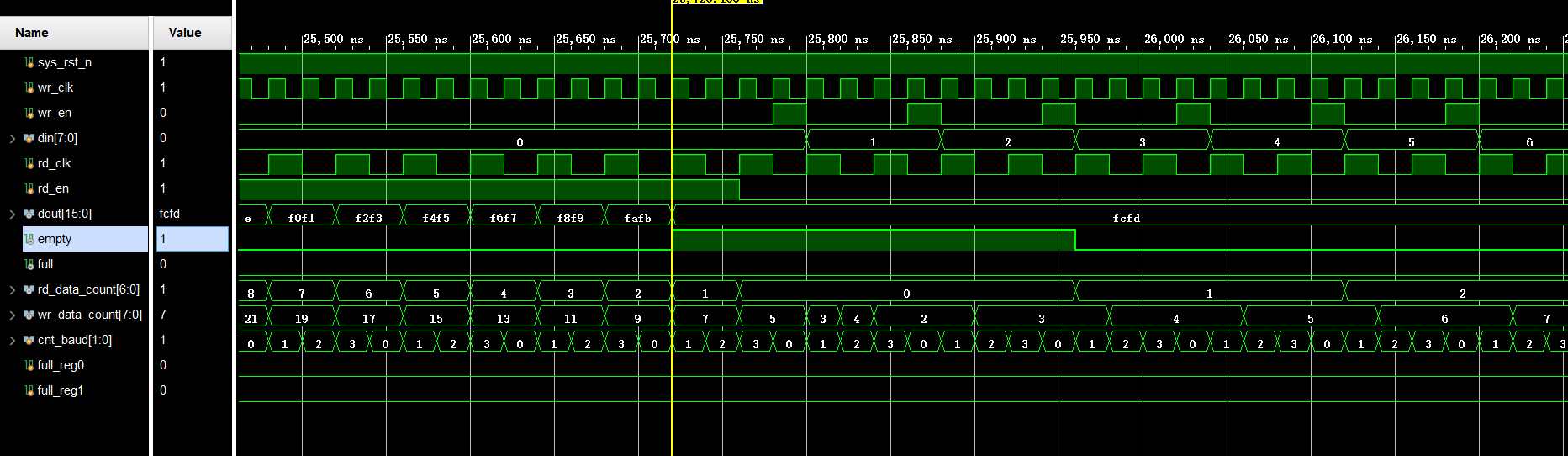

IP核--PLL、ROM、RAM

IP核 理论知识 IP(Intellectual Property)即知识产权,用于 ASIC 或 FPGA 中的预先设计好的电路功能模块。 优点:提高开发效率,减少设计和调试时间,加速开发进程,降低开发成本。 缺点: 跨平台时IP核往往不通用。 IP核是黑匣子,不透明,看不到核心代码。 有些定制的 IP 核由于是不通用的,往往会有较高的收费,这也是一笔巨大的开销。 IP 核有三种不

Vivado 下 IP核之 PLL实验

目录 实验任务:Vivado 下 IP核之 PLL实验 1、实验简介 2、实验环境 3、实验原理 3.1、PLL IP核简介 3.2、MMCM 和 PLL 各自的含义以及两者的区别 3.3、PLL 分频 和 倍频 的工作原理 3.4、实验任务 4、建立工程 4.1、PLL IP 核配置 4.2、模块设计 4.3、编写代码 4.4、Vivado 自带仿真器的使用

基于级联延迟信号消除的锁相环(CDSC_PLL)技术MATLAB仿真

微❤关注“电气仔推送”获得资料(专享优惠) 基于级联型延迟信号消除(CDSC)的锁相环技术(CDSC-PLL),该锁相环克服了传统dq 锁相环在电网电压畸变或不对称时存在较大稳态误差的缺点。CDSC-PLL是在传统dq锁相环的控制环节中加入了一个 CDSC环节,即dqCDSCPLL。 基于延迟信号消除的锁相环原理 通过谐波的半波对称性在dq坐标系中将谐波消除, 也即延迟信号消除(DSC)法,

![PEG(2K)-g-[3.5]-PLL(20k)-g[3.5]-PEG(3.4k)-Biotin 生物素修饰聚乙二醇聚赖氨酸聚乙二醇](https://img-blog.csdnimg.cn/direct/4918c709c0d34338843af737bbab139f.jpeg)

![[嵌入式软件][入门篇][仿真平台][STM32CubeMX] GPIO和PLL的介绍](https://img-blog.csdnimg.cn/direct/1311a99837b44c00ab1c7499cf50234f.gif#pic_center)