本文主要是介绍FPGA学习——Altera IP核调用之PLL篇,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 一、IP核

- 1.1 IP核简介

- 1.2 FPGA中IP核的分类

- 1.3 IP核的缺陷

- 二、PLL简介

- 2.1 什么是PLL

- 2.2 PLL结构图

- 2.3 C4开发板上PLL的位置

- 三、IP核调用步骤

- 四、编写测试代码

- 五、总结

一、IP核

1.1 IP核简介

IP核(知识产权核),是在集成电路的可重用设计方法学中,指某一方提供的、形式为逻辑单元、芯片设计的可重用模组。 IP核通常已经通过了设计验证,设计人员以IP核为基础进行设计,可以缩短设计所需的周期,加速开发进程,降低开发资本。

1.2 FPGA中IP核的分类

- 软核——HDL语言形式:硬件描述语言(综合之前的寄存器传输级(RTL模型));需要经过综合以及布局布线才能使用;可进行参数调整、复用性强;布局布线灵活;设计周期短、设计投入少;对模块的预测性较低,在后续设计有发生错误的风险。

- 固核——网表形式:具体在FPGA设计中可以看做带有布局规划的软核;完成了综合的功能块;可预布线特定信号或分配待定的布线资源。

- 硬核——版图形式:具体在FPGA设计中指布局和工艺固定、经过前端和后端验证的设计;硬核是完成提供设计的最终阶段产品——掩膜(Mask);缺乏灵活性、可移植性差;更易于实现IP核的保护。

1.3 IP核的缺陷

- IP核往往不能跨平台使用(如:Altera和Xlinx的IP核不能相互调用)

- IP核不透明,看不到内部核心代码

- 定制IP需要额外收费

二、PLL简介

2.1 什么是PLL

锁相环 (phase locked loop)是一种利用相位同步产生的电压,去调谐压控振荡器以产生目标频率的负反馈控制系统。根据自动控制原理,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。

以上是百度百科对PLL的说明。

在FPGA中,PLL属于全局时钟网络资源,PLL可以替我们生成稳定优质的不同频率、不同相位的时钟。同时,PLL作为全局时钟资源可以使时钟信号到达各个触发器的时间相近(我们自己编写分频器产生的时钟质量很差,而且到达各级触发器的时间也不相同,全局时钟网络采用了特殊的线材,因此可以做到时延很低)。

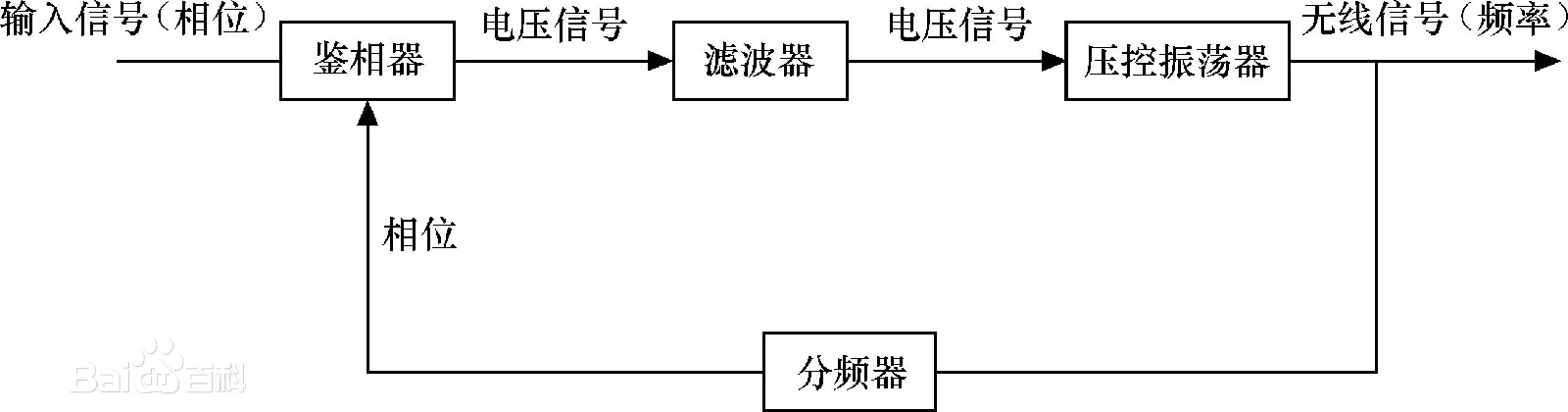

2.2 PLL结构图

由于博主是物联网出身,电路方面的基础实在是很差,所以结构图就不跟大家细分析了,但需要注意的一点是,PLL是一种反馈电路,通过压控振荡器后,信号会通过分频器与鉴相器中我们设置的时钟信号作对比,二者相同后才会产生输出,因此PLL并不会立即输出我们想要的时钟信号,而是会有一段的延时。

2.3 C4开发板上PLL的位置

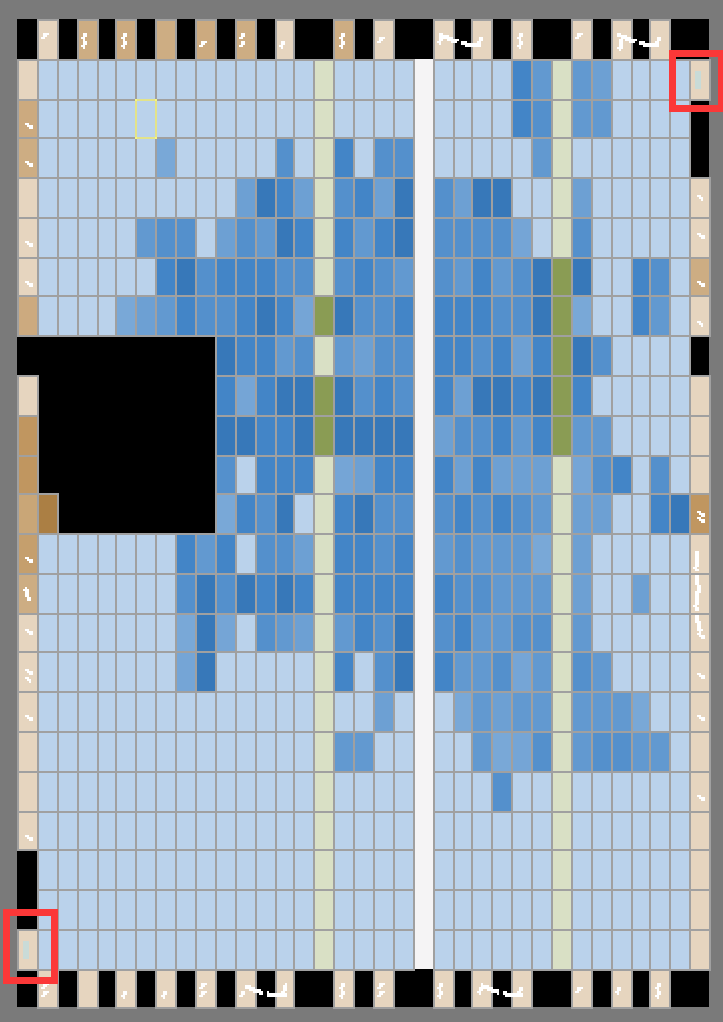

博主所用开发板器件库为Cyclone Ⅳ,芯片型号为EP4CE6F17C8,该开发板的PLL资源如下图:

(点击Quartus菜单栏的TOOLS选项,选中Chip Planner即可调出开发板资源图)

可以看出,该开发板一共有两个PLL资源。同时该开发板的PLL资源为2输入5输出,即可同时输入两路时钟信号,输出五路时钟信号。

三、IP核调用步骤

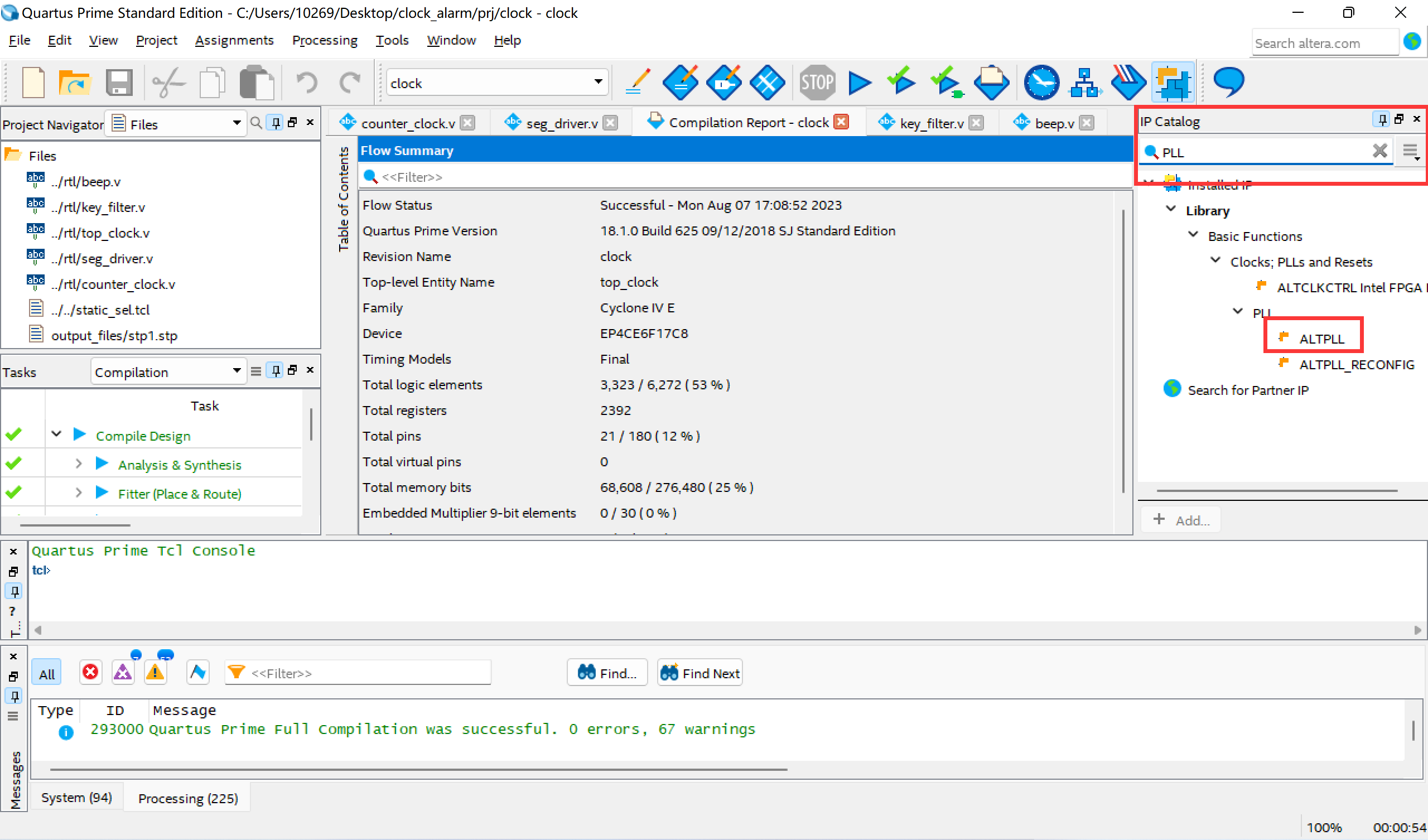

打开Quartus,找到IP Catalog选项卡,输入PLL,选择ATLPLL(Altera PLL),如果没有IP Catalog选项卡,可以点击菜单栏中的View,在Utility Windows勾选上IP Catalog或使用快捷键ALT+F7.

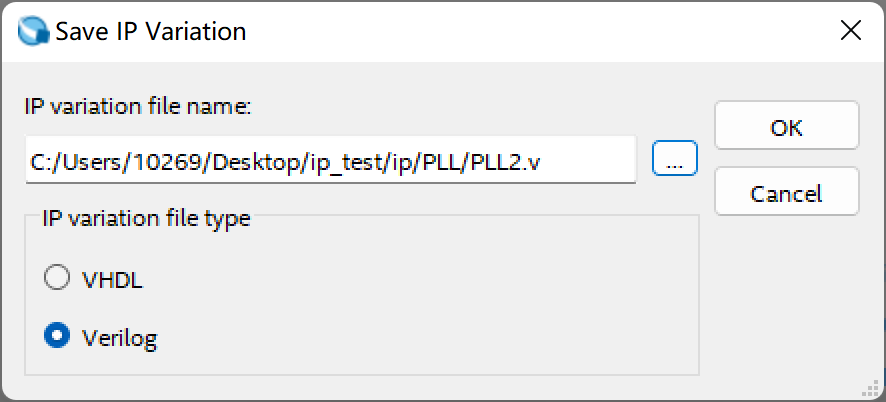

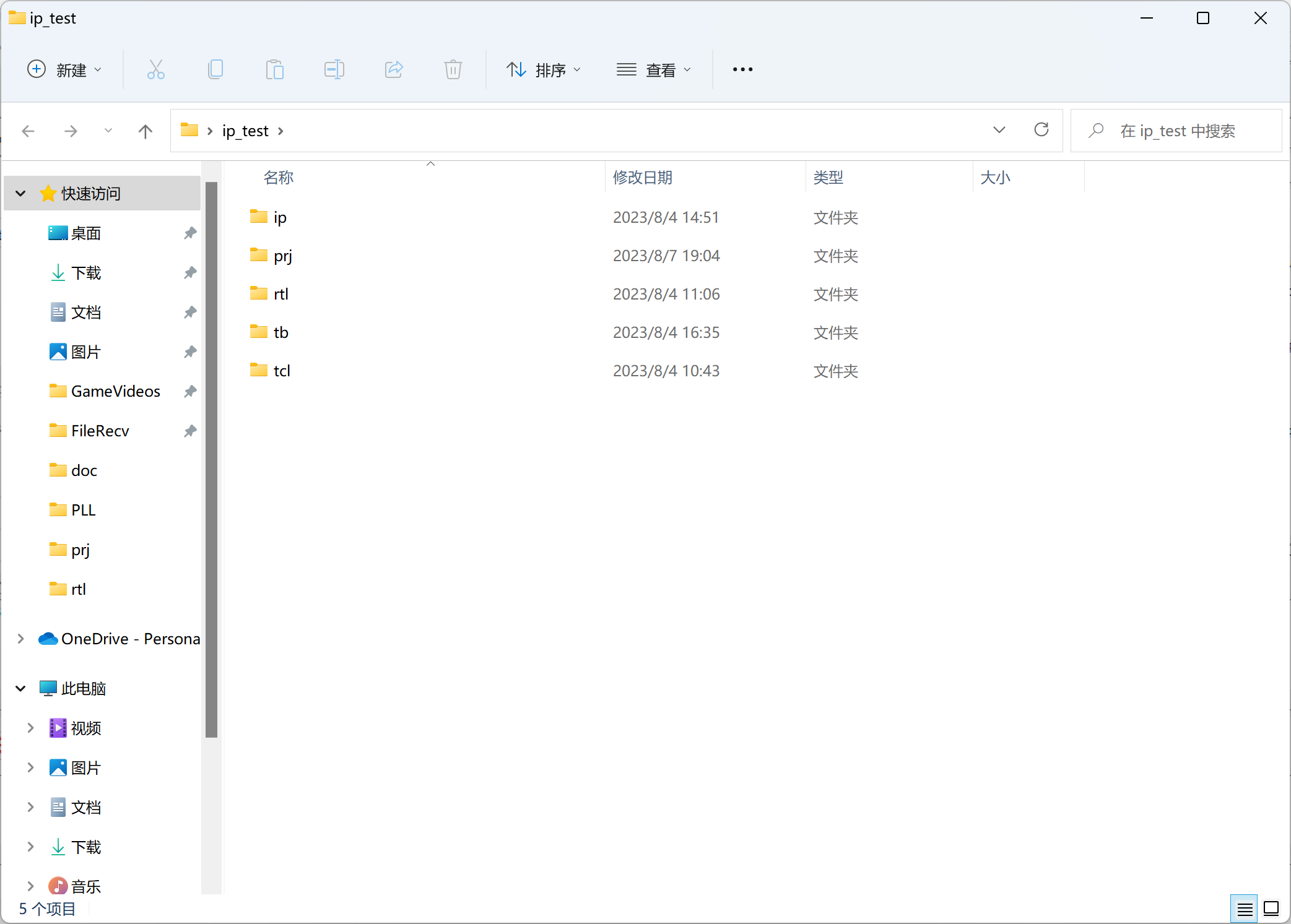

创建IP核时一般新建IP核文件夹,并在其中创建一个所用IP核名称的文件夹(一个项目可能调用多个IP),而后保存文件,如下图所示:

博主的FPGA项目文件结构一般如下:

- IP文件夹用来存储IP核

- prj为项目文件夹,用来存放quartus项目生成的各种文件

- rtl存放源码

- tb存放仿真文件testbench

- tcl存放tcl脚本文件

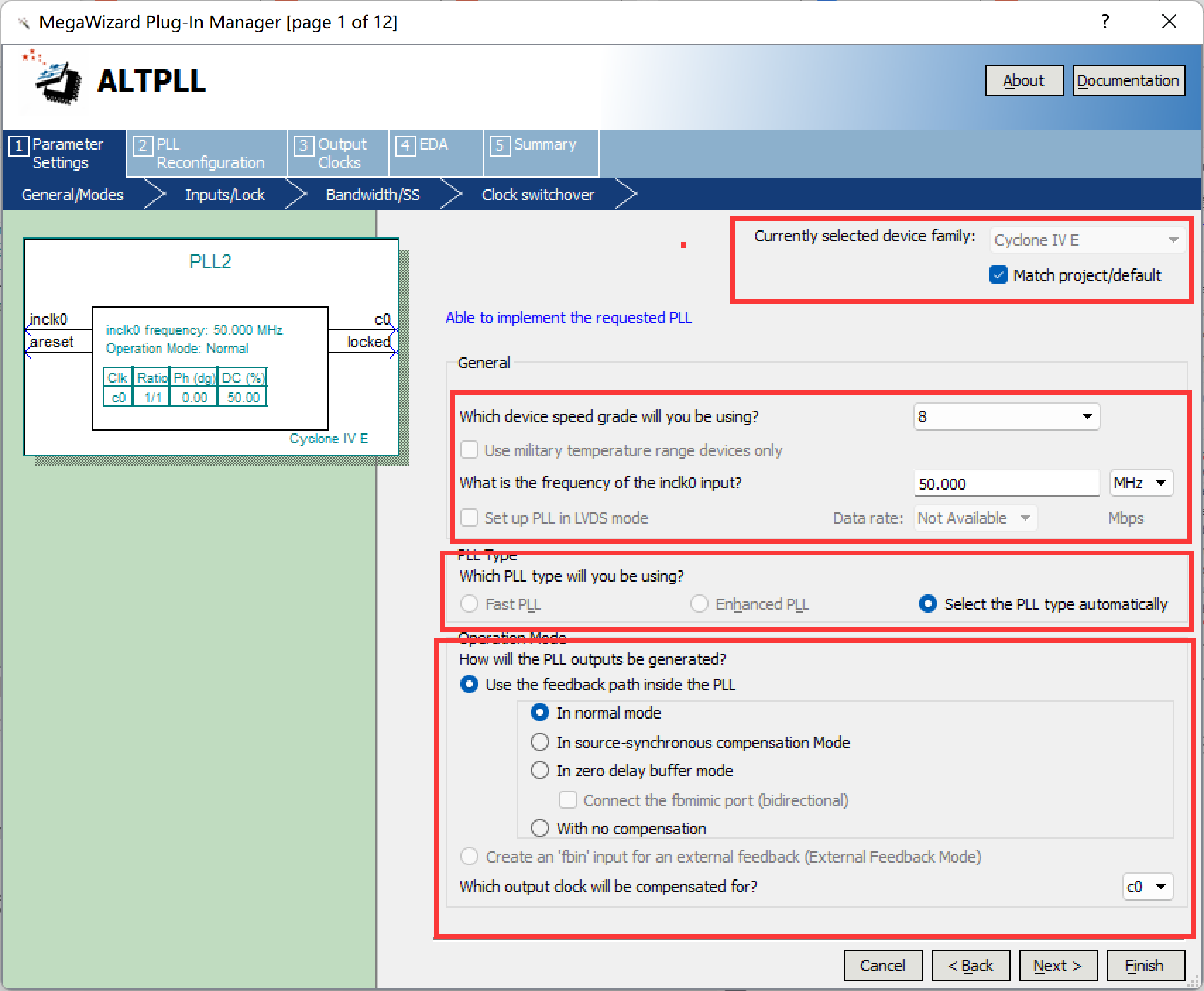

文件保存成功后进入PLL设置选项卡

- 右上角documents联网后点击可以超链接到Altera官方的IP核文档,其中有着详细的配置信息

- 器件库一般默认匹配

- 设备速度等级与下方的输入时钟clk0要与开发板一致!!,博主开发板速度等级为8,时钟频率为50MHz

- PLL种类和模式我们选择默认(具体什么区别自己官方阅读文档,最后强调一次博主也是初学者,也还没用到这些,如有讲错请多包涵)

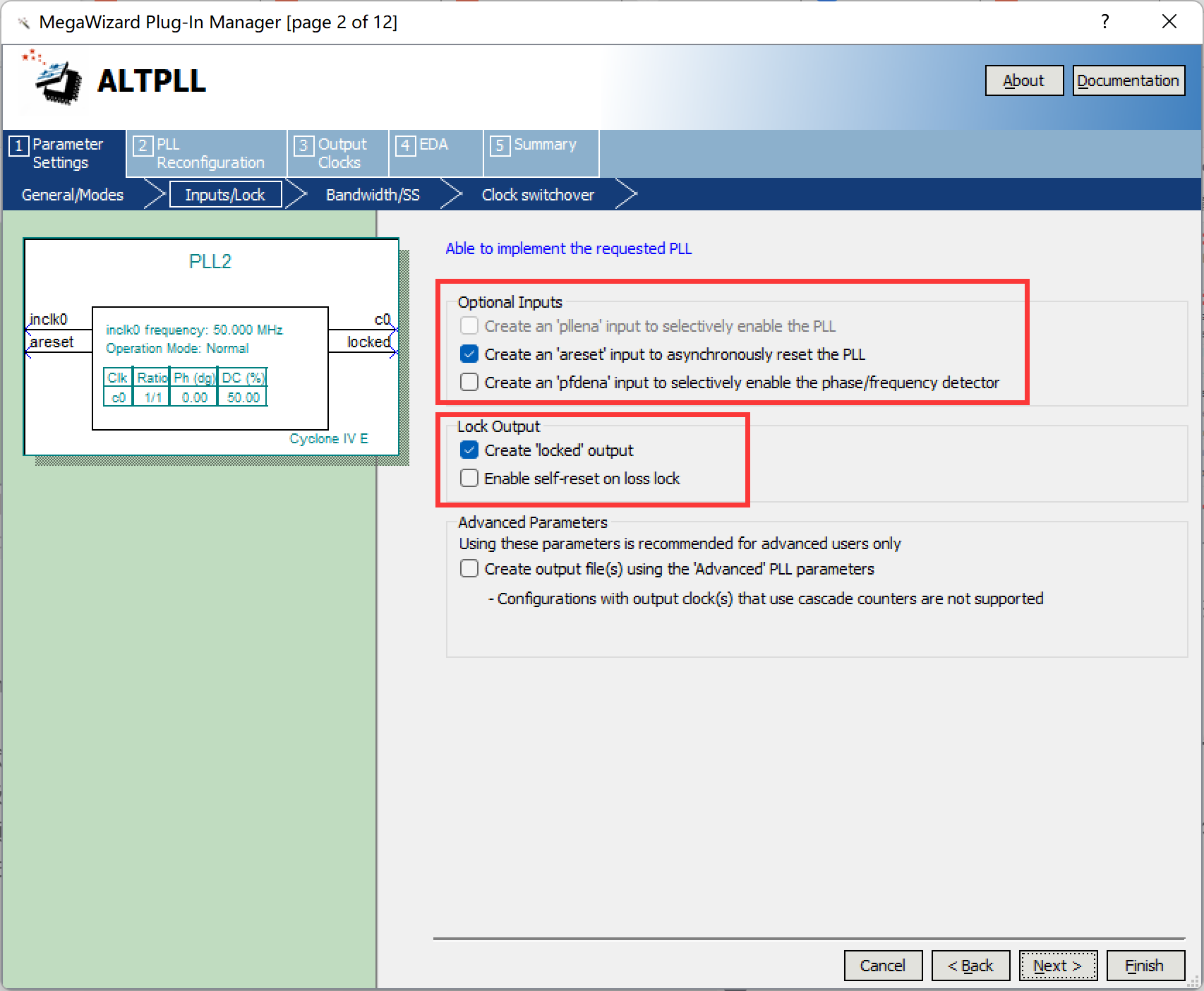

点击next后按下图选择

- arest是复位信号,勾选后会自动为我们创建复位信号(注意:Altera IP核均为高电平有效,如果平时写代码习惯复位信号低电平有效,例化IP核是需要对复位信号取反)

- locked为锁信号,前文博主说道,PLL并不能立即生成稳定的时钟,需要经过一段时间电路的反馈,此时locked信号就会确保不稳定的时钟信号不会进行输出

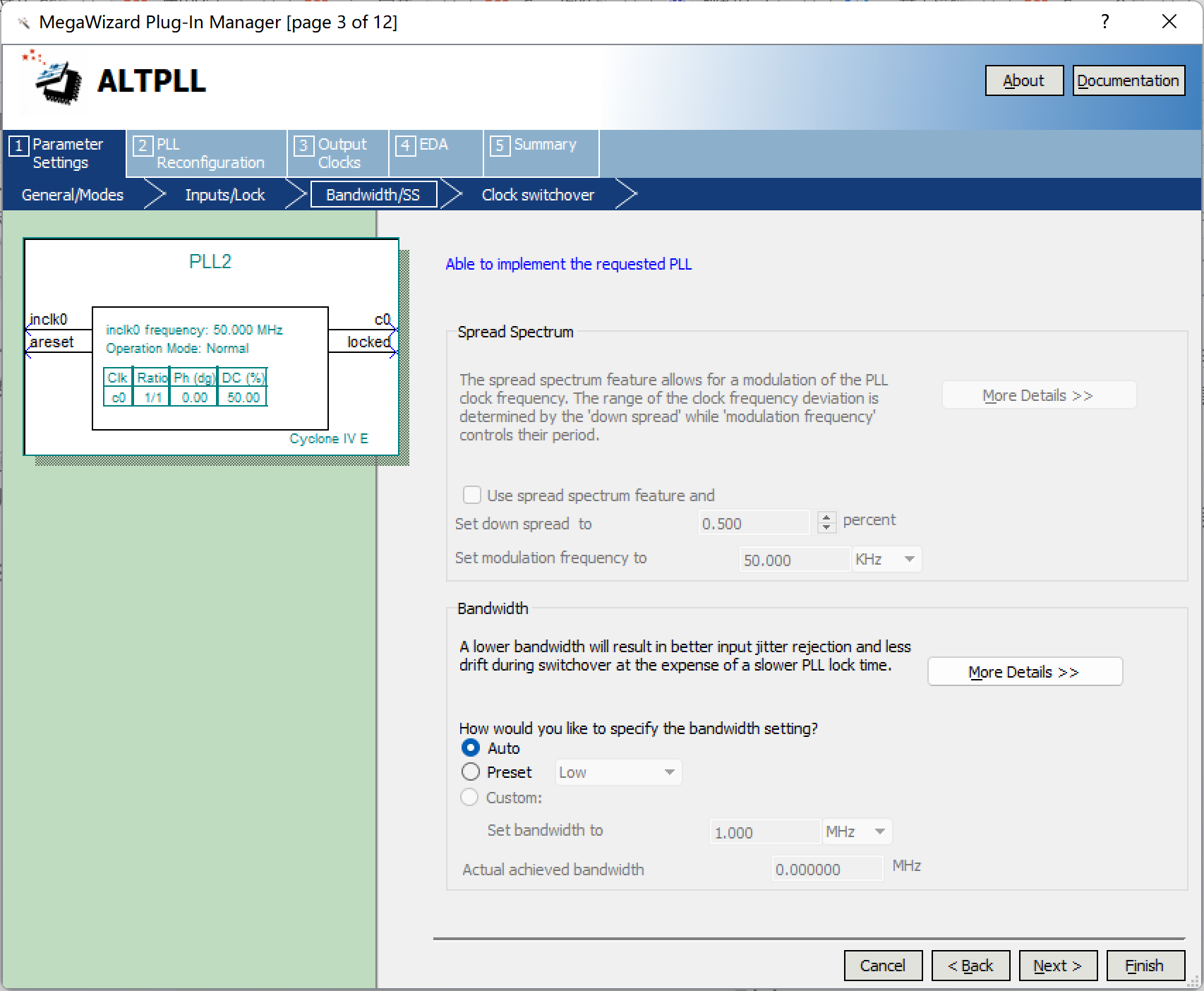

点击next按下图进行选择

- 此界面默认选择即可

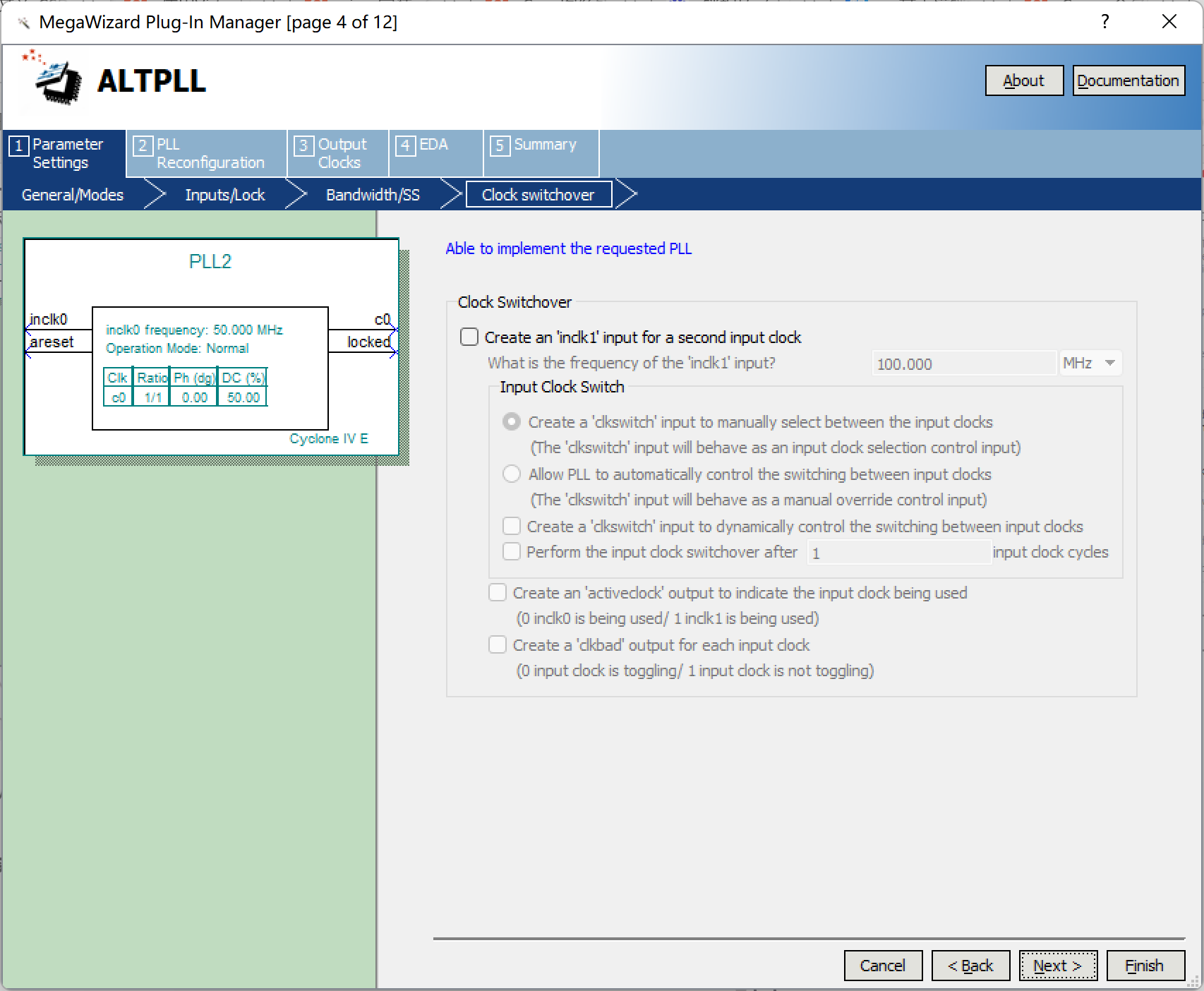

点击next来到如下界面:

- 此界面是在询问我们是否需要设置第二路输入时钟,我们不选

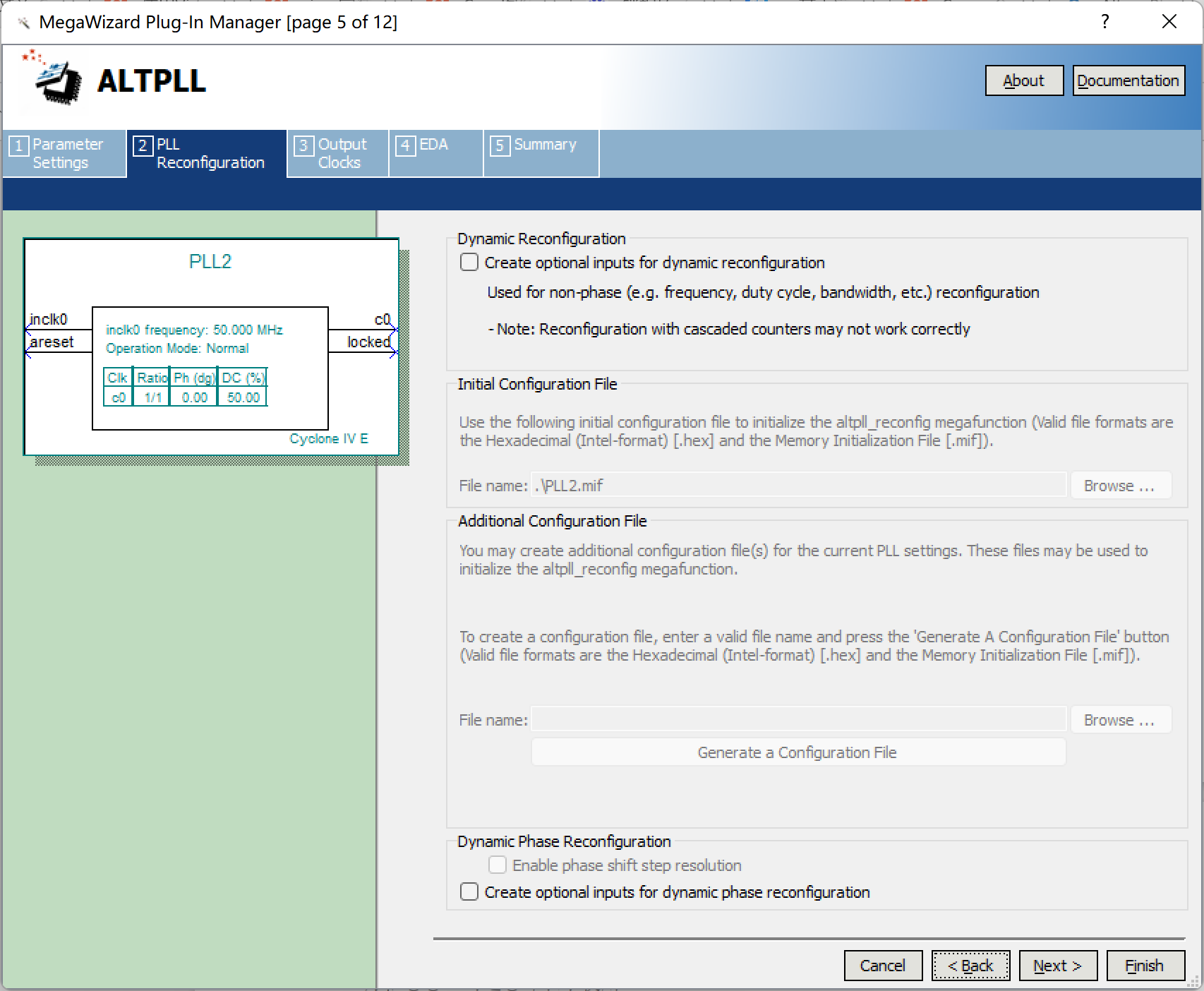

继续点击next

- 本界面为PLL重配置界面,博主也还没学到,所以也不选(其实前面说不选的都是因为博主也没用过,博主真的是初学者)

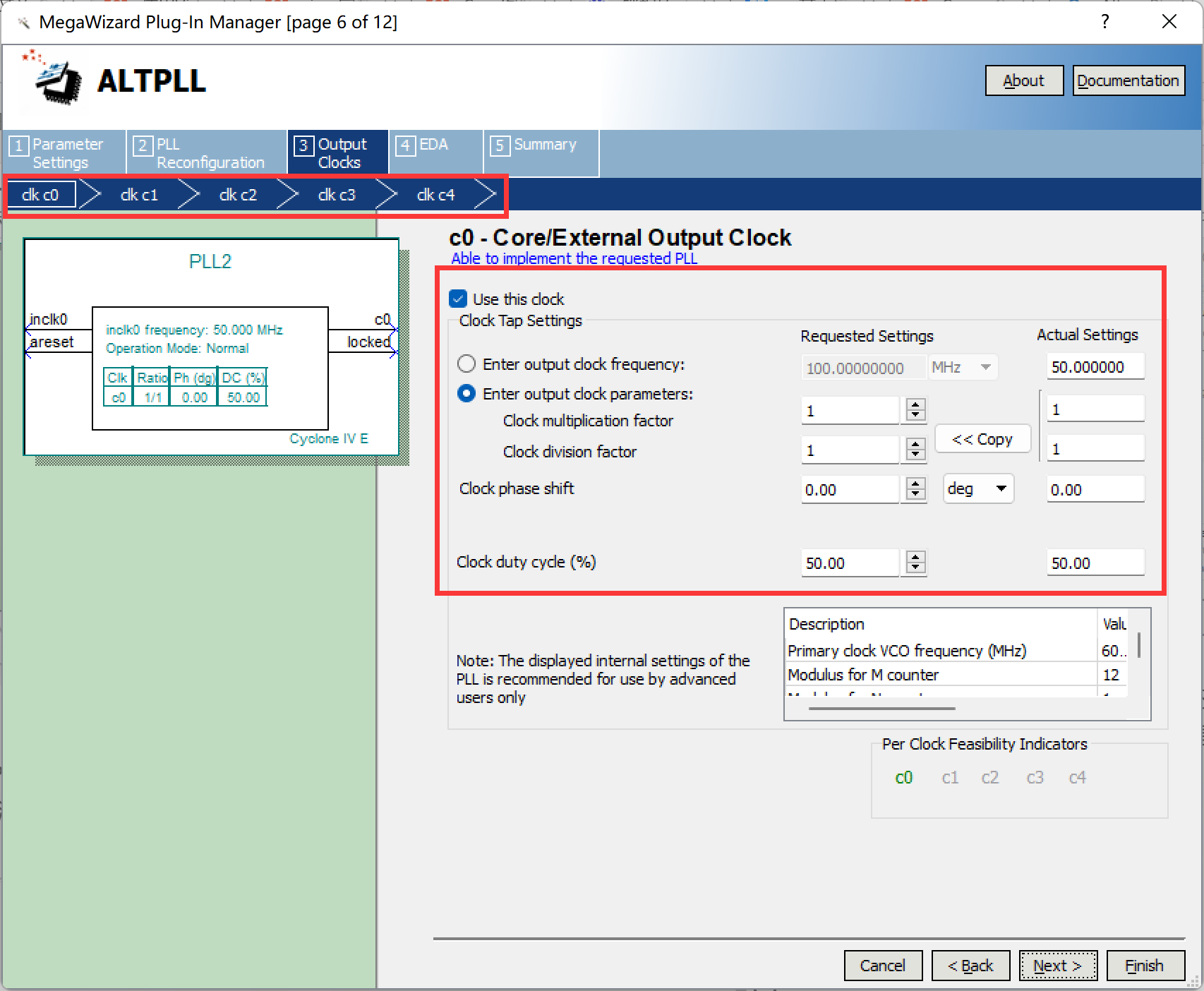

继续next

- 此界面为输出时钟信号配置

- 由最上可以看出,本开发板最多可设置五路PLL输出时钟

- 如图 我们可以选择手动输入所需时钟频率或者利用下面的参数进行频率配置

- clock phase shift则是用来设置时钟信号的相位(deg是单位,度的意思,下拉也可选择时间尺度)

- clock duty cycle则是用来设置时钟信号的占空比

大家按照自己需求设置即可

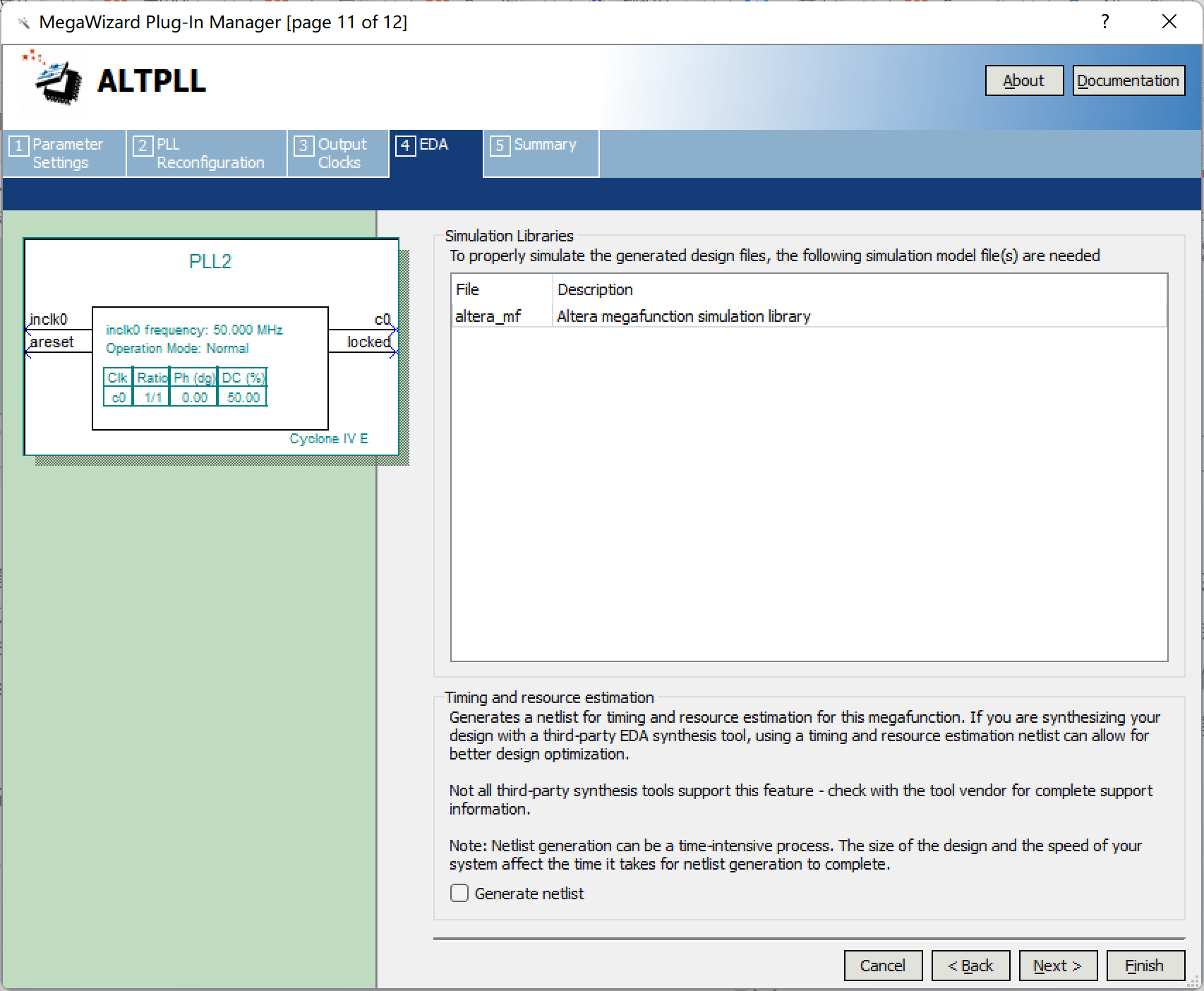

继续next

- 此选项的mf文件如果我们在后续仿真时采用联合仿真,则不需要管,如果采用do文件仿真,则需要添加此文件,我们不勾选

接着next

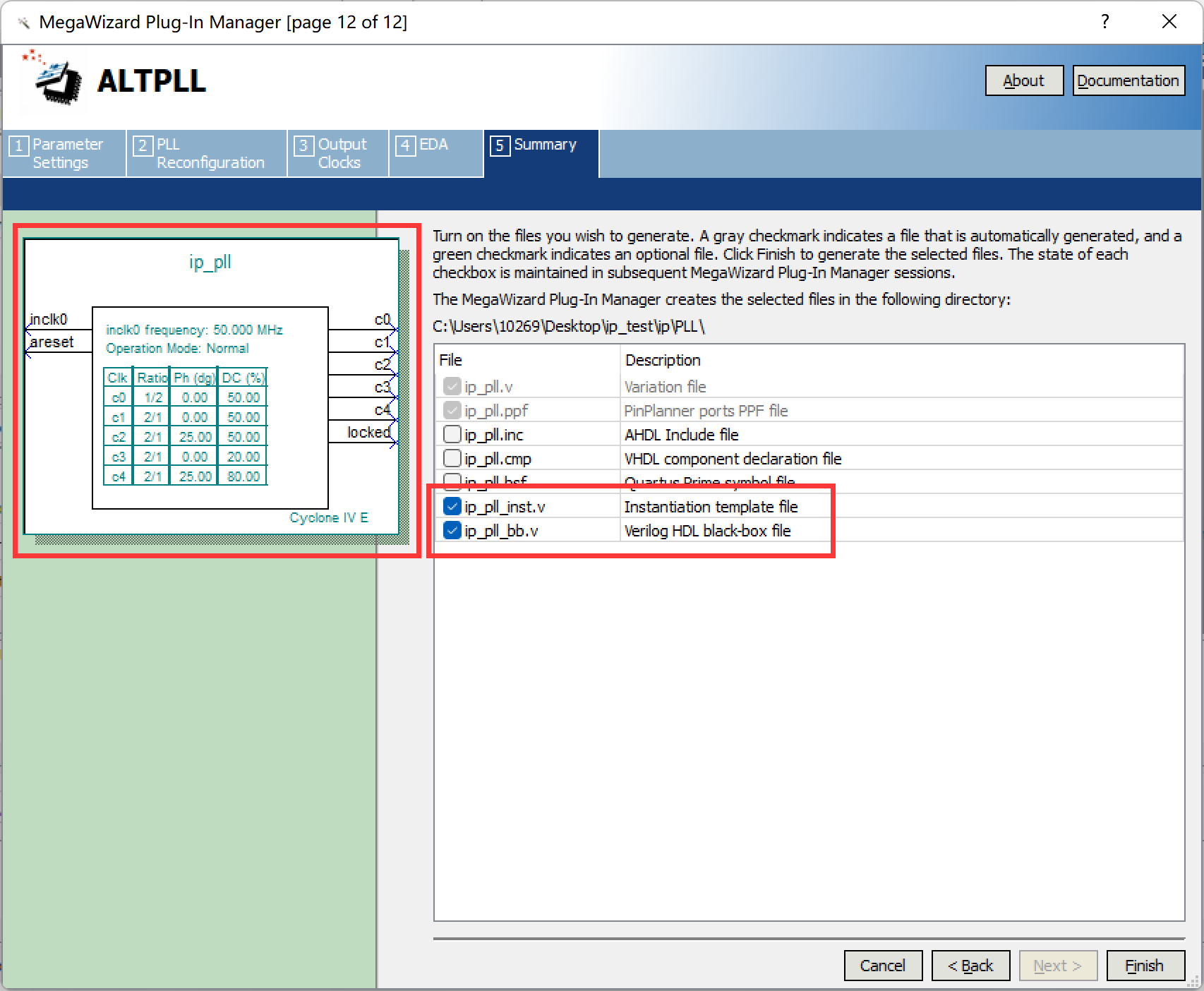

- 该界面即为总览界面,我们可以通过左上角检查自己的大致设置

- 文件生成选项默认勾选.v文件,上面的inst.v则是为我们提供了例化模板,便于我们例化,建议勾选

- 点击finish完成配置

四、编写测试代码

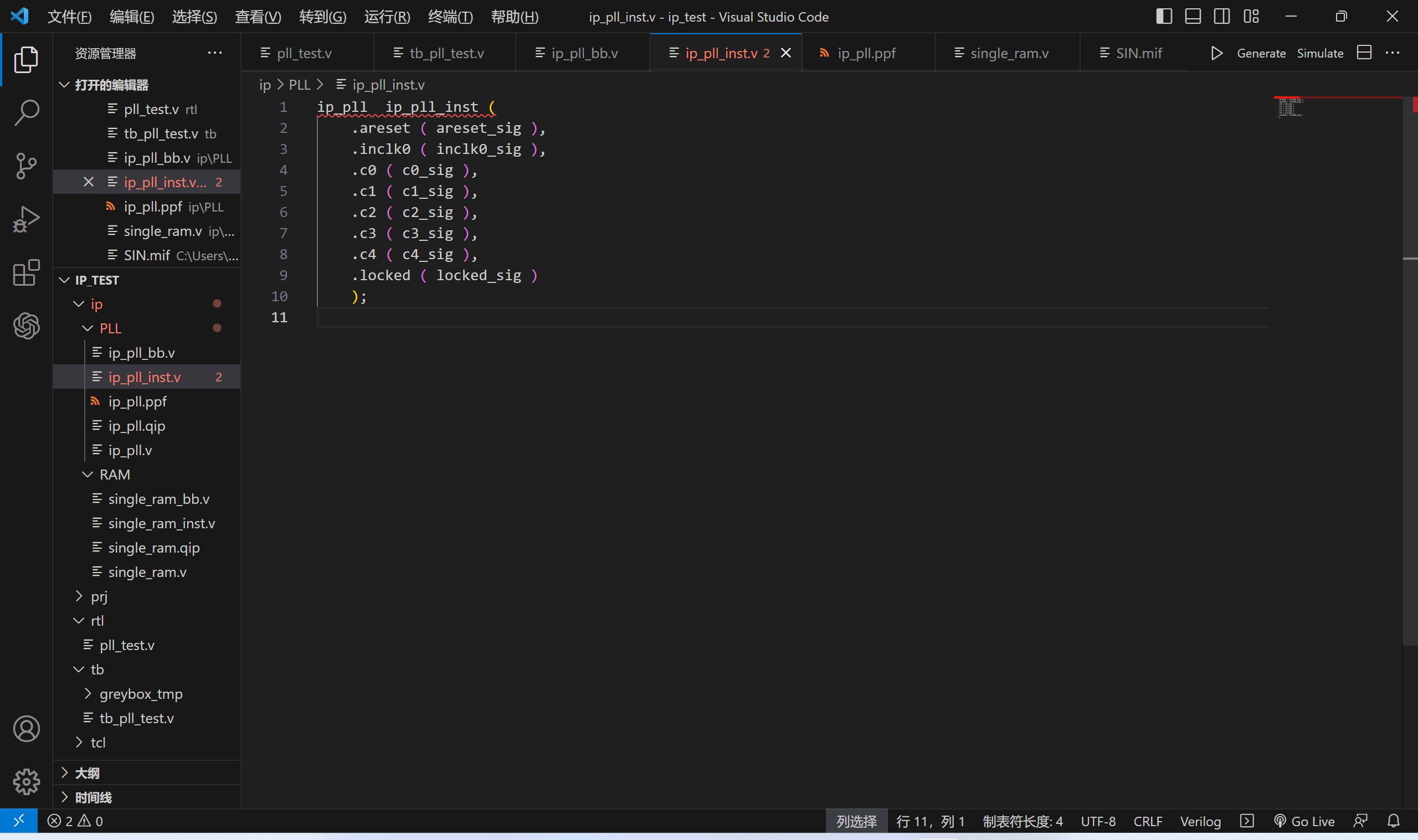

紧接着我们便可以用编译器打开quartus为我们生成的这些文件

- 可以看到inst.v就是quartus为我们生成的例化模板

新建test_ip.v文件和tb文件输入如下代码:

module test_ip(

input clk ,

input rst_n ,

output c0 ,

output c1 ,

output c2 ,

output c3 ,

output locked

);

pll pll_inst (

.areset ( ~rst_n ),

.inclk0 ( clk ),

.c0 ( c0 ),

.c1 ( c1 ),

.c2 ( c2 ),

.c3 ( c3 ),

.locked ( locked )

);

endmodule

`timescale 1ns/1ns

module test_tb();

reg tb_clk ;

reg tb_rst_n ;

wire tb_c0 ;

wire tb_c1 ;

wire tb_c2 ;

wire tb_c3 ;

wire tb_locked ;

parameter CYCLE = 20;

//模块例化

ip_test(

.clk (tb_clk ),

.rst_n (tb_rst_n ),

.c0 (tb_c0 ),

.c1 (tb_c1 ),

.c2 (tb_c2 ),

.c3 (tb_c3 ),

.locked (tb_locked )

);

initial begin

tb_clk = 1'b1;

tb_rst_n = 1'b1;

#(CYCLE*2);

tb_rst_n = 1'b0;

#(CYCLE*10);

tb_rst_n = 1'b1;

#(100*CYCLE);

$stop;

end

always #(CYCLE/2) tb_clk = ~tb_clk;

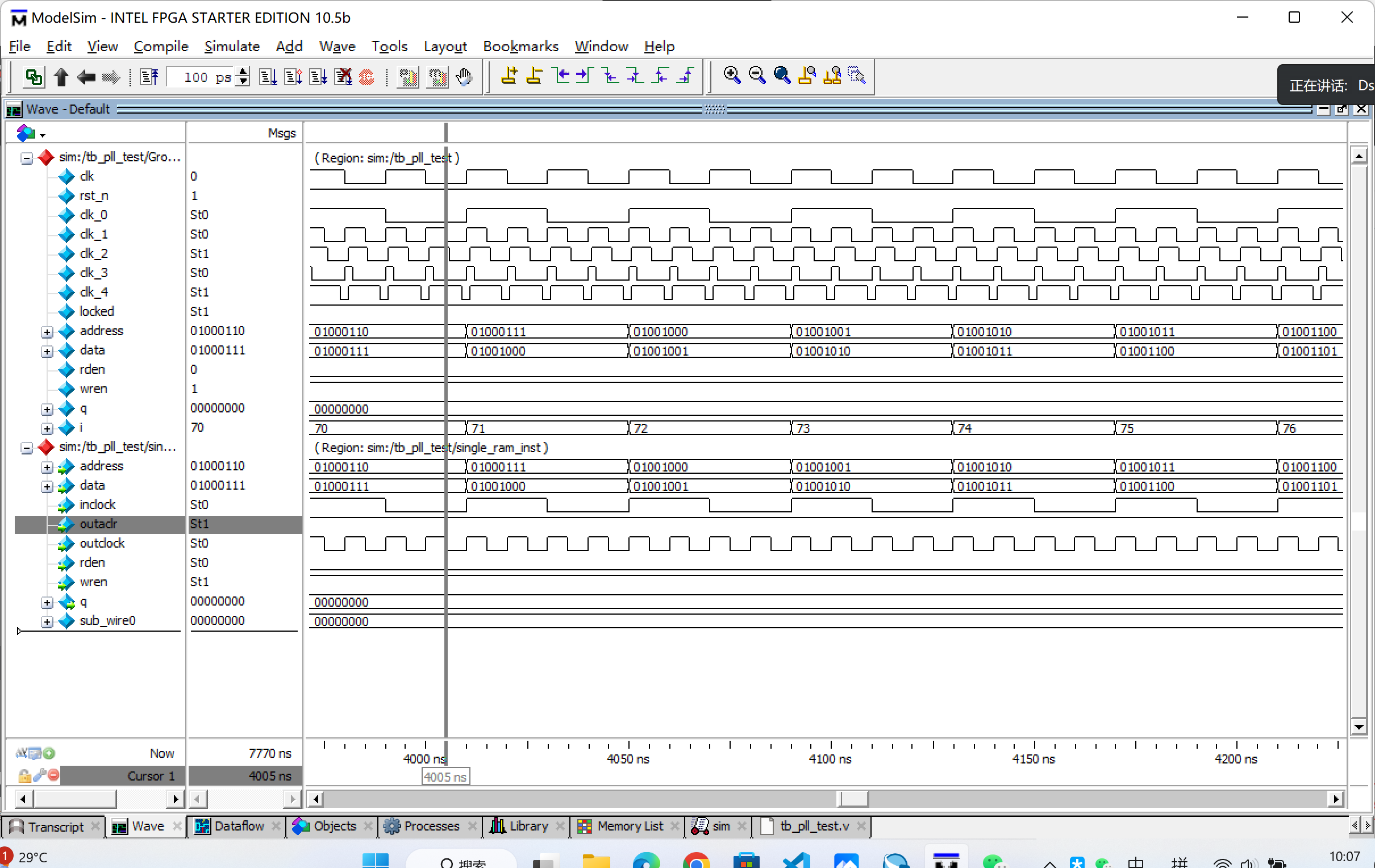

进入quartus 编译并进行仿真,仿真结果如下:

(后面为博主RAM IP核的学习,大家不用管,只看前面的时钟信号即可)

可以看出PLL为我们输出了稳定的时钟信号

五、总结

PLL IP核的调用只是一个步骤的练习,相信大家跟着博主走一遍也就会进行调用了,但是其中的许多细节,博主自己也并未学习到,比如:模式选择,重配置等等,大家可以通过官方文档进行更细致的学习。

本篇博客到此结束,如有错误还请各位指正,谢谢!

这篇关于FPGA学习——Altera IP核调用之PLL篇的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!