altera专题

Xilinx系FPGA学习笔记(四)VIO、ISSP(Altera)及串口学习

系列文章目录 文章目录 系列文章目录VIO(Vivado)ISSP(Altera)串口学习FPGA串口发送FPGA串口接收 VIO(Vivado) VIO 的全称叫 Virtual Input/Output,建立一个虚拟的输入/输出信号,可以对需要调试的模块的输出信号的数值进行在线的查看,以及模拟一些信号输给需要调试模块,方便调试查找问题和验证模块的实际上板工作的正确

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。本文介绍的实例可方便扩展到具有类似接口格式的其他高速数据转换器设计。 1.概述 ADS4249是一款双通道、14位、250MSPS ADC,具有双总线、字节级数字接口。ADS4249接口示例适用于许多TI高速ADC,包

FPGA学习笔记之Altera FPGA使用JIC文件配置固化教程(转)

1,打开希望固化的FPGA设计工程,这里我直接打开按键消抖这节课的工程。 2,在quartus ii软件中点击File—>Convert Programming Files,如下图所示: 3,在弹出的窗口中,Programming file type 选择JTAG Indirect Configuration File(.jic),Mode选择Active Serial,Configura

使用Modelsim独立仿真Altera及Xilinx IP核

使用Modelsim进行仿真非常方便,可以通过.do文件完成一些重复性的界面操作,但是使用Modelsim仿真IP核的时候经常会因为没有库文件的问题而纠结,网上不乏一些相关教程,但是在使用过程中总会遇到这样那样的问题,于是我痛定思痛,决定彻底解决这个问题,为了帮助大家解决相同的烦恼,决定写这篇文档,帮助大家避免走我曾走过的弯路,这也是我的第一篇教程,希望能帮到大家! 1 软件环境

Win10 Altera USB Blaster Driver 试图将驱动程序添加到存储区时遇到问题

按住 Shift 点击重启,重启 Win10 疑难解答 高级启动选项 F7 禁用驱动程序强制签名 进入系统,重新安装驱动

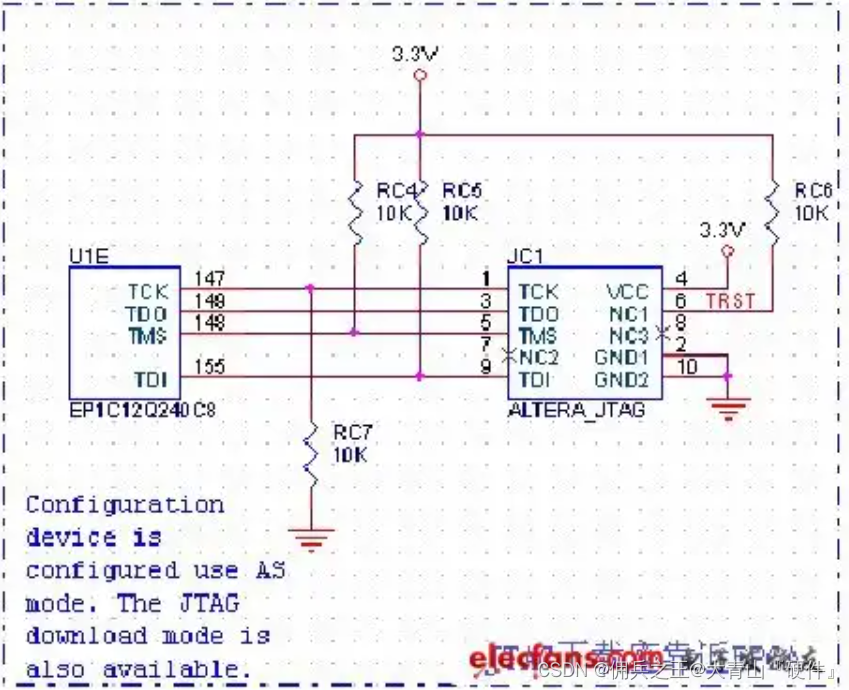

Altera的JTAG电路下载模块为何上下拉电阻,不可不知的秘密

一、FPGA背景信息 当前的FPGA市场上有国际和国产两大体系,国际排名,一直很稳定,国际上前三名Xilinx、Altera、Lattice,国内FPG厂商也在填补空白,低端、中低端市场上发力,替代潮流已在兴起,目前国内前五,分别是京威齐力、安路科技、广州高云、复旦微电子、西安智多晶,国货当自强,真的很厉害。 FPGA随着人工智能、大数据、云计算、数据中心而越发收到重视,对于我们硬件工程师来说

【INTEL(ALTERA)】为什么在使用 .ipx 时,nios2-bsp 无法查找 .sopcinfo 文件?

目录 说明 解决方法 说明 由于 Quartus® Prime Pro 软件版本 17.0 出现问题,使用 .ipx 文件创建多个自定义组件时,.sopcinfo 文件在qsys_name文件夹中生成,而不是在项目目录文件夹中生成。 当您在Nios II软件构建工具 中构建Nios® II应用程序和 bsp 项目时,当您构建应用程序项目时会看到错误。 错误: 信息:编译 。。

【INTEL(ALTERA)】Nios® II EDS 是否在 Windows 10 上受支持?

目录 说明 解决方法 说明 在 readme.txt 中提到 Windows 10 不支持Nios II EDS 标准版。/content/dam/support/us/en/programmable/kdb/others/download/os-support/readme-qp171.txt 但是,在Nios II版本中,它得到了支持。https://www.altera.co

【INTEL(ALTERA)】make: nios2-swexample-create:未找到命令

目录 说明 解决方法 说明 由于外部内存接口英特尔® Stratix® 10 FPGA IP 出现问题,如果在 Windows 平台上使用英特尔® Quartus® Prime Pro Edition Software v20.4 或更早版本的"使用软Nios处理器进行片上调试"选项,编译Nios® II 片上处理器调试软件时可能会出现错误。 让 mrproper make

【INTEL(ALTERA)】为什么 F-Tile DisplayPort FPGA IP 设计示例无法通过高比特率 3 (HBR3) 的 RX 链路调训?

目录 说明 解决方法 说明 由于 Quartus® Prime Pro Edition 软件版本 v23.3 和 v23.4 生成的 F-Tile DisplayPort FPGA IP 设计示例中存在问题,您可能会在 HBR3 上观察到 RX 链路训练失败。 解决方法 要在这些软件版本中变通解决此问题,请使用以下 RxEQ 参数编辑项目 Quartus 设置文件 (.qsf)

【INTEL(ALTERA)】编程了错误的加密密钥后,为什么 Agilex™ 7 设备无法恢复?

目录 说明 解决方法 说明 如果您意外地对加密密钥编程错误,Agilex™ 7 设备将无法恢复。这是此设备的预期行为。 解决方法 此错误没有恢复流程。使用 Agilex™ 7 设计安全功能时,请注意加密密钥并仔细编程。

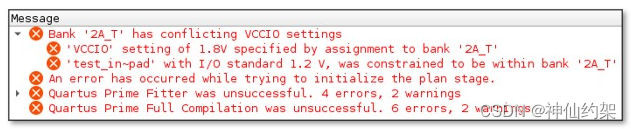

【INTEL(ALTERA)】Quartus® 软件 Pin Planner 中 Agilex™ 5 FPGA的 HSIO 库可以选择 1.8V VCCIO?

目录 说明 解决方法 说明 由于 Quartus® Prime Pro Edition 软件版本 24.1 存在一个问题,Quartus® 软件 Pin Planner 中的 I/O 组属性 GUI 允许用户选择 1.8V 作为 HSIO 银行位置的 VCCIO。HSIO bank 支持的有效 VCCIO 电压仅为 1.0V、1.05V、1.1V、1.2V 和 1.3V。 如果将任何

【INTEL(ALTERA)】Nios® II无法使用基于 Ubuntu 18.04.5 的 WSL 进行构建

现象 在使用 Ubuntu 18.04.5 构建 WSL 的Nios® II处理器时,任何英特尔® Quartus® Prime 软件版本都可能会看到此问题。 原因 这是因为在 Nios® II Command Shell 中运行命令 “wslpath -u .”时返回值不同。 正常工作:命令返回”。故障:命令返回“wslpath:”。”

altera 防止reg/wire 优化

转载:# 关于SignalTap中的节点查找不到的问题_signaltap找不到信号-CSDN博客 关于SignalTap中的节点查找不到的问题 在选择需要查看的信号节点时,有一个信号节点,我翻遍了所有的模块,始终未能看到它的影子,然后上网查了一下,找到了问题所在。 因为在使用quartus编译综合时,某些信号会被优化掉,就会导致在查找此信号节点时,会发现找不见。 解决方法: 1.对

【INTEL(ALTERA)】为什么 F-Tile Serial Lite IV 工具包在链路初始化期间无法启用内部串行环回?

说明 F-Tile Serial Lite IV 工具包存在一个问题,即内部串行环回启用失败,并在执行链路初始化时输出不正确的寄存器值。这是因为我们在内部更改为 demo_jtag 在系统重置过程中检查 tx_pll_locked 和 rx_cdr_locked 状态。但完成后没有把它改回 phy_jtag 。 解决方法 要变通解决此问题,您需要按照以下步骤操作: 点击 “断言系统重置

【INTEL(ALTERA)】采用 JTAG 频率为 24MHz 或 16Mhz 的非流水线Nios® V/m 处理器,niosv-download 失败

说明 在英特尔® Quartus® Prime Pro Edition 软件 23.3 版及更高版本中将 Nios® V 处理器软件下载到非流水线Nios® V/m 处理器时,可能会出现此问题。 这是由于处理器限制,仅影响非流水线Nios® V/m 处理器。 以下其他处理器不受此限制的影响: 管道式 Nios® V/m 处理器Nios® V/g 处理器 解决方法 要变通解决此问题,

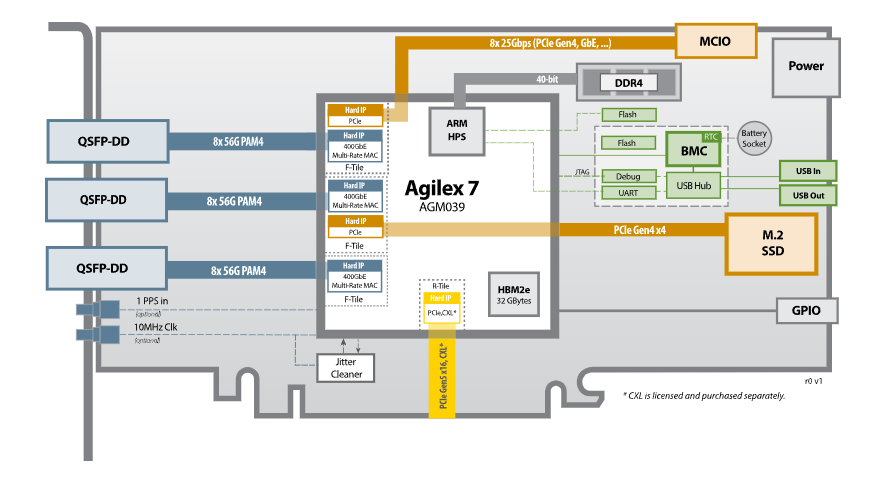

产品推荐 | BittWare基于Altera Agilex“M FPGA的lA-860m加速卡

01 产品概述 BittWare的lA-860m是一款Altera Agilex“M系列FPGA卡,针对吞吐量和内存密集型应用进行了优化。M 系列 FPGA 具有广泛的内存层次结构,包括集成高带宽存储器 (HBM2e) 和硬内存片上网络 (NoC),以最大限度地提高内存带宽。lA-860m 卡利用 Agilex 芯片独特的平铺架构提供 l/0 和内存的平衡,包括 QSFP-DD、支持 CXL 的

FIFO使用方法(ALTERA)

本文引用自Suinchang 《关于ALTERA提供的FIFO核使用原理》 ALTERA提供了LPM_FIFO参数宏模块,可以在代码中例化使用。 FIFO有两种工作模式:(1)SCFIFO,(2)DCFIFO 其中SCFIFO指读写用一个时钟进行同步,可以支持同时读写的功能。 其中DCFIFO指读写使用不同的时钟进行同步,这在设计多时钟系统中相当有用,可用于不同时

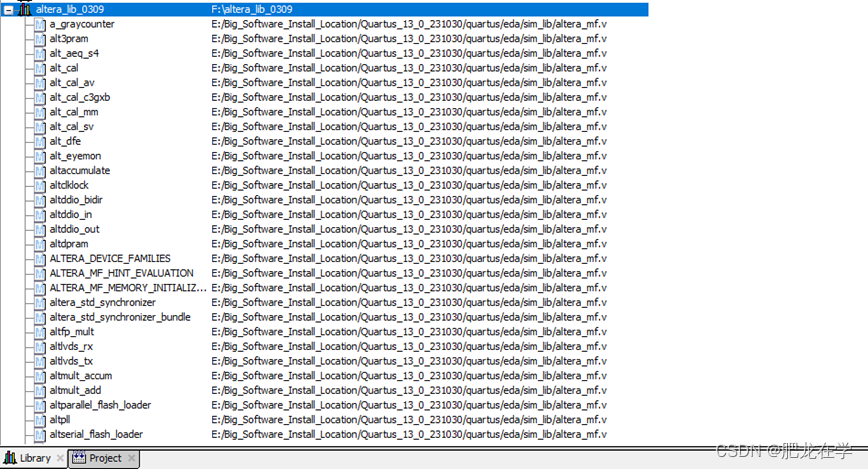

Modelsim 如何创建Altera库

以 (altera_mf)为例进行介绍 1、点击File,创建新的Libiary,弹出新建库的窗口,我们选择第三项“a new library and a logical mapping to it”。Library Name输入库名称,Library Physival Name输入库的地址,然后点击OK。 2、然后点击Project栏, 右键空白处,会弹出 3、点击Existing Fil

最新消息:英特尔宣布成立全新独立运营的FPGA公司——Altera

今天,英特尔宣布成立全新独立运营的FPGA公司——Altera(2015年6月Intel以 167 亿美元的价格,收购FPGA厂商Altera)。首席执行官Sandra Rivera和首席运营官Shannon Poulin分享展示其在超过550亿美元的市场中保持领先性的战略规划,强调将通过打造集成AI功能的FPGA等举措,进一步丰富公司的产品组合,同时亦表明将持续助力客户应对不断增加的挑战。会

【工程源码】Altera FPGA 开启引脚片上上拉电阻功能

本文和设计代码由FPGA爱好者小梅哥编写,未经作者许可,本文仅允许网络论坛复制转载,且转载时请标明原作者。 Cyclone IV E FPGA的通用输入输出管脚都支持内部弱上拉电阻,但是时钟输入脚不支持。所以,当需要上拉电阻的信号(如本例中的矩阵键盘Row信号和IIC协议中的SDA、SCL信号)连接到了FPGA的通用输入输出管脚上,在一些要求不高的场合,就可以使用片上上拉电阻来为这些信号设

【INTEL(ALTERA)】错误 (293007): 当前模块quartus_ipgenerate意外退出代码 0 终止。这可能是因为某些系统资源已耗尽

说明 由于 Windows* 操作系统的限制,当您的 英特尔® Quartus® Prime Pro Edition 软件项目目录的路径长度超过 260 个字符时,您可能会看到此错误消息。 解决方法 要变通解决此问题,请执行以下操作之一 将新的驱动器号映射到路径中的较低目录,以缩短路径长度。共享网络路径可以映射为 Windows 操作系统上的驱动器。 例如使用Z:C:\longpath

【INTEL(ALTERA)】带有浮点单元 (FPU) Nios® V/g 处理器在 英特尔® Cyclone10 GX 设备中执行不正确的浮点运算

说明 由于 英特尔® Quartus® Prime Pro Edition 软件版本 23.3 存在一个问题,当使用 Nios® V/g 处理器并在 英特尔® Cyclone® 10 GX 设备中启用 FPU 时,浮点运算无法按预期进行。 Nios® V/g 处理器 – 启用浮点单元 解决方法 请勿在 英特尔® Cyclone®Nios 10 GX 设备中启用 V/g 中的硬件

【INTEL(ALTERA)】如何在 Windows 操作系统上设置 Design Space Explorer II 远程 SSH 场

说明 从英特尔® Quartus® Prime Pro Edition 软件 22.1 版本开始,您可以选择使用 Windows OpenSSH 服务器设置 Design Space Explorer II (DSE II)。 解决方法 1.让 DSE II 与 OpenSSH 协同工作的第一步是 安装 OpenSSH。应在远程主机上安装 OpenSSH 服务器服务。请参阅 Micro

【INTEL(ALTERA)】为什么Nios® V 应用程序项目构建失败,并且观察到“找不到 -lstdc++”消息?

说明 由于 xPack GNU RISC-V 嵌入式 GCC v10.1.0-1.1 工具链 (Windows Build) 中缺少多lib arch/abi-to-directory 映射,在 Windows 中使用命令“make -C<Application project build directory>” 在 Windows 中构建Nios® V/m 处理器英特尔 FPGA IP设计应用