本文主要是介绍【INTEL(ALTERA)】Quartus® 软件 Pin Planner 中 Agilex™ 5 FPGA的 HSIO 库可以选择 1.8V VCCIO?,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

说明

解决方法

说明

由于 Quartus® Prime Pro Edition 软件版本 24.1 存在一个问题,Quartus® 软件 Pin Planner 中的 I/O 组属性 GUI 允许用户选择 1.8V 作为 HSIO 银行位置的 VCCIO。HSIO bank 支持的有效 VCCIO 电压仅为 1.0V、1.05V、1.1V、1.2V 和 1.3V。

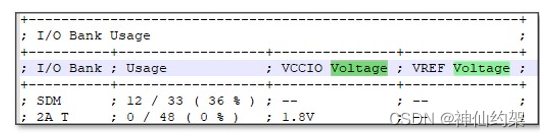

如果将任何未使用的 HSIO 组的 VCCIO 分配到 1.8V,Quartus® fitter 报告将错误地反映该未使用组的 1.8V VCCIO 电压。

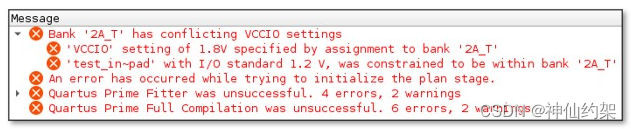

如果使用的 HSIO 组被分配到 1.8V,Quartus® Prime 软件将检测在使用的 HSIO 库中分配的 VCCIO 与为 HSIO 引脚选择的有效 I/O 标准的 VCCIO 之间的冲突。Quartus® Prime 软件将显示类似于以下示例的错误:

解决方法

要变通解决此问题,请选择 HSIO 银行支持的有效 VCCIO 电压,如《Agilex™ 5 通用 I/O 用户指南》中所述。该问题计划在 Quartus® Prime Pro Edition 软件的未来版本中修复。

这篇关于【INTEL(ALTERA)】Quartus® 软件 Pin Planner 中 Agilex™ 5 FPGA的 HSIO 库可以选择 1.8V VCCIO?的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![C#实战|大乐透选号器[6]:实现实时显示已选择的红蓝球数量](https://i-blog.csdnimg.cn/direct/cda2638386c64e8d80479ab11fcb14a9.png)