quartus专题

【乌拉喵.教程】编写TestBench,quartus与modelsim时序仿真

最近将多年来收集到的教学视频、国内外图书、源码等整理整合拿出来,涉及arm、Linux、python、信号完整性、FPGA、DSP、算法、stm32、单片机、制图、电子模块、kali、出版社图书等。资料目前约1.5TB+。详情请见: https://www.bilibili.com/read/cv20701606 昨天搜了一圈,也没整会这个仿真,今天在武梦梦的指导下修改了testbench,

关于在Quartus II和ModelSim中进行FPGA仿真报错的问题

今天晚上在用Quartus II设计好FPGA代码后,尝试在ModelSim中进行前仿真以验证设计功能的时候,总是报错。错误状态如下: Can’t launch the ModelSim-Altera software – the path to the location of the executables for the ModelSim-Altera software were not s

解决Quartus Prime 20.1 Lite Edition不能仿真的问题

安装时默认安装,不要安装最后一个ModelSim(付费组件,会导致免费的ModelSim Starter不可用,一般说不能仿真的大多是这个问题),Lite版本可以编译仿真10000行以下代码,已经够用了。 Quartus Prime Lite 20.1 下载链接:https://download.altera.com/akdlm/software/acdsinst/20.1std/711/ib_

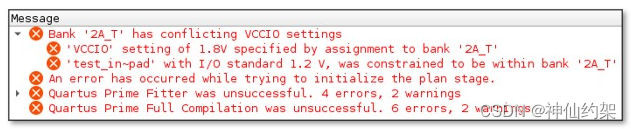

【INTEL(ALTERA)】Quartus® 软件 Pin Planner 中 Agilex™ 5 FPGA的 HSIO 库可以选择 1.8V VCCIO?

目录 说明 解决方法 说明 由于 Quartus® Prime Pro Edition 软件版本 24.1 存在一个问题,Quartus® 软件 Pin Planner 中的 I/O 组属性 GUI 允许用户选择 1.8V 作为 HSIO 银行位置的 VCCIO。HSIO bank 支持的有效 VCCIO 电压仅为 1.0V、1.05V、1.1V、1.2V 和 1.3V。 如果将任何

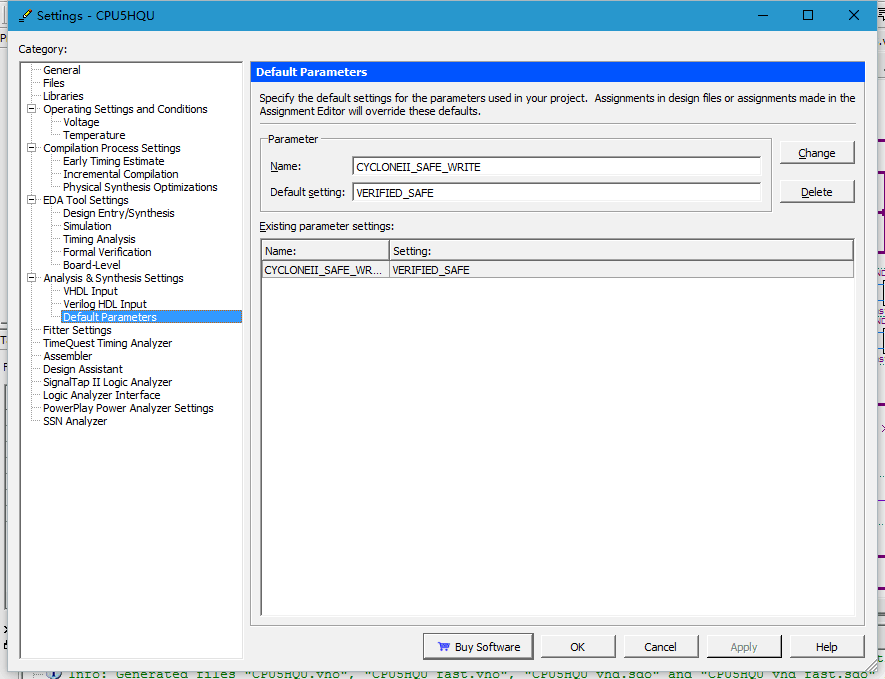

Quartus TCL

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-qpp-scripting.pdf https://www.intel.com/content/www/us/en/programmable/documentation/sbv1513989262284.html 使用JTAG模式下载到F

Quartus II 版本问题解决方案

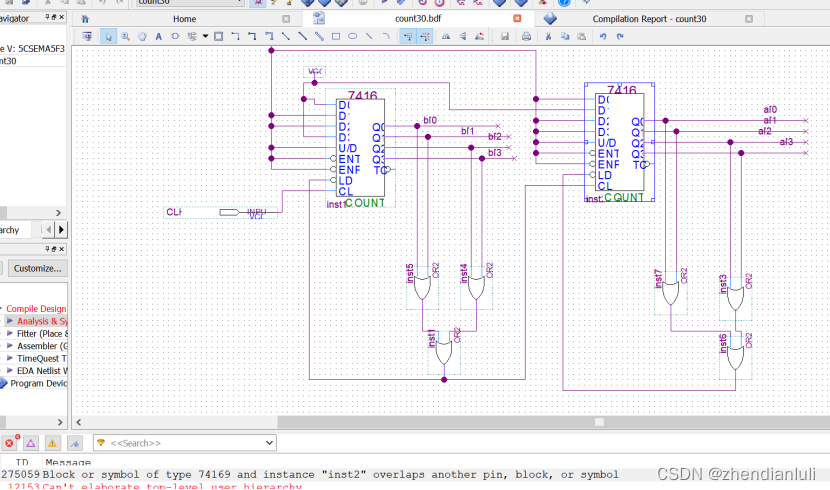

问题1: 在做一个项目时,发现该项目(主要才用原理图设计)可以在Quartus 9.0版本上编辑,但是无法编译通过,表现在会提示一个弹窗的错误,选择no可以继续进行,结束时也没有提示error,但是并没有正常编译通过。因此也就无法进行modelsim仿真,表现为每一次modelsim的结果都是一样的。 解决方案: 此时将整个项目关闭,用11.0版本打开,不要修改,直接编译就可以通

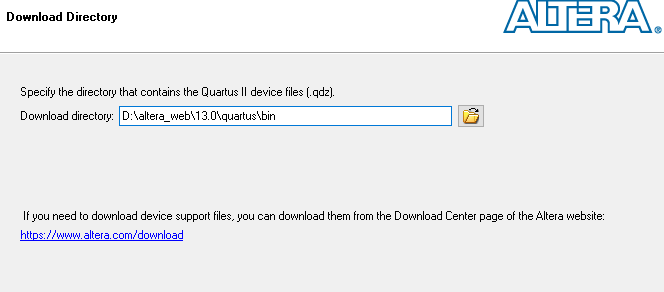

Quartus 13.0安装教程

1.首先,进入ALTERA官网这里是网址 2.选择合适的版本,这里我按器件来选。选择的是Cyclone II芯片对应的软件版本。 3.选择下载方式,以及所需的文件。 4.接下来会需要登录你的ALTERA账号。如果没有的,用邮箱注册一下就好,很方便的。 5.如果使用直接下载的话,下载后会是几个分离的文件。点击QuartusSetupWeb-13.0.0.156进行安装。 6.安

Quartus Cyclone I II III IVE 器件型号

玩耍了一个 EP2 型号的开发板,发现 安装的quartus13 没有Cyclone II 型号,经过探索发现了是版本不对。 https://www.intel.com/content/www/us/en/software-kit/711920/intel-quartus-ii-subscription-edition-design-software-version-13-0sp1-for-wi

Quartus ii 调用除法器IP核

TOOLS->MEGA WIZARD->CREATE NEW MEGA FUNCTION-> 右邊 設定OUTPUT FILE ->左邊 選DIVIDE_LPM 或 ALTFP_DIV 然後設定參數, 就可以了 这里有很多ip核都可以调用,比较方便。节省了大量的时间和资源。 以下是 DIVIDE_LPM 範例 8BIT/8BIT 結果 // synopsys translate_off`

基于FPGA的数字电子钟VHDL代码Quartus仿真

名称:基于FPGA的数字电子钟VHDL代码Quartus仿真(文末获取) 软件:Quartus 语言:VHDL 代码功能: 数字电子钟 1)设计一个能显示秒、分、时的24小时数字钟 2)用数码管显示出时,分,秒,复位显示00:00:00 3)通过按键可对时,分,秒进行设置 1. 工程文件 2. 程序文件 3. 程序编译 4. RTL图

基于FPGA的DDS波形发生器VHDL代码Quartus仿真

名称:基于FPGA的DDS波形发生器VHDL代码Quartus仿真(文末获取) 软件:Quartus 语言:VHDL 代码功能: DDS波形发生器VHDL 1、可以输出正弦波、方波、三角波 2、可以控制输出波形的频率 DDS波形发生器原理 1. 工程文件 2. 程序文件 ROM IP核 3. 程序编译 4. RTL图

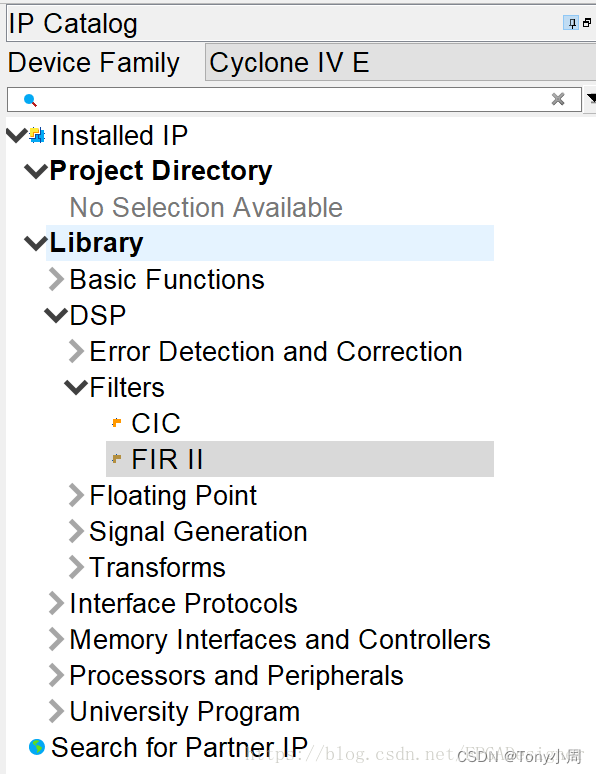

FPGA Quartus IP核 打开使用

两种Quartus版本下的IP核,从使用者的角度来看仅仅是配置界面不同,在参数设置和使用方法上基本一致。本文以“MegaWizard Plug-In Manager”中的FIR Compiler IP核使用为例。 Quartus的FIR IP核属于收费IP,如果是个人学习使用需要对IP核单独破解。在Quartus的破解licence文件中找到下段代码,在licence最后复制粘贴一份,将“FEAT

Quartus II仿真出现错误

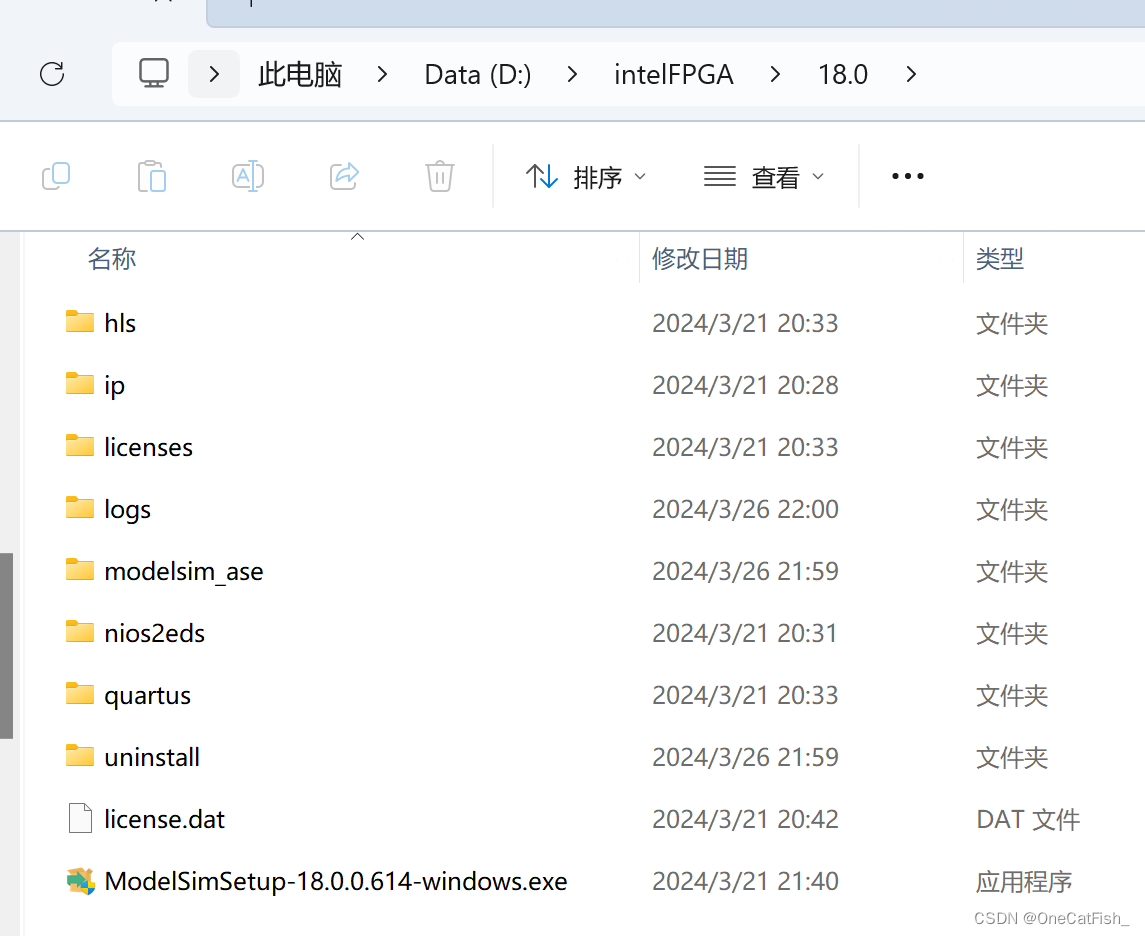

ModelSim executable not found in D:/intelFPGA/18.0/quartus/bin64/modelsim_ase/win32aloem/ Error. 找不到modelsim地址,原来是我下载了.exe,但没有双击启动安装ase文件夹呀!!!!晕,服了我自己

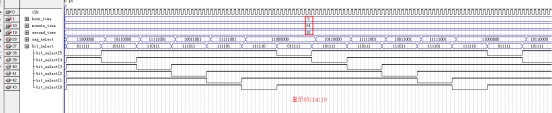

多模爆闪灯流水灯8种模式Verilog代码Quartus仿真

名称:多模爆闪灯流水灯8种模式Verilog代码Quartus仿真(文末获取) 软件:Quartus 语言:Verilog 代码功能: 多模爆闪灯← 应用于警车、岗亭、道路维修等场合,能够通过按键切换8种不同的工作模式。← 1. 工程文件 2. 程序文件 3. 程序编译 4. RTL图 5. Testbench

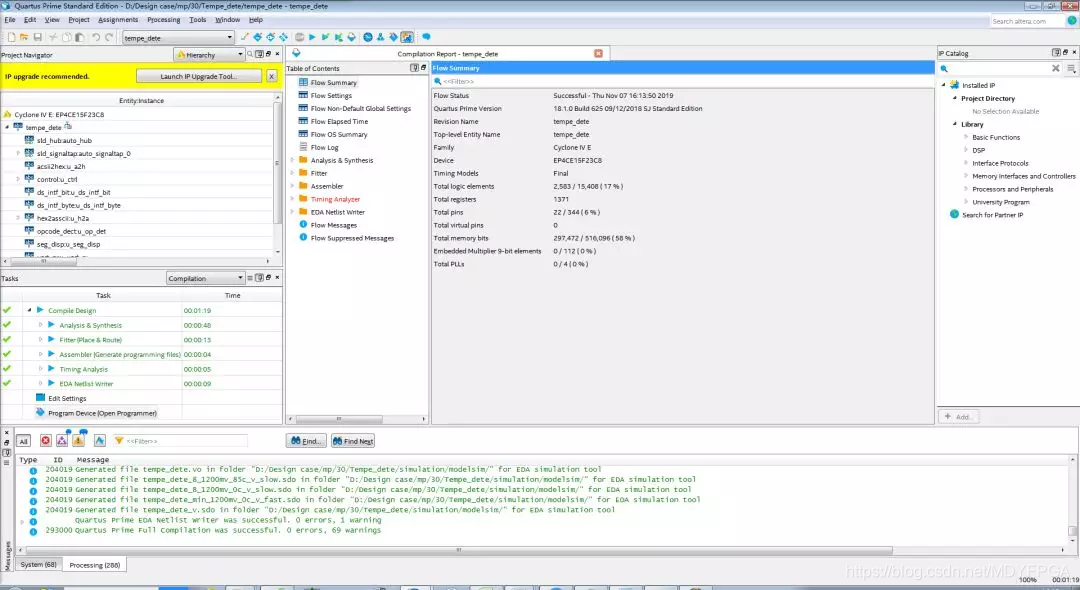

quartus Ⅱ 12.1 使用教程(7) vga显示测试

开发板使用的是EP4CE15F23C8,软件使用的是quartus 12.1 ,工程主要使用vga显示方格 行计数 //hsync计数always@(posedge clk_148M or negedge i_rst_n)beginif(i_rst_n == 1'b0)hsync_cnt <= 12'd0;else if(hsync_cnt == H_TOTAL -12'd1)hsync_c

quartus Ⅱ 12.1 使用教程(6) ROM 测试

开发板使用的是EP4CE15F23C8,软件使用的是quartus 12.1 ,工程主要读ROM内的数据 调用ROM IP Tools->MegaWizard Plug-In Manager 点击Next 选择ROM 数据宽度8bits,数据深度32words,点击Next 点击Next 点击Browse,选择ROM初始化文件 选择r

quartus Ⅱ 12.1 使用教程(5) eeprom 读写测试

开发板使用的是EP4CE15F23C8,软件使用的是quartus 12.1 ,工程主要是对24c04进行读写 eeprom顶层 `timescale 1ns / 1ps//// Module Name: eeprom_top // Function: write and read eeprom using I2C bus//module eeprom_top(input

全新英特尔® Quartus® Prime,带你全速前进!

更多精彩内容,请微信搜索“FPGAer俱乐部”关注我们 英特尔® Quartus® Prime 软件 v18.0 已新鲜出炉,可快速完成编译、分析和重新配置,所有支持我们的用户先睹为快吧! 突破性的英特尔® Quartus® Prime 设计软件,在性能、效率和可用性三大重要方面进行了华丽升级,提供行业领先的易用性和时效性。全新的并发分析特性和 Stratix 10 器件快速重

Quartus 曼彻斯特码 CRC校验

VHDL 曼彻斯特编解码 曼彻斯特码 曼彻斯特码,即曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从低到高跳变表示“1”,从高到低跳变表示“0”。 说明 最近完成了一个串行通信的项目,采用光纤作为物理层材料,F

【INTEL(ALTERA)】错误 (293007): 当前模块quartus_ipgenerate意外退出代码 0 终止。这可能是因为某些系统资源已耗尽

说明 由于 Windows* 操作系统的限制,当您的 英特尔® Quartus® Prime Pro Edition 软件项目目录的路径长度超过 260 个字符时,您可能会看到此错误消息。 解决方法 要变通解决此问题,请执行以下操作之一 将新的驱动器号映射到路径中的较低目录,以缩短路径长度。共享网络路径可以映射为 Windows 操作系统上的驱动器。 例如使用Z:C:\longpath

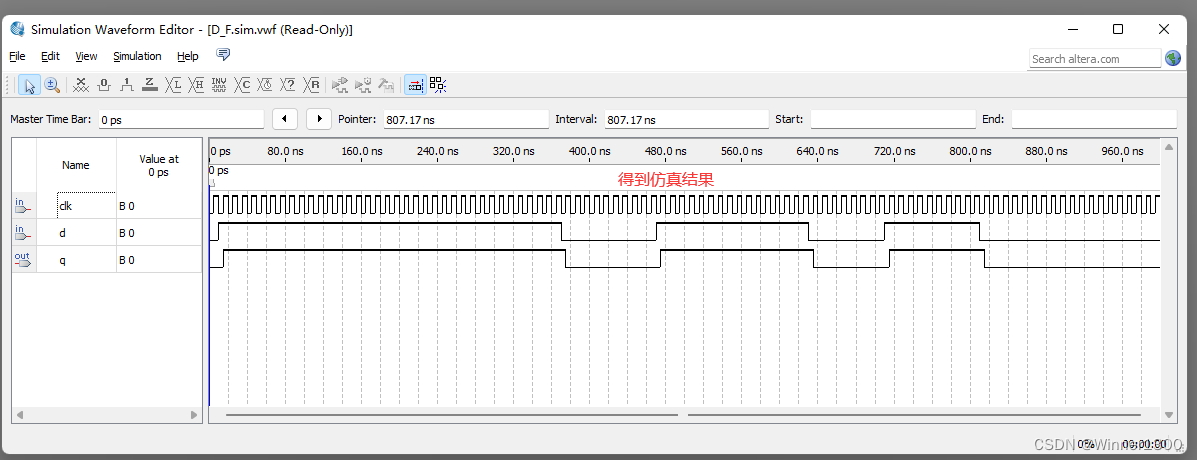

EDA quartus自带仿真工具仿真

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 EDA quartus自带仿真工具仿真 前言一、打开自带工具1.新建仿真波形文件 二、使用步骤1.设置输入信号2.运行仿真 总结 ) 前言 有的同学利用modelsim仿真有困难,写写测试文件不会写怎么办,可以使用quartus 自带的仿真工具仿真,最高版本支持到13.0版本,更高版本的没有仿真模块。

【数字系统】LED动态显示模块设计:数据输入/动态显示/按键信号转换 Quartus II 环境/Verilog HDL语言/编程+仿真+开发板/FPGA/CPLD/EDA

一、 实验目的 1. 学习理解LED动态显示的工作原理 2. 进一步掌握Verilog HDL层次化的设计方法。 3. 掌握Verilog HDL行为级描述与结构化描述方法。 4. 显示数值的数据输入模块、数据动态显示模块、信息可调整的动态显示顶层模块的设计与仿真。 二、 实验过程步骤 1、设计模块1:显示数值的数据输入display_decode a.模块功能要求

七段数码管、点阵以及按键开关的使用和编程(使用quartus)

其原理如图 数码管的具体使用 根据其管理图比如说我想点亮显示一个3,我只需要把a、b、c、d、g设置成高电平,把其余设置成低电平即可。 效果图如下 以后所用的译码代码如下: p4:process(num)--num为要显示的数字、abc为段选beginif(num=0) thenabc<="0000001";elsif(num=1) thenabc<="100111

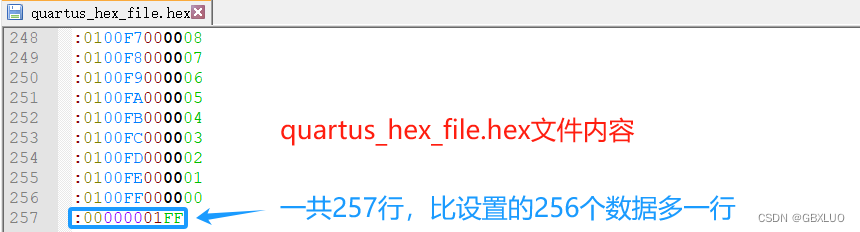

Quartus IP 之mif与hex文件创建与使用

一、mif与hex概述 ROM IP的数据需要满足断电不丢失的要求,ROM IP数据的文件格式一般有三种文件格式:.mif、.hex、.coe,Xilinx与Intel Altera支持的ROM IP数据文件格式如下: Xilinx与Altera支持的ROM文件格式 Alterahex、mifAM(助记)Xilinxhex、coeXC(助记) .hex、.coe格式一般是用于Xilinx版本

Quartus报错资源不够用问题分析

Quartus报错资源不够用问题分析 本文为明德扬原创文章,转载请注明出处! 当quartus报错资源不够的时候,报错为:170048 Selected device has 56 RAM location(s) of type M9k. However,the current design needs more than 56 to successfully fit.(如下图所示)