本文主要是介绍基于FPGA的数字电子钟VHDL代码Quartus仿真,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

名称:基于FPGA的数字电子钟VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

数字电子钟

1)设计一个能显示秒、分、时的24小时数字钟

2)用数码管显示出时,分,秒,复位显示00:00:00

3)通过按键可对时,分,秒进行设置

1. 工程文件

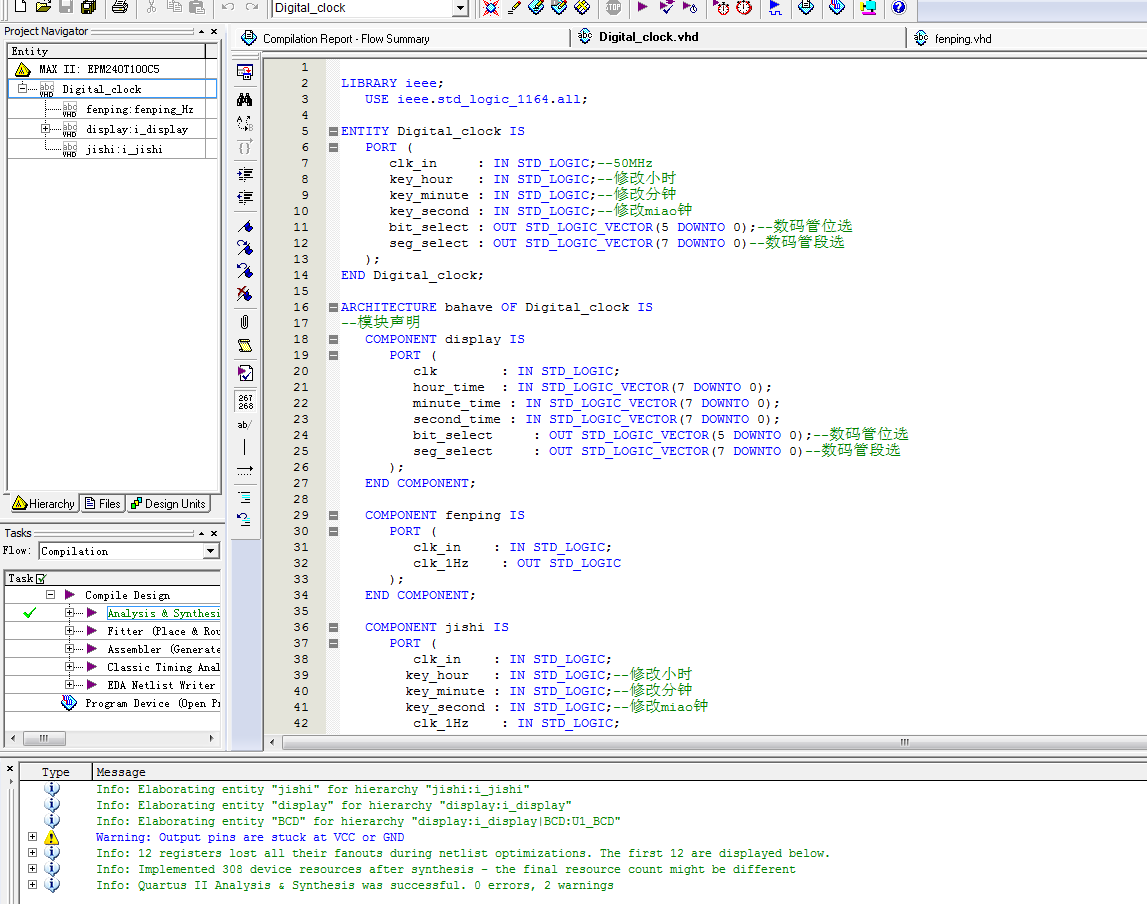

2. 程序文件

3. 程序编译

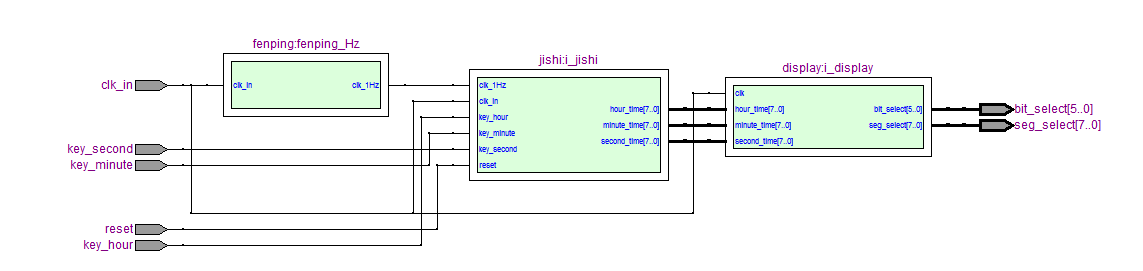

4. RTL图

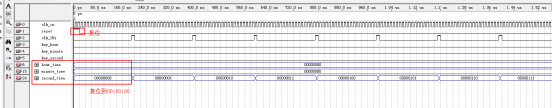

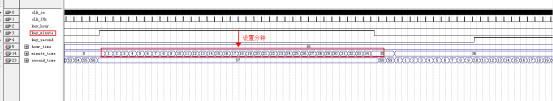

5. 仿真图

整体仿真图

分频模块仿真

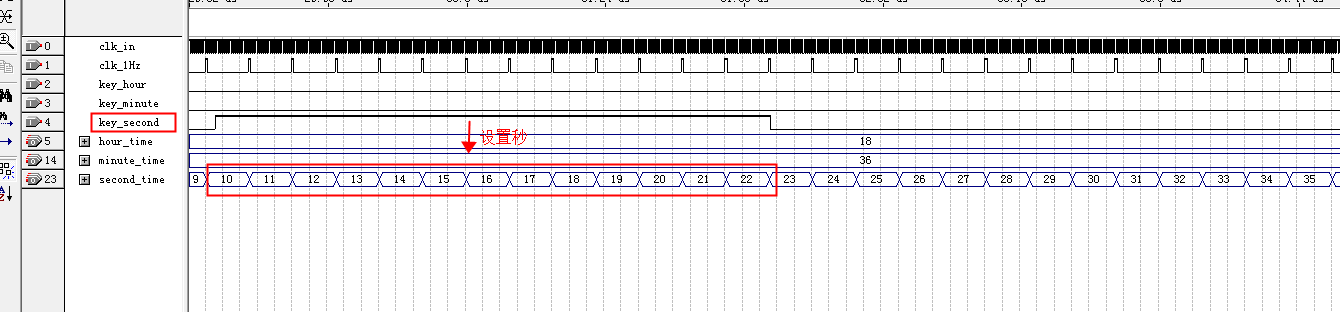

计时模块

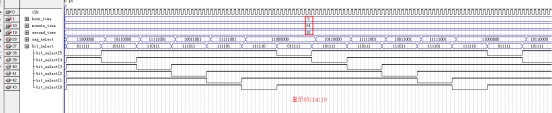

显示模块

部分代码展示:

LIBRARY ieee;USE ieee.std_logic_1164.all; ENTITY Digital_clock ISPORT (clk_in : IN STD_LOGIC;--50MHzreset : IN STD_LOGIC;--resetkey_hour : IN STD_LOGIC;--修改小时key_minute : IN STD_LOGIC;--修改分钟key_second : IN STD_LOGIC;--修改miao钟bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选); END Digital_clock; ARCHITECTURE bahave OF Digital_clock IS --模块声明COMPONENT display ISPORT (clk : IN STD_LOGIC;hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0);bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选);END COMPONENT;COMPONENT fenping ISPORT (clk_in : IN STD_LOGIC;clk_1Hz : OUT STD_LOGIC);END COMPONENT;COMPONENT jishi ISPORT (clk_in : IN STD_LOGIC;reset : IN STD_LOGIC;--reset key_hour : IN STD_LOGIC;--修改小时 key_minute : IN STD_LOGIC;--修改分钟 key_second : IN STD_LOGIC;--修改miao钟clk_1Hz : IN STD_LOGIC;hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT;SIGNAL hour_time : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL minute_time : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL second_time : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL clk_1Hz : STD_LOGIC; BEGIN--分频到1Hzfenping_Hz : fenpingPORT MAP (clk_in => clk_in,clk_1Hz => clk_1Hz);--计时模块i_jishi : jishiPORT MAP (clk_in => clk_in,reset =>reset,key_hour=> key_hour,key_minute=> key_minute,key_second => key_second,--修改miao钟clk_1Hz => clk_1Hz,hour_time => hour_time,--时minute_time => minute_time,--分second_time => second_time--秒);--显示模块i_display : displayPORT MAP (clk => clk_in,hour_time => hour_time,minute_time => minute_time,second_time => second_time,bit_select =>bit_select,--数码管位选seg_select =>seg_select--数码管段选);END bahave;

源代码

扫描文章末尾的公众号二维码

这篇关于基于FPGA的数字电子钟VHDL代码Quartus仿真的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!