vhdl专题

从VHDL代码到真实硬件:设计一个8位算术逻辑单元

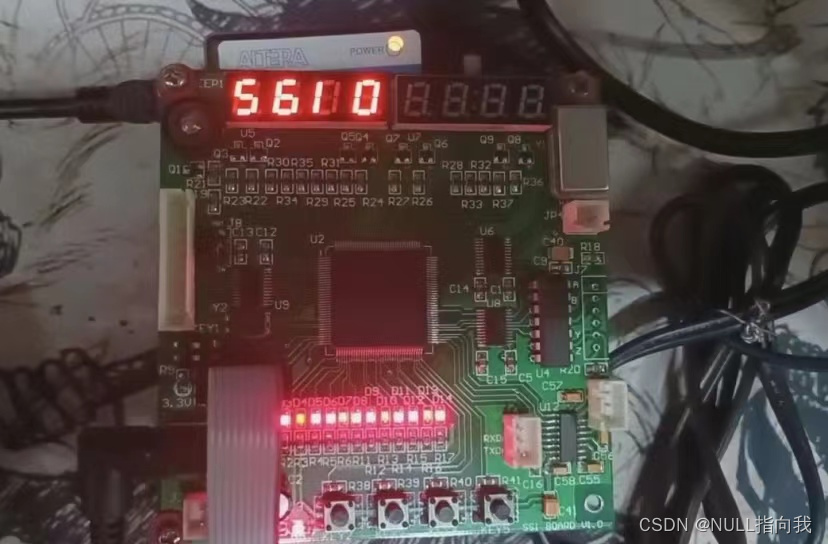

在这个项目中,我们使用VHDL语言创建了一个8位算术逻辑单元(ALU),并在连接到带有输入开关和LED显示器的自定义PCB的Altera CPLD开发板上运行它。 本文引用地址:https://www.eepw.com.cn/article/202409/462593.htm 使用基于硬件的方法开发电子系统并不总是需要将各种晶体管和逻辑门物理连接到面包板或PCB上。可以使用离散逻辑构建算术逻辑单

VHDL实现IEEE802.3中的CRC32算法

IEEE 802.3 标准中规定的 CRC32 算法是一种基于多项式除法的校验和计算方法。在以太网中,每个帧都包括一个CRC32校验字段,用于检测数据在传输过程中是否出现了错误。该算法使用的多项式为x32 + x26 + x23 + x22 + x16 + x12 + x11 + x10 + x8 + x7 + x5 + x4 + x2 + x + 1 多项式按正常写法是0x04C11DB7,计算

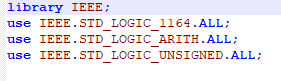

VHDL的数据类型(学习笔记2)

VHDL语言学习笔记(二):数据类型 VHDL语言是一种强数据类型语言,它对运算关系和赋值关系中各种操作数据类型有严格要求: VHDL要求设计实体中的每一个常量、信号、变量、函数以及设定的各种参量都必须具有确定的数据类型,只有相同数据类型的量才能相互传递和作用。 文章目录 VHDL语言学习笔记(二):数据类型1、标准的数据类型1.1,实数(REAL)1.2,整数(INTEGER)1.

VHDL语言入门整理

1.2选1多路选择器 Library ieee; Use ieee.std_logic_1164.all; Entity L1 is Port ( a,b,s:in std_logic; y:out std_logic ); End L1; Architecture one of L1 is Begin Process(a,b,s)begin If(s='0')then y<=a; Else

Verilog或VHDL中防止信号综合后被优化众多方法总结 ,亲测实用

Verilog 方法1. Synthesis_Options中的-keep hierarchy设置为YES或soft,zhe 在ISE中的综合(XST)选项上右键选择process properties,弹出的对话框里面Synthesis_Options中的-keep hierarchy是设置综合后层次结构的。设置为YES后,用CHIPSCOPE调试时看到的层次结构跟你的设计是一样的,找信号很

VHDL | 音乐盒设计(代码类)

博主github:https://github.com/MichaelBeechan 博主CSDN:https://blog.csdn.net/u011344545 ****************************Copyright (c)***************************-----------------------------File Info------

VHDL/CPLD硬件描述语言:2022年做的万年历实验

之前接触过一些硬件描述语言以及VHDL/CPLD的单片机的设计实验,那时是2022年了 这里补写一篇笔记,以记录一下那十多个小时 万年历实验 研究中的心得体会: 说明解释都是个人理解,与标准描述有较大出入...... 目录 输入输出器件的编写: 分频器点亮不同频率LED: 引用头文件: 实体(ENTITY)定义和架构(ARCHITECTURE)的开头部分: 主体:变量定义与时钟事件检查

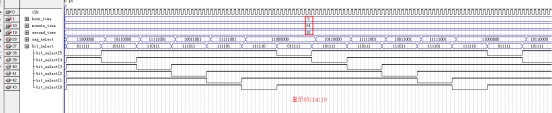

基于FPGA的数字电子钟VHDL代码Quartus仿真

名称:基于FPGA的数字电子钟VHDL代码Quartus仿真(文末获取) 软件:Quartus 语言:VHDL 代码功能: 数字电子钟 1)设计一个能显示秒、分、时的24小时数字钟 2)用数码管显示出时,分,秒,复位显示00:00:00 3)通过按键可对时,分,秒进行设置 1. 工程文件 2. 程序文件 3. 程序编译 4. RTL图

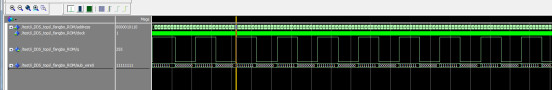

基于FPGA的DDS波形发生器VHDL代码Quartus仿真

名称:基于FPGA的DDS波形发生器VHDL代码Quartus仿真(文末获取) 软件:Quartus 语言:VHDL 代码功能: DDS波形发生器VHDL 1、可以输出正弦波、方波、三角波 2、可以控制输出波形的频率 DDS波形发生器原理 1. 工程文件 2. 程序文件 ROM IP核 3. 程序编译 4. RTL图

VHDL语言中的包集和原件

介绍 在学习这部分之前,我一直感觉VHDL语言特别没有层次,代码一坨一坨的,让人看着很不舒服。学习了包集和原件,感觉好太多了。 原件(component) 一个元件就是一段结构完整的代码(包括库声明,实体和结构体)组成。将这个完整的结构声明为元件,就可以供其他电路使用,这样代码看起来就有层次化了。 我举一个与门的例子: library ieee; us

VHDL中txt文件的读写

本文转载: https://blog.csdn.net/love_ljq/article/details/53637597 在对VHDL代码进行ModelSim仿真的时候,如果测试一个比较简单的功能,比如简单地测试一个IPCore,那么我们只需要 signalName <= x"01"; wait for cam_period*5; signalName <= x"10"; wait

verdi编译vhdl文件时,报出warning:*Warn* Unknown argument –vhdl08的解决 办法

原因分析: verdi -help打印出的帮助信息中可找到-vhdl08,但根据上下文可看到该选项是 nTrace工具的选项。所以命令如“verdi -vhdl08 -f include.f"会报出warning。解决办法: 使用verdi的vhdlcom工具来编译vhdl。例如: vhdlcom -vhdl08 top_design.vhd 然后再通过库调用的方式打

verdi加载vhdl和verilog混合RTL设计的方法

采用三步法完成混合语言RTL设计的加载。 step1. 用vhdlcom将所有的VHDL RTL代码编译成库 1.1 将所有的vhdl文件放到vhdl.f文件中,如: vhdl.f --------- my_design.vhd my_lib.vhd tb_my_design.vhd 1.2 编译成库

实战EDA电子设计自动化经典入门模型VHDL代码编写(含代码解释)下篇--D触发器 4选1多路开关

前言 上篇文章: 实战EDA电子设计自动化经典入门模型VHDL代码编写(含代码解释)上篇–状态机,逻辑设计:Y=AB+C 实战EDA电子设计自动化经典入门模型VHDL代码编写(含代码解释)中上篇–2-4译码器 信号十分频 电子设计自动化(EDA): 定义:EDA是用于设计和开发复杂的电子系统(如集成电路)和印刷电路板的软件工具集合。这些工具通常用于设计电路、进行仿真测试、分析电路行为以及协助制

北邮VHDL数电实验—电子沙漏

由于APEC假期推迟了一周,上周五我们才交实验报告,在这里我就不把自己的全部实验报告贴上来了。北邮或是其他学校的学生可以参考我的代码,并且欢迎提出交流 实验室里用的板子是EPM1270T144C5,内部时钟50MHz。我用的软件是Quartus9.0 实验基本要求: (1)采用 8*8 双色点阵显示电子沙漏的开机界面,如图2 所示。其中红色LED 代表沙漏的上半部分

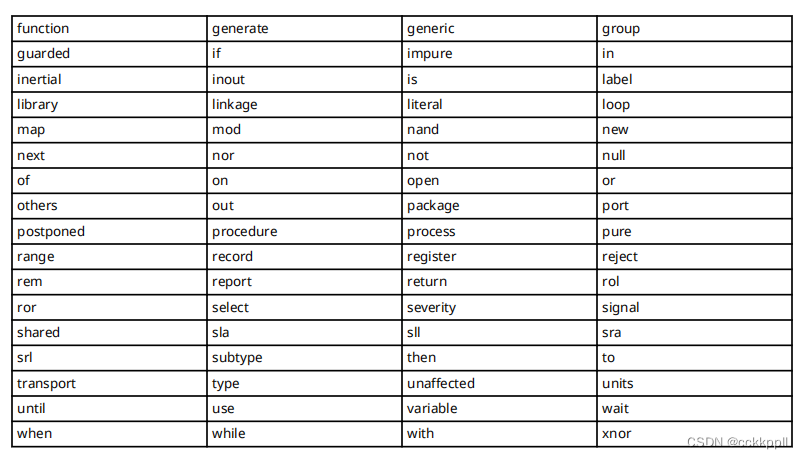

定义自己的VHDL包、VHDL构造支持状态、VHDL保留字

定义自己的VHDL包 您可以定义自己的VHDL包来指定: •类型和亚型 •常数 •功能和程序 •组件声明 定义VHDL包允许访问的其他部分的共享定义和模型您的项目,需要以下内容: •包声明:声明前面列出的每个元素。 •包主体:描述包声明中声明的函数和过程。 包声明语法 package mypackage is type mytype is record f

【FPGA】VHDL:八段码到8421BCD码转换电路

目录 EDA设计基础练习题 : 实验要求如下: 代码 八段码到8421BCD码转换电路 8421BCD码到八段码转换电路 八段码到8421BCD~运行结果展示 8421BCD转八段码~运行结果展示 特别注意 软件:Quartus II 13.0 (64-bit) 语言:VHDL EDA设计基础练习题 : 4、八段码到8421BCD码转换电路(以共阳极数码管为例)

单板计算机(SBC)-片上系统(SOC)嵌入式C++和FPGA(VHDL)

要点: 片上系统/单板计算机嵌入式C++及VHDL编程单板计算机(Raspberry Pi)C++实现MQTT监控房间门锁,灯光,并使用RESTful提示状态单板计算机(ESP8266)C++ 无线网络 MQTT土壤湿度监测仪,实现HTTP服务器,创建网页版监控界面,构建ESP8266监控固件,单板计算机集成到IP网络,添加二氧化碳检测传感器,使用GPIO和PWM控制继电器和直流压控风扇片上系统

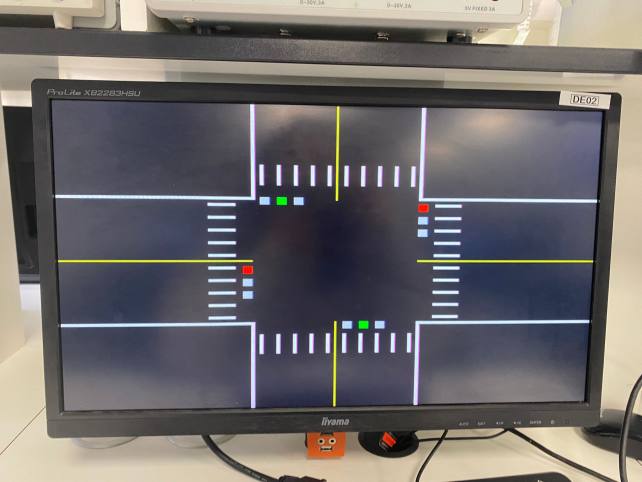

交通灯图像VGA显示DE1-SoC开发板红绿灯VHDL代码下载及设计报告

名称:交通灯图像VGA显示DE1-SoC开发板红绿灯数码管显示倒计时 软件:Quartus II 语言:VHDL 代码功能: 本设计使用VHDL语言设计VGA显示的交通灯,VGA显示屏上显示主干道和支干道,道路用白色线条描绘,每个道路中间用黄色线条隔开分为左右两个车道。每条主干道和支干道都对应有3个红绿灯,分别为红色、黄色、绿色。红黄绿三色交通灯指挥车辆的通行,红灯停,绿灯行,黄灯为绿灯到

VHDL有限状态机(单进程,双进程)交通灯示例

Finite State Machine有限状态机 它的逻辑流程图是: 注意!“当前状态”和“下一状态”的位置,我们将在下文的交通灯示例中理解。 设计要求: --我们要设计一个十字路口的交通灯,就两个按钮,东西方向一个(sensor2),南北方向一个(sensor)。流程就是,东西方向为红灯,南北在走人, --这时候东西方向的人想过马路,按下sensor2,然后红变绿,东西走,南北停。

第二章 VHDL语言元素

第二章 VHDL 语 言元 素 2.1 VHDL 语 言的客体 2.2 VHDL 语 言的数据 类 型 2.3 VHDL 数据 类 型 转换 2.4 VHDL 词 法 规则 与 标识 符 2.1 VHDL 语 言的客 体 VHDL 语 言中,可以 赋 予一个 质 的 对 象就称 为 客体 。客体主要包

第一章 VHDL基本结构

第一章 VHDL基本结构 1.1 实体 1.2 结构体 1.3 块、子程序和进程 1.4 库和程序包 1.5 配置 一个完整的VHDL程序,或者说设计实体,通常要求最低能为VHDL综合器所支持,并能作为一个独立的设计单元,即元件的形式而存在的VHDL程序。在VHDL程序中,通常包含实体(ENTITY)、结构体(ARC

4位行波加法器vhdl_推动未来雷达技术发展的4大关键技术

人类在掌握电磁波技术的50年以后,发展出了无线电雷达技术,它在第二次世界大战中崭露锋芒,发挥了巨大的作用。 近年来随着微波、计算机、半导体、大规模集成电路等各个领域科学进步,雷达技术在不断发展,其内涵和研究内容都在不断地拓展。雷达功能也由单一功能慢慢演变成多任务、多功能雷达系统。雷达使用的器件也由当初的晶体管发展成GaAs/ GaN/ SiGe的器件。 雷达技术及应用的最新发展趋势 当前面对

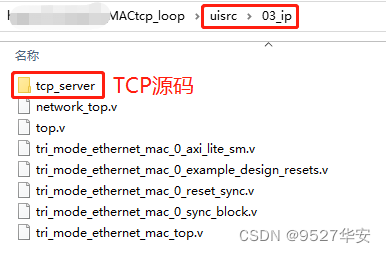

FPGA实现 TCP/IP 协议栈 客户端 纯VHDL代码编写 提供4套vivado工程源码和技术支持

目录 1、前言版本更新说明免责声明 2、相关方案推荐我这里已有的以太网方案1G 千兆网 TCP-->服务器 方案10G 万兆网 TCP-->服务器+客户端 方案常规性能支持多节点FPGA资源占用少数据吞吐率高低延时性能 4、TCP/IP 协议栈代码详解代码架构用户接口代码模块级细讲顶层模块PACKET_PARSING模块ARP模块IGMP_REPORT和IGMP_QUERY模块PING和WH

vhdl中mod与rem的区别

mod(取模)and rem(取余) VHDL has mod and rem. They return the same value if both arguments are positive.but, they produce different results for negative inputs:5 mod 3 = 2(-5) mod 3 = 15 mod (-3) = -1(-5)

VHDL数码管显示控制器设计

题目要求: 初始状态,开关 K1 为低电平,6 个数码管上依次显示 1-6。当 K1 变为高电平时,数据管显示内容依次循环左移,当 K1 变为低电平时,保持当前显示内容。 参考资料:使用VHDL实现动态扫描八位七段数码管 我参考了他的计时器部分 我的代码: library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.