本文主要是介绍定义自己的VHDL包、VHDL构造支持状态、VHDL保留字,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

定义自己的VHDL包

您可以定义自己的VHDL包来指定:

•类型和亚型

•常数

•功能和程序

•组件声明

定义VHDL包允许访问的其他部分的共享定义和模型您的项目,需要以下内容:

•包声明:声明前面列出的每个元素。

•包主体:描述包声明中声明的函数和过程。

包声明语法

访问VHDL包

要访问VHDL包,请执行以下操作:

1.使用库子句来包括编译包的库。例如

库library_name;

2.用use子句指定包或包中包含的特定定义。

例如:使用library_name.package_name.all。

3.将这些行直接插入使用包的实体或体系结构之前定义。因为工作库是默认库,所以如果指定包已编译到此库中。

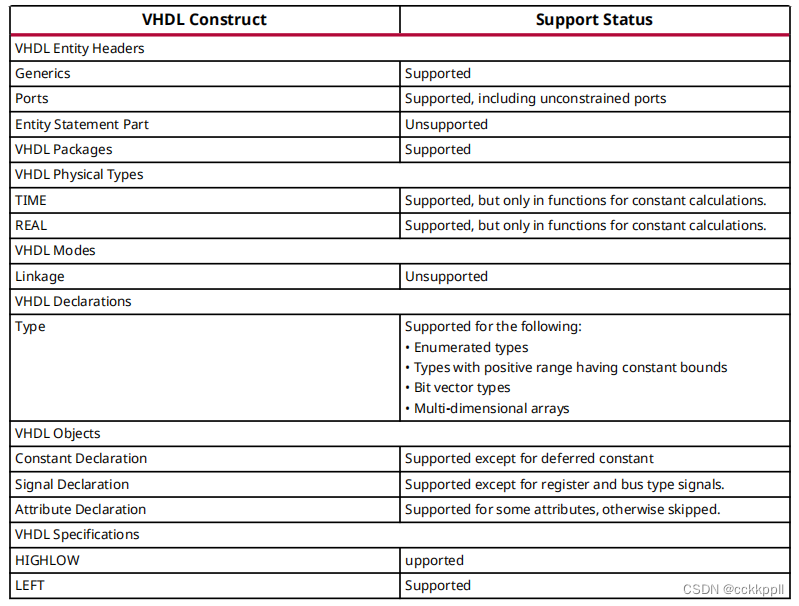

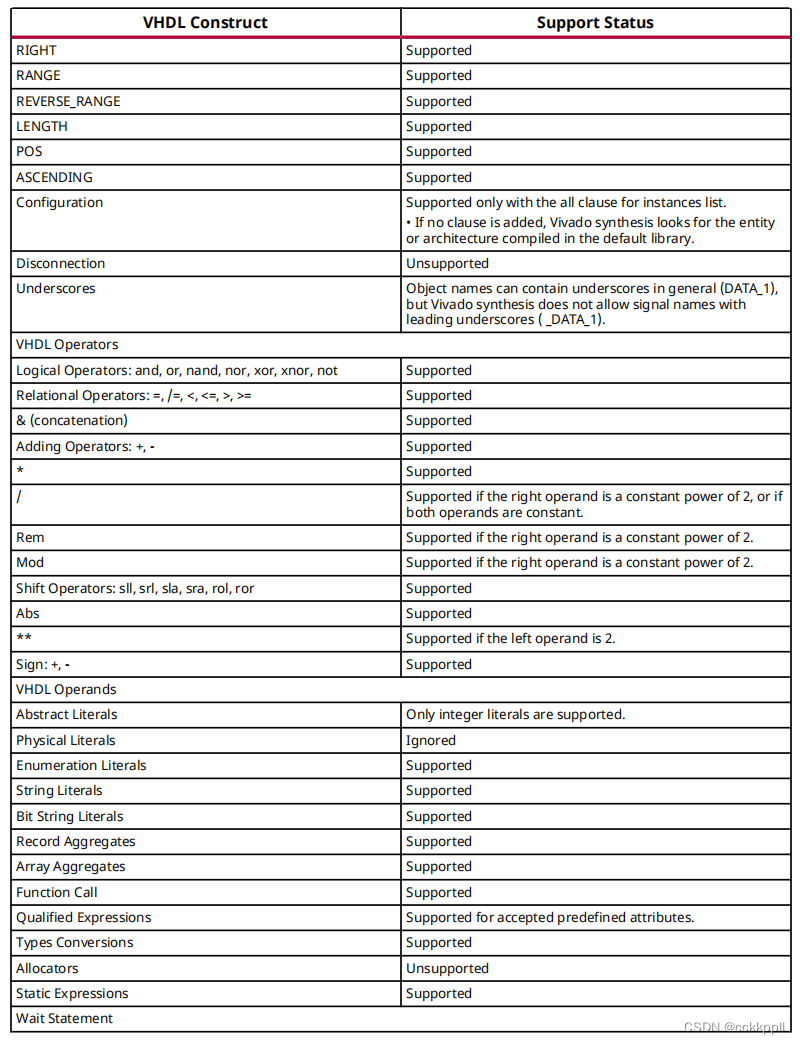

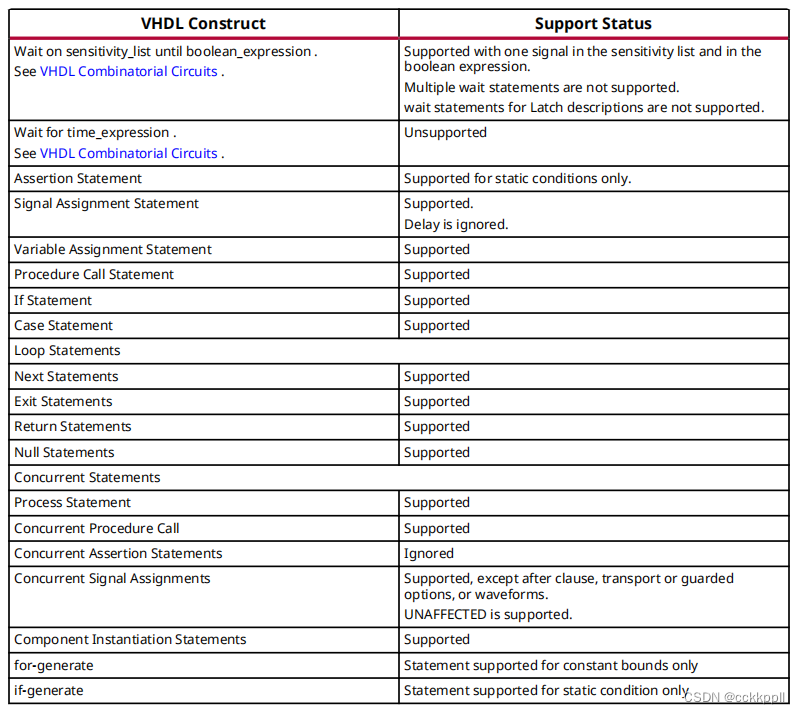

VHDL构造支持状态

Vivado synthesis支持VHDL设计实体和配置,除非中另有说明下表。

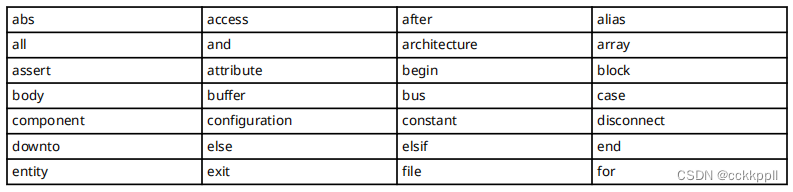

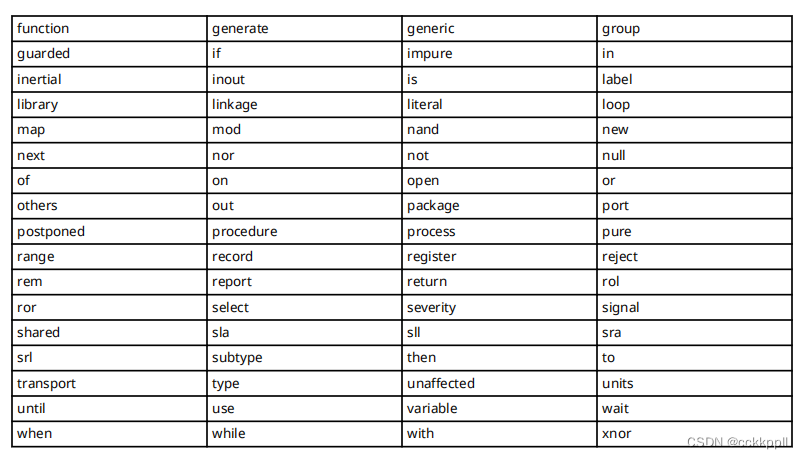

VHDL保留字

这篇关于定义自己的VHDL包、VHDL构造支持状态、VHDL保留字的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!