本文主要是介绍PLL深度解析第一篇——PLL的知识图谱,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在硬件电路中,时钟就像心脏一样,在时钟的节拍下,不同的芯片、不同的电路、不同的接口都可以有序的进行工作或者通信(类似流水线一样,必须有节奏的运行)。

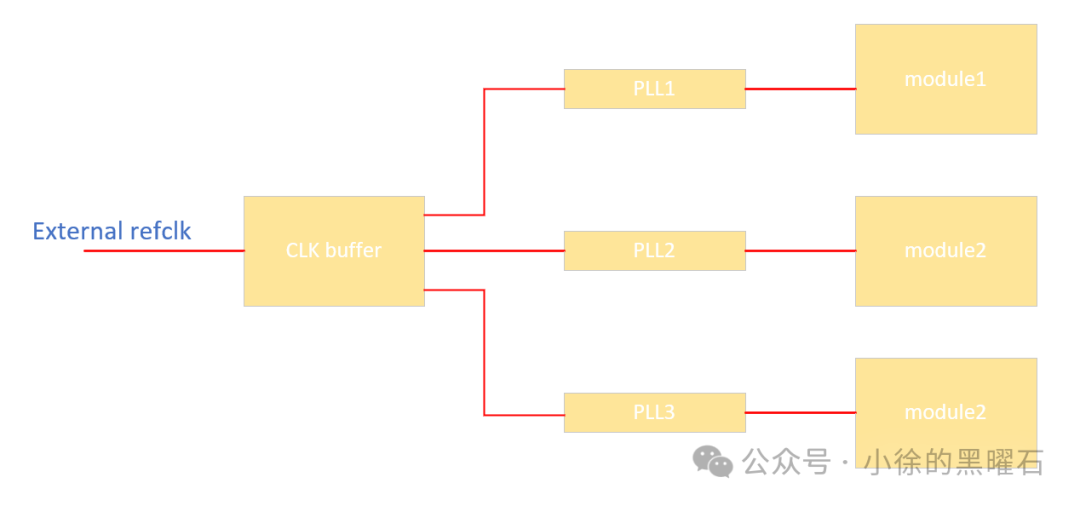

但是在芯片中,不同的模块和接口工作的频率并不一样,我们需要把提供的参考时钟转换到不同的模块和接口需要的频率上去,一般起到该功能的有分频器、PLL锁相环、CLK buffer等,一起组成了芯片复杂的CLK tree来对时钟频率进行转换和分配。

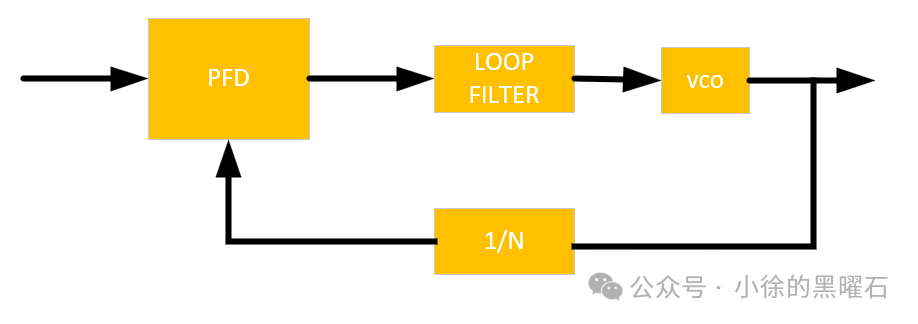

而其中最复杂以及起到最主要作用的就是PLL:

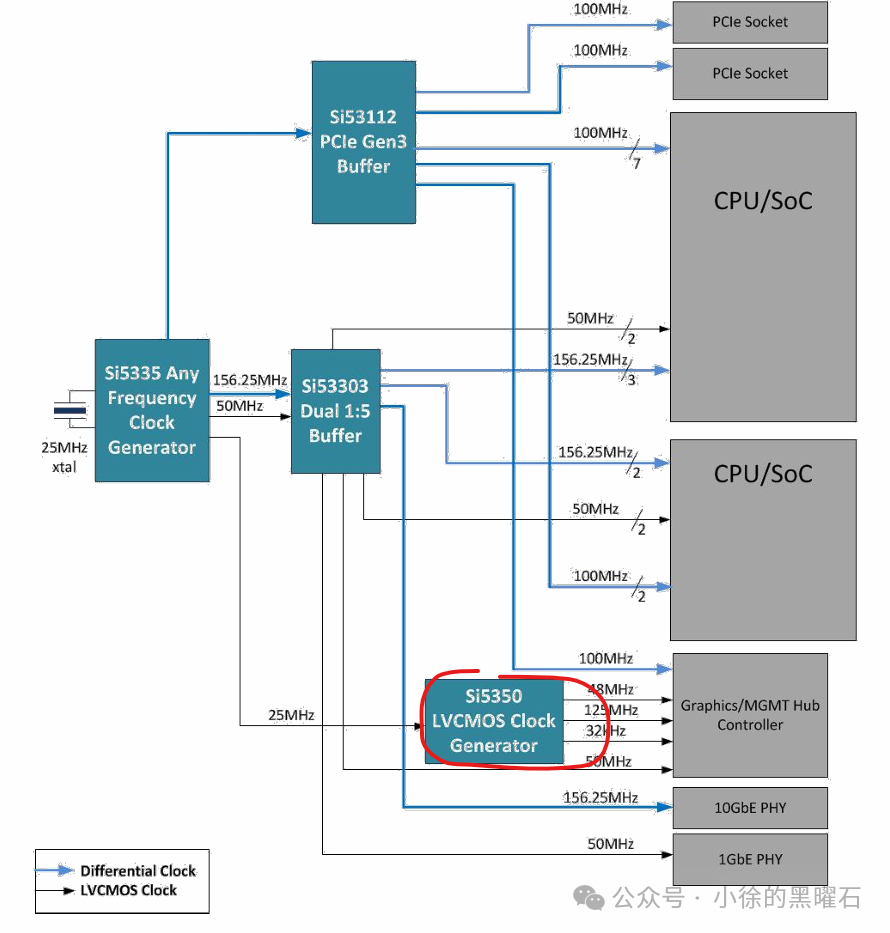

下图的architecture是PLL在时钟分配中的典型应用,外部给到系统的参考时钟是25MHZ,但是不同模块需要的时钟频率各有不同,需要提供100MHZ、50MHZ、48MHZ、165.25MHZ等各种频率甚至不同性能要求的时钟,分析下面的架构可以发现,部分CLK可以通过分频器产生就可以了,而部分则只能通过PLL产生并对时钟进行分配,比如将25MHZ时钟倍频到48MHZ。

当然PLL的作用不局限于此,在高速接口、射频电路等也有非常广泛的应用场景,比如Serdes中的CDR(即时钟数据恢复)中也常常使用PLL来调节恢复时钟的频率并补偿由于工艺或者温度变化而导致的频率变化。

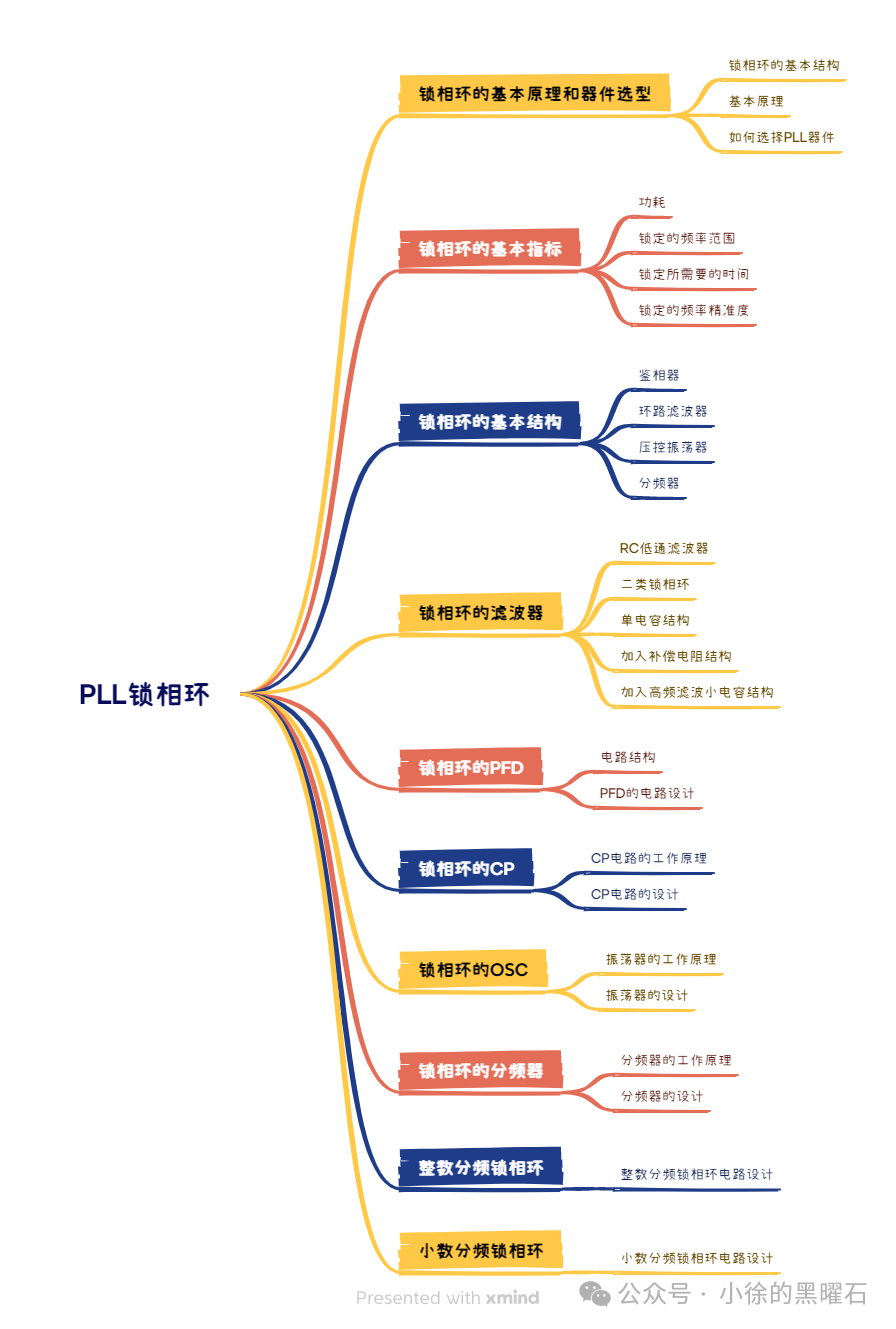

PLL非常复杂,也是一门在持续发展的技术方向,因此我们尝试在应用的角度对PLL的知识进行讲解,整体上将会参考下面的PLL锁相环知识图谱进行分析

这篇关于PLL深度解析第一篇——PLL的知识图谱的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!