本文主要是介绍IP核--PLL、ROM、RAM,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

IP核

- 理论知识

IP(Intellectual Property)即知识产权,用于 ASIC 或 FPGA 中的预先设计好的电路功能模块。

优点:提高开发效率,减少设计和调试时间,加速开发进程,降低开发成本。

缺点:

-

- 跨平台时IP核往往不通用。

-

- IP核是黑匣子,不透明,看不到核心代码。

-

- 有些定制的 IP 核由于是不通用的,往往会有较高的收费,这也是一笔巨大的开销。

IP 核有三种不同的存在形式:HDL 语言形式,网表形式、版图形式。分别对应我们常说的三类 IP 内核:软核、固核和硬核。

1.1 软核,用硬件描述语言的形式功能块的行为,并不涉及用什么电路和电路元件实现这些行为。大多数应用于 FPGA 的 IP 内核均为软核,软核有助于用户调节参数并增强可复用性。由于不涉及物理实现,为后续设计留有很大的发挥空间,增大了 IP 的灵活性和适应性。其主要缺点是在一定程度上使后续工序无法适应整体设计,从而需要一定程度的软 IP 修正,在性能上也不可能获得全面的优化。

1.2 固核,是软核和硬核的折衷。固核是完成了综合的功能块,有较大的设计深度,以网表的形式交给客户使用。

对时序要求严格的内核(如 PCIE 接口内核),可预布线特定信号或分配特定的布线资源,以满足时序要求。

1.3 硬核,是完成提供设计的最终阶段产品——掩膜(Mask),以经过完全的布局布线的网表形式提供,这种硬核既具有可预见性,同时还可以针对特定工艺或购买商进行功耗和尺寸上的优化。缺点是缺乏灵活性、可移植性差。另外,由于无须提供寄存器转移级(RTL)文件,因而更易于实现 IP 保护。

PLL IP 核

PLL(Phase Locked Loop,即锁相环),可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟。

工作原理:

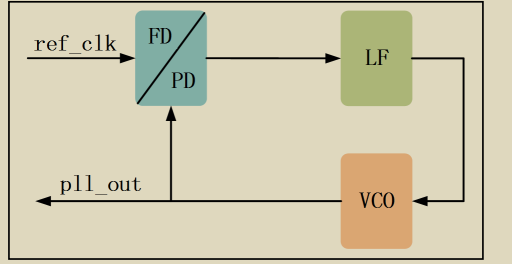

ref_clk参考时钟通过鉴频(FD)或鉴相(PD)器和需要比较的时钟频率或相位进行比较,然后输出进入环路滤波器(LF)控制噪声的带宽,滤掉高频噪声,使之稳定在一个值,起到将带有噪声的波形变平滑的作用。经过环路滤波器的输出连接到压控振荡器(VCO)上,环路滤波器输出的电压可以控制 VCO 输出频率的大小,环路滤波器输出的电压越大 VCO 输出的频率越高。

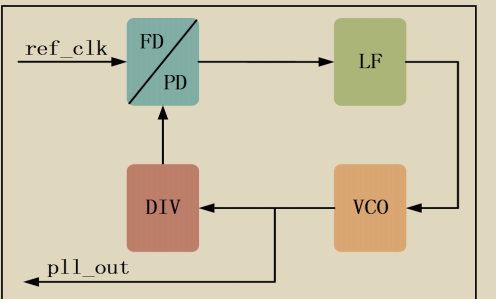

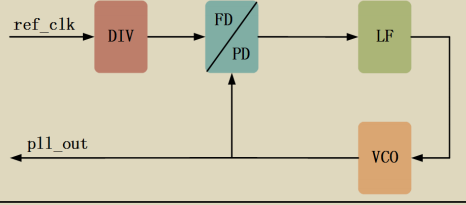

对于倍频和分频,是通过增加一个分频器实现。

比如倍频:

分频:

仿着实现

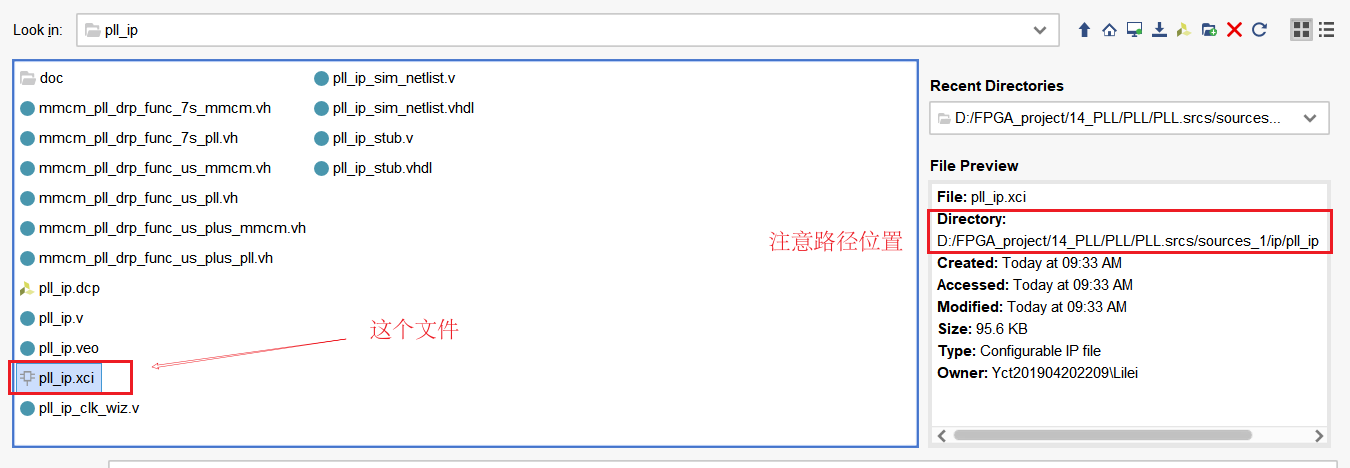

在实现时先创建IP核工程,然后进行设计。之后要利用该IP核时新建工程后再把IP核添加进去,然后注意变量名,要更改后和工程一样。

添加IP核到新工程里的文件是

代码和仿真:

module pll

(input wire sys_clk,input wire clk_mul2,input wire clk_div2,input wire clk_phase90,input wire clk_ducle20,output wire locked

);pll_ip pll_ip_inst

(.clk_in1 (sys_clk),.clk_out1 (clk_mul2),.clk_out2 (clk_div2),.clk_out3 (clk_phase90),.clk_out4 (clk_ducle20),.locked (locked)

);endmodule

`timescale 1ns/1nsmodule tb_pll();reg sys_clk;

wire clk_mul2;

wire clk_div2;

wire clk_phase90;

wire clk_ducle20;wire locked;initial sys_clk = 1'b1;always #10 sys_clk = ~sys_clk;pll pll_inst

(

. sys_clk (sys_clk),

. clk_mul2 (clk_mul2),

. clk_div2 (clk_div2),

. clk_phase90 (clk_phase90),

. clk_ducle20 (clk_ducle20),

.locked (locked));endmodule

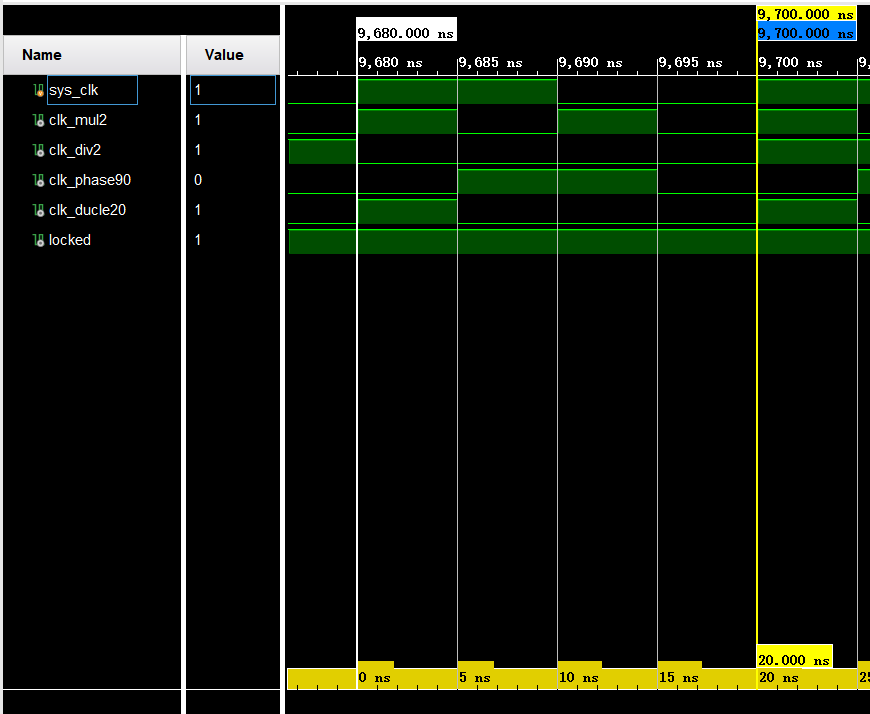

仿真的结果如下:

ROM IP核

-

ROM基础知识

ROM 是只读存储器(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦储存资料就无法再将之改变或删除,且资料不会因为电源关闭而消失。

在 FPGA 中通过 IP 核生成的 ROM 或 RAM调用的都是 FPGA 内部的 RAM 资源,掉电内容都会丢失。**用 IP 核生成的 ROM 模块只是提前添加了数据文件(.coe 格式),在 FPGA 运行时通过数据文件给 ROM 模块初始化,**才使得 ROM 模块像个“真正”的掉电非易失存储器。

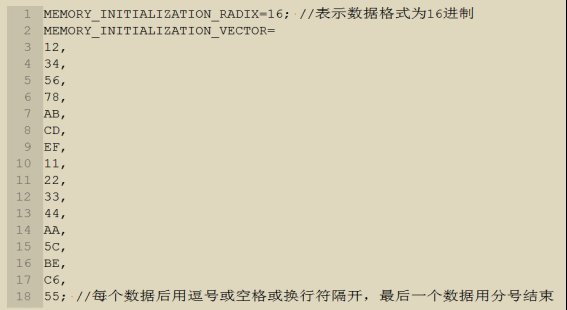

对于ROM初始化文件,.coe格式,里面规定了数据格式和初始化数据。

比如:

-

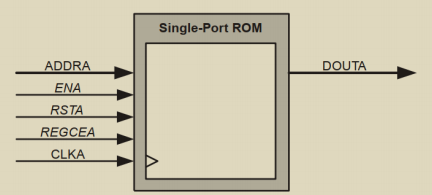

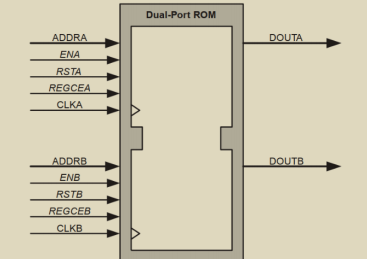

Xilinx推出两种ROM IP核,单端口 ROM(Single-Port Rom)和双端口ROM(Dual-Port ROM)。对于单端口 ROM 提供一个读地址端口和一个读数据端口,只能进行读操作;双端口 ROM 与单端口 ROM 类似,区别是其提供两个读地址端口和两个读数据端口,基本上可以看做两个单口 RAM 拼接而成。

RAM IP核

- RAM基础知识

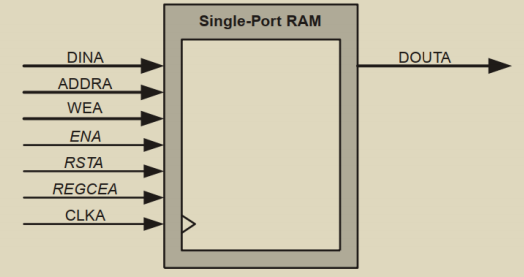

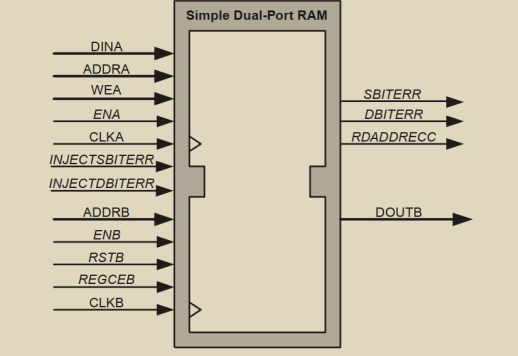

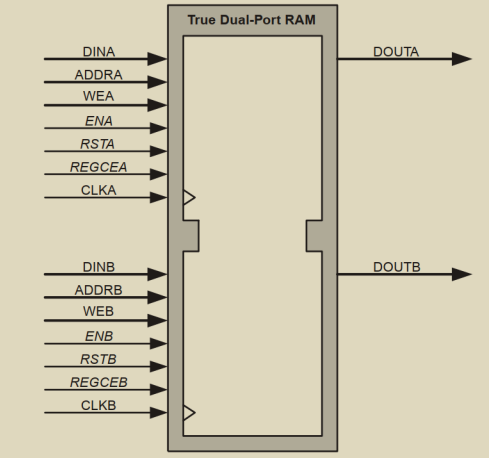

RAM 是**随机存取存储器(Random Access Memory)**的简称,是一个易失性存储器。RAM 工作时可以随时从任何一个指定的地址写入或读出数据,同时我们还能修改其存储的数据,即写入新的数据。 - Xilinx 推出的 RAM IP 核分为两种类型:单端口 RAM 和双端口 RAM,双端口RAM又分为简单和真正双端口RAM。这三种可以类比单工、半双工、双工通信方式。

单端口,读写操作共用一组地址线,读写操作不能同时进行。

简单双端口,写端口只能写不能读,而读端口只能读不能写。

真正双端口,有两个地址端口用于读写操作(两个读/写端口),即两个端口都可以进行读写。

FIFO IP 核

- 理论知识

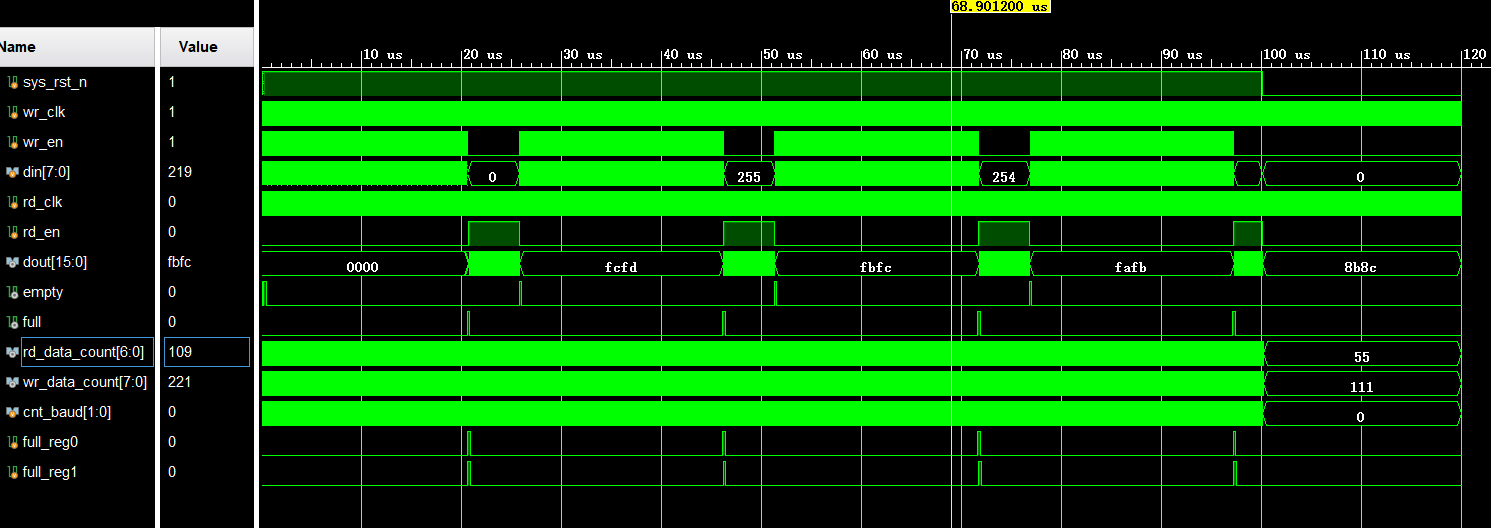

FIFO(First In First Out,即先入先出),是一种数据缓冲器,用来实现数据先入先出的读写方式,FIFO存储器没有地址线。

FIFO 根据读写时钟是否相同,分为 SCFIFO(同步 FIFO)和 DCFIFO(异步 FIFO),SCFIFO 的读写为同一时钟,应用在同步时钟系统中;DCFIFO 的读写时钟不同,应用在异步时钟系统中。 - 以异步FIFO为例

首先按照资料创建DCFIFP核,然后新建工程并添加IP核,之后和普通工程一样。

源代码

module dcfifo

(output wire [15:0] dout,output wire empty,output wire full,output wire [6:0] rd_data_count,output wire [7:0] wr_data_count,input wire rd_clk,input wire wr_clk,input wire [7:0] din,input wire rd_en,input wire wr_en);dcfifo_256x8 dcfifo_256x8_inst

(.din (din),.dout (dout),.empty (empty),.full (full),.rd_clk (rd_clk),.rd_data_count (rd_data_count),.rd_en (rd_en),.wr_clk (wr_clk),.wr_data_count (wr_data_count),.wr_en (wr_en)

);

endmodule

仿真代码

`timescale 1ns/1nsmodule tb_dcfifo();wire [15:0] dout;

wire empty;

wire full;

wire [6:0] rd_data_count;

wire [7:0] wr_data_count;reg rd_clk;

reg wr_clk;

reg [7:0] din;

reg rd_en;

reg wr_en;

reg sys_rst_n;

reg [1:0] cnt_baud;

reg full_reg0;

reg full_reg1;initialbeginwr_clk = 1'b1;rd_clk = 1'b1;sys_rst_n <= 1'b0;#100sys_rst_n <= 1'b1;#100000sys_rst_n <= 1'b0;endalways #10 wr_clk = ~wr_clk;

always #20 rd_clk = ~rd_clk;//cnt_baud:计数从 0 到 3 的计数器,用于产生输入数据间的间隔

always@(posedge wr_clk or negedge sys_rst_n)if (sys_rst_n == 1'b0)cnt_baud <= 2'b0;else if (cnt_baud == 2'd3)cnt_baud <= 2'b0;elsecnt_baud <= cnt_baud + 1'b1;//wr_en,s输入数据有效标志信号,FIFO写请求信号

always@(posedge wr_clk or negedge sys_rst_n)if (sys_rst_n == 1'b0)wr_en <= 1'b0;else if (cnt_baud == 2'd3 && rd_en == 1'b0)wr_en <= 1'b1;elsewr_en <= 1'b0;//din,输入数据信号

always@(posedge wr_clk or negedge sys_rst_n)if (sys_rst_n == 1'b0)din <= 8'b0;else if (din == 8'd255 && wr_en == 1'b1)din <= 8'b0;else if (wr_en == 1'b1)din <= din + 1;//将同步于 rd_clk 时钟的写满标志信号 full 在 rd_clk 时钟下打两拍,与前面的计数周期对齐always@(posedge rd_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0) beginfull_reg0 <= 1'b0;full_reg1 <= 1'b0;endelsebeginfull_reg0 <= full;full_reg1 <= full_reg0;end//rd_en:FIFO 读请求信号同步于 rd_clk

always@(posedge rd_clk or negedge sys_rst_n)if (sys_rst_n == 1'b0)rd_en <= 1'b0;else if (full_reg1 == 1'b1)rd_en <= 1'b1;else if (empty == 1'b1)rd_en <= 1'b0;dcfifo dcfifo_inst

(.din (din),.dout (dout),.empty (empty),.full (full),.rd_clk (rd_clk),.rd_data_count (rd_data_count),.rd_en (rd_en),.wr_clk (wr_clk),.wr_data_count (wr_data_count),.wr_en (wr_en)

);endmodule

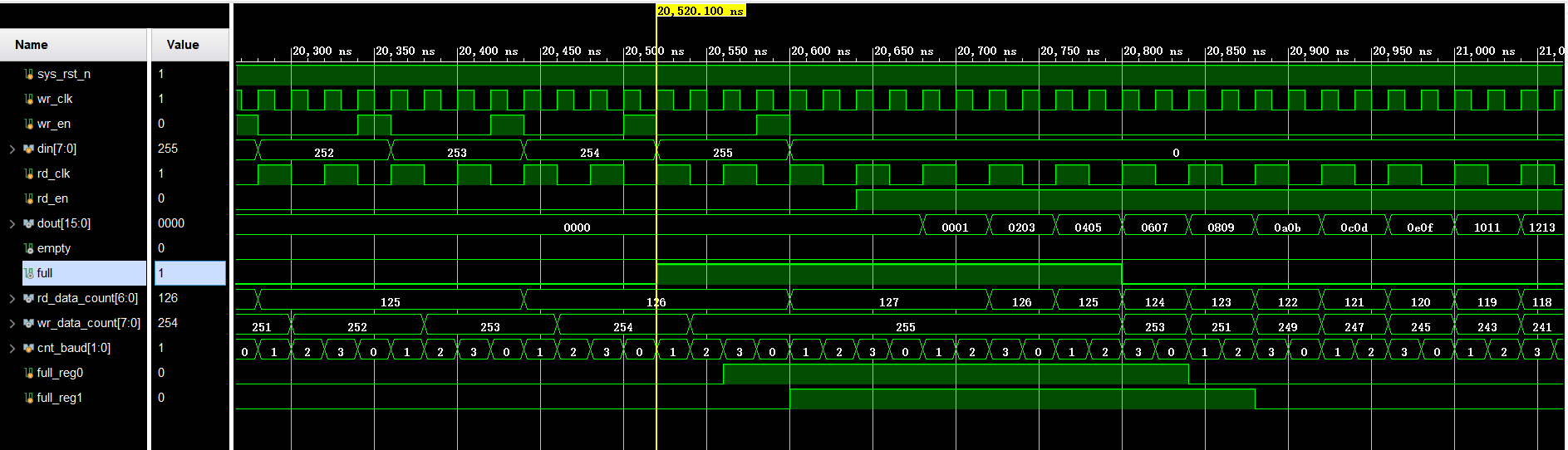

满FIFO

注意读出的时候,由于输出是16bit,所以输出的高八位和低八位是顺序的。

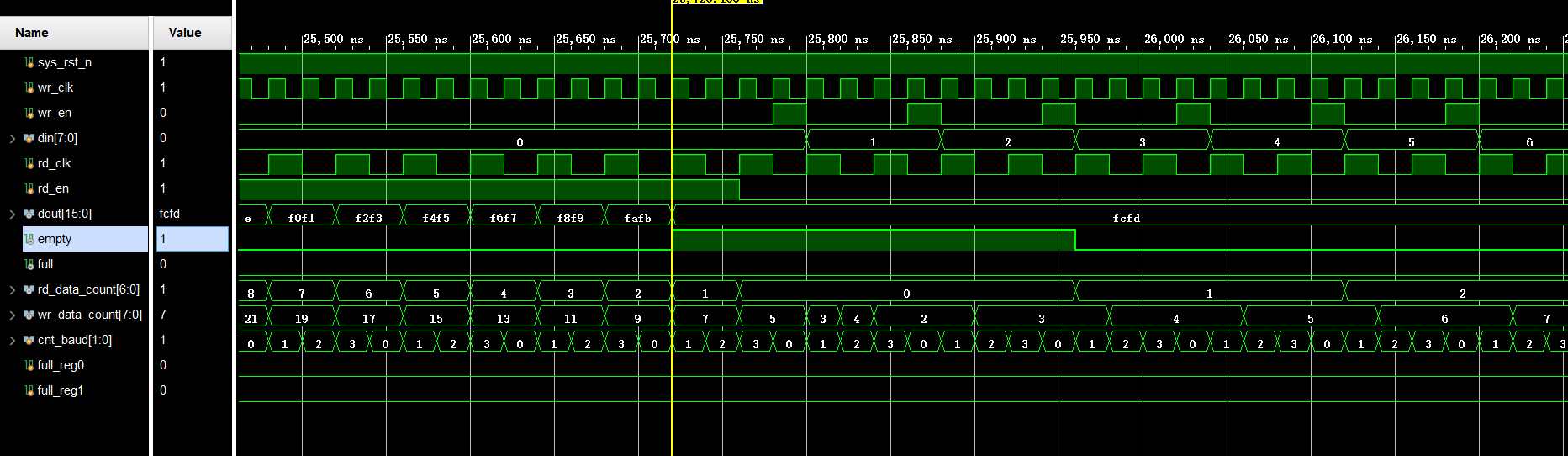

空FIFO

这篇关于IP核--PLL、ROM、RAM的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!