本文主要是介绍Quartus PLL分频,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

在Quartus中实现PLL分频,输入FPGA引脚上的25MHz的时钟,配置PLL使其输出四路分别为12.5Mhz,25Mhz,50Mhz和100MHz的时钟信号。

选择菜单Tools–>Mega Wizard Plug-In Manager选项

点击next

点击i/o中的ALT[LL,右上角的器件选择根据自己选择,保存路径建议先在整个工程文件夹中建立ip_core—>pll文件夹,这里路劲直接手写输入。点击next。

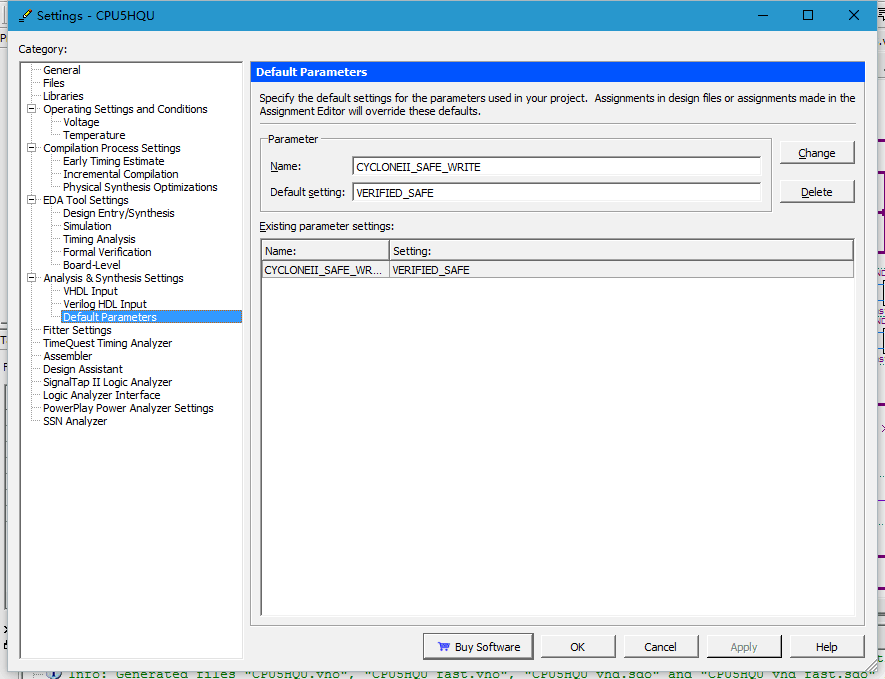

根据器件的速度等级选择8,输入到该PLL的时钟频率选择25MHz。

在Input/Lock 页面进行设置,点击next。

然后在Output Clocks页面对clk c0 ,clk c1,clk c2,clk c3,分别进行频率设置

配置完成后,进行Summary页面设置,勾选*_inst.v文件,点击finish即可。可以在pll文件夹中打开pll_controller_inst.v文件,这是PLL IP核例化的模板.

这篇关于Quartus PLL分频的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!