分频专题

时钟分频的几个细节理解

时钟分频原理简单。但需要注意几个细节。 计数器分频,是基于源时钟div2/4/8/16/32/64。如果基于分频器串联,那么需要定义很多分频时钟,提升sdc时钟定义的复杂性。计数器分频,要注意所有div2/4/8/16/32/64,需要保证同相位。这样才能方便sdc,正确定义分频时钟和源时钟的相位关系。遇到一些设计,采用门控EN,实现时钟分频。 这是FPGA设计经验,“在FPGA的设计中,分频时

STM32 定时器最佳分频

简而言之,您想满足以下方程式: 预分频器 * 溢出值 = 周期(以周期数表示)= 每秒时钟周期数 / 频率 Prescaler * Overflow = Period-in-Cycles = Clock-cycles-per-Second / Frequency 计算 PWM 的预分频器和 溢出值 的一个好方法是选择最小可能的预分频器,然后将溢出值调整到所需的总频率。这样可以使溢出值尽可能大

关于展频和小数分频的理论原理和实践

如果一个以为周期的函数在 上满足狄利克雷条件,即: 1.除去有限个第一类间断点外,处处连续 2.分段单调,单调区间的个数有限 则的fourier级数表示为: 在 上处处收敛,且在的连续点处收敛于, 其中, 对上式两边求积分: 所以: 对于 所以: 所以: 综上: 在电子通信领域,常常利用欧拉公式: 所以

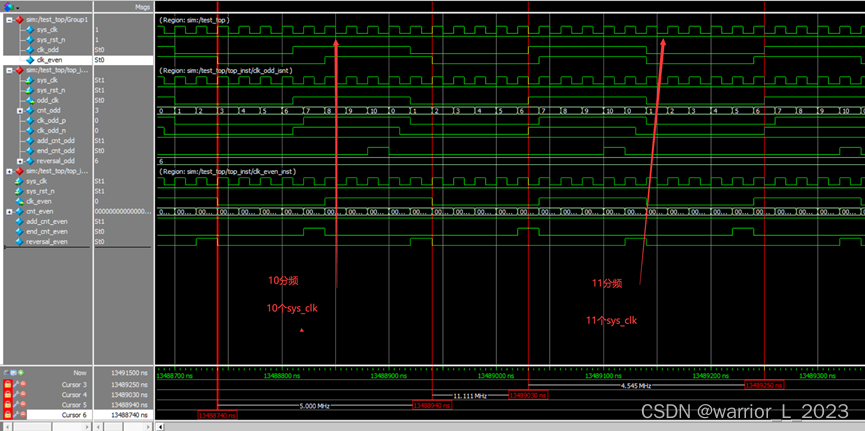

【牛客】VL76 任意奇数倍时钟分频

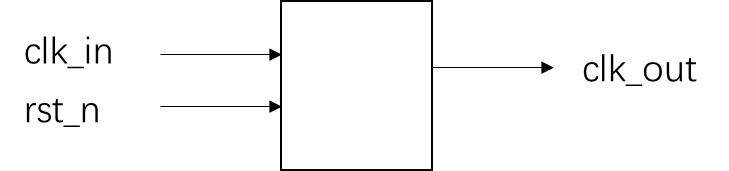

描述 编写一个模块,对输入的时钟信号clk_in,实现任意奇数分频,要求分频之后的时钟信号占空比为50%。模块应包含一个参数,用于指定分频的倍数。 模块的接口信号图如下: 要求:使用Verilog HDL语言实现,并编写testbench验证模块的功能。 输入描述: clk_in:输入时钟信号 rst_n:复位信号,低电平有效 输出描述: clk_out:分频之后的时钟信

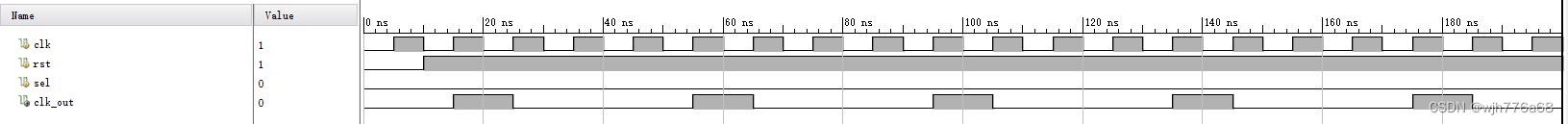

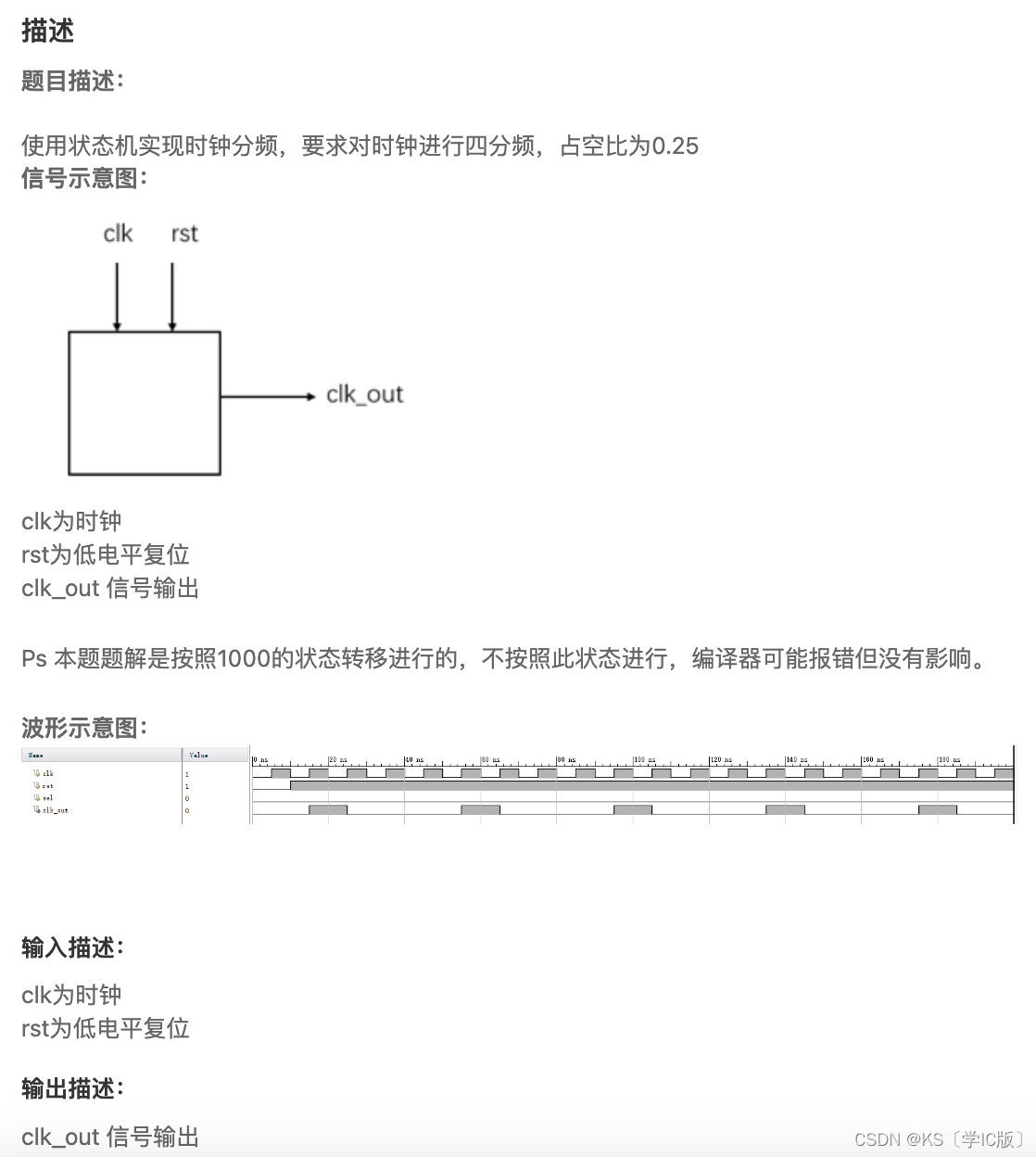

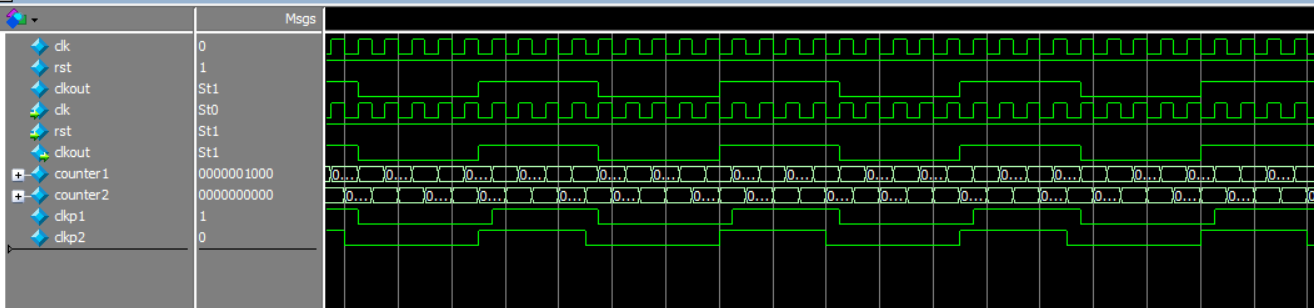

【牛客】VL65 状态机与时钟分频

描述 题目描述: 使用状态机实现时钟分频,要求对时钟进行四分频,占空比为0.25 信号示意图: clk为时钟 rst为低电平复位 clk_out 信号输出 Ps 本题题解是按照1000的状态转移进行的,不按照此状态进行,编译器可能报错但没有影响。 波形示意图: 输入描述: clk为时钟 rst为低电平复位 输出描述: clk_out 信号输出 `timescale 1n

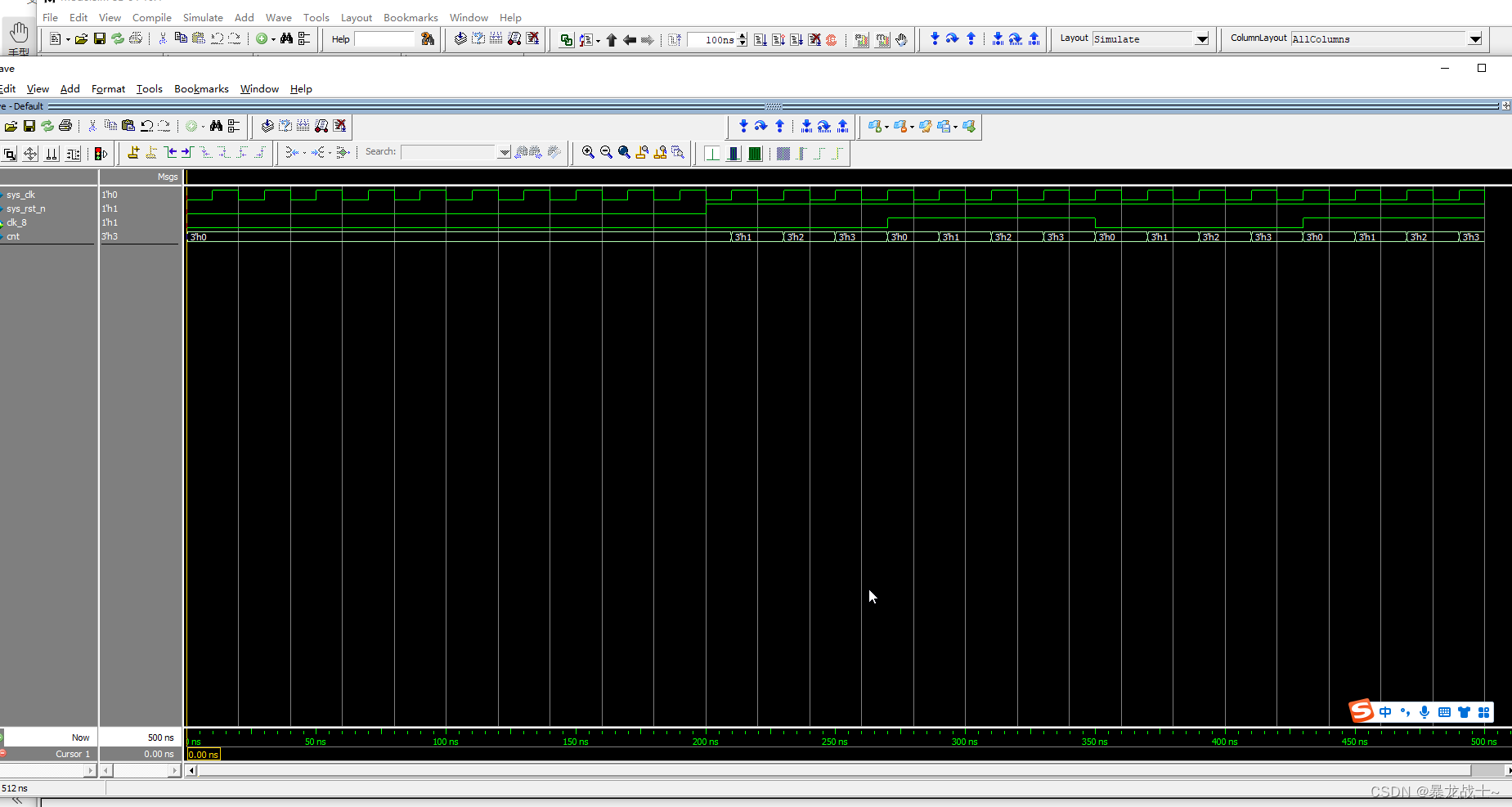

Verilog经典题(三)——偶分频、奇分频

文章目录 偶分频思路(看着就知道咋写的快速回顾)代码波形 奇分频思路代码波形 偶分频 占空比50%的偶分频 思路(看着就知道咋写的快速回顾) 参数DivNum定义几分频输入clk,rst 输出oclk,中间计数器count,tmp0 1 2 3 置高,4 5 6 7 置低 if(count == ((DivNum>>1) - 1)) begincount <= count

veri-log 语言之实现任意分频

veri-log 语言之实现任意分频 分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器。

lv14 内核内存管理、动态分频及IO访问 12

一、内核内存管理框架 内核将物理内存等分成N块4KB,称之为一页,每页都用一个struct page来表示,采用伙伴关系算法维护 补充: Linux内存管理采用了虚拟内存机制,这个机制可以在内存有限的情况下提供更多可用的内存空间。每个进程都有自己独立的虚拟地址空间,应用程序只能访问自己的地址空间,而不能直接访问其他进程的地址空间或内核空间。 当应用程序需要访问某些数据时,它会使用虚拟地址来

Quartus PLL分频

在Quartus中实现PLL分频,输入FPGA引脚上的25MHz的时钟,配置PLL使其输出四路分别为12.5Mhz,25Mhz,50Mhz和100MHz的时钟信号。 选择菜单Tools–>Mega Wizard Plug-In Manager选项 点击next 点击i/o中的ALT[LL,右上角的器件选择根据自己选择,保存路径建议先在整个工程文件夹中建立ip_core—>pll文件夹,这里

【Verilog】期末复习——设计一个带异步复位端且高电平有效的32分频电路

系列文章 数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter) 运算符 数据流建模 行为级建模 结构化建模 组合电路的设计和时序电路的设计 有限状态机的定义和分类 期末复习——数字逻辑电路分为哪两类?它们各自的特点是什么? 期末复习——VerilogHDL描述数字逻辑电路的建模方式有哪三种?它们的特点是? 期末复习——解释下列名词(FPGA、ASIC、IP、RTL

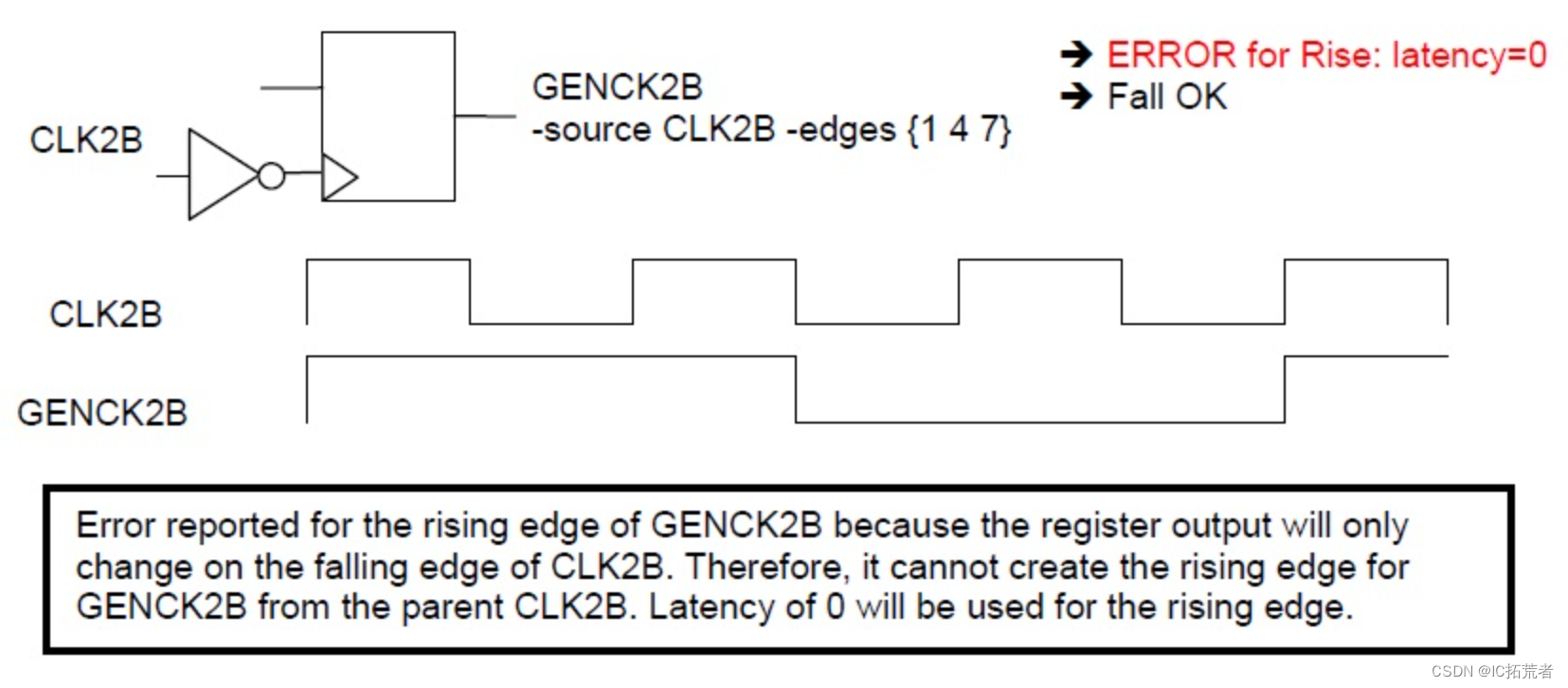

数字IC后端实现之Innovus TA-152错误解析(分频generated clock定义错误)

**ERROR: (TA-152): A latency path from the ‘Fall’ edge of the master clock at source pin… Error Code TA-152 在数字IC后端实现innovus中我们经常会看到这类Error,具体信息如下所示。 Error Message **ERROR: (TA-152): A latency pa

12.31信号位宽转换(整数,非整数),时钟分频(奇数,偶数,任意小数,占空比),自动售货机(1,2),游戏机

非整数倍数据位宽转换8to12 所谓非整数倍,就是利用一个cnt去周期性决定寄存器里怎么输出,这个cnt的值,是最小公倍数 寄存器就正常的寄存,怎么输入怎么寄存 `timescale 1ns/1nsmodule width_8to12(input clk , input rst_n ,input valid_in ,input [

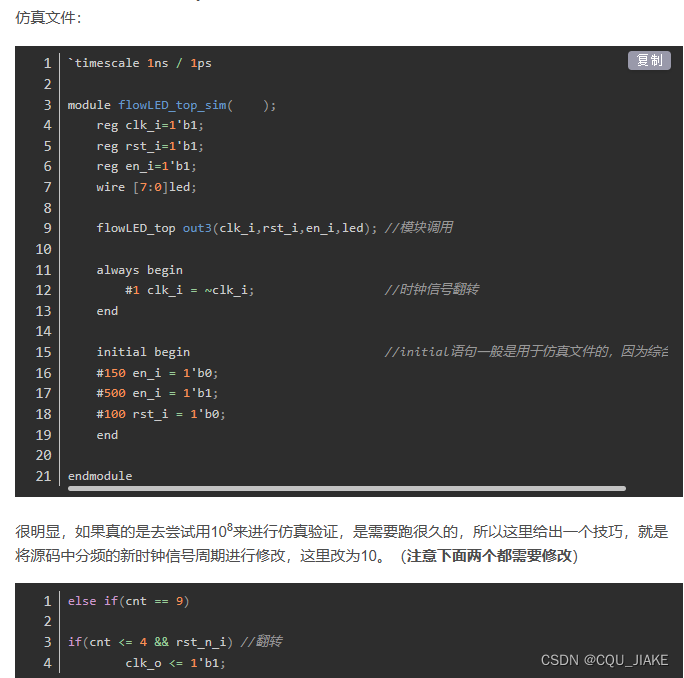

「Verilog学习笔记」状态机与时钟分频

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 状态机写法 `timescale 1ns/1nsmodule huawei7(input wire clk ,input wire rst ,output reg clk_out);//*************code***********//parameter S0 = 0,

FPGA分频电路设计(2)

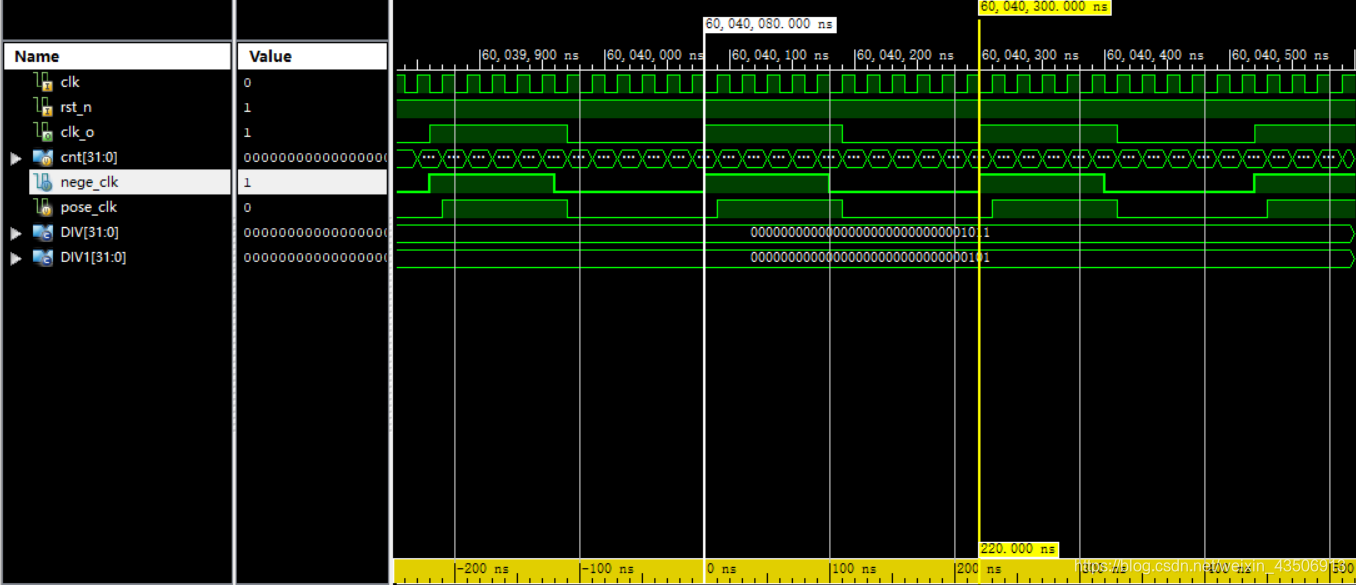

实验要求: 采用 4 个开关以二进制形式设定分频系数(0-10),实现对已知信号的分频。 类似实验我之前做过一次,但那次的方法实在是太笨了: 利用VHDL实现一定系数范围内的信号分频电路 需要重做以便将来应对更大的分频系数 先画个图分析下: 做偶数系数的分频,你只要关注上升沿或下降沿中的其中一种即可,但如果是奇数系数分频,你必须同时关注两种变化。 我的代码: library ieee ;

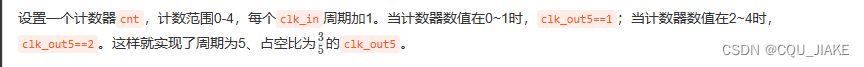

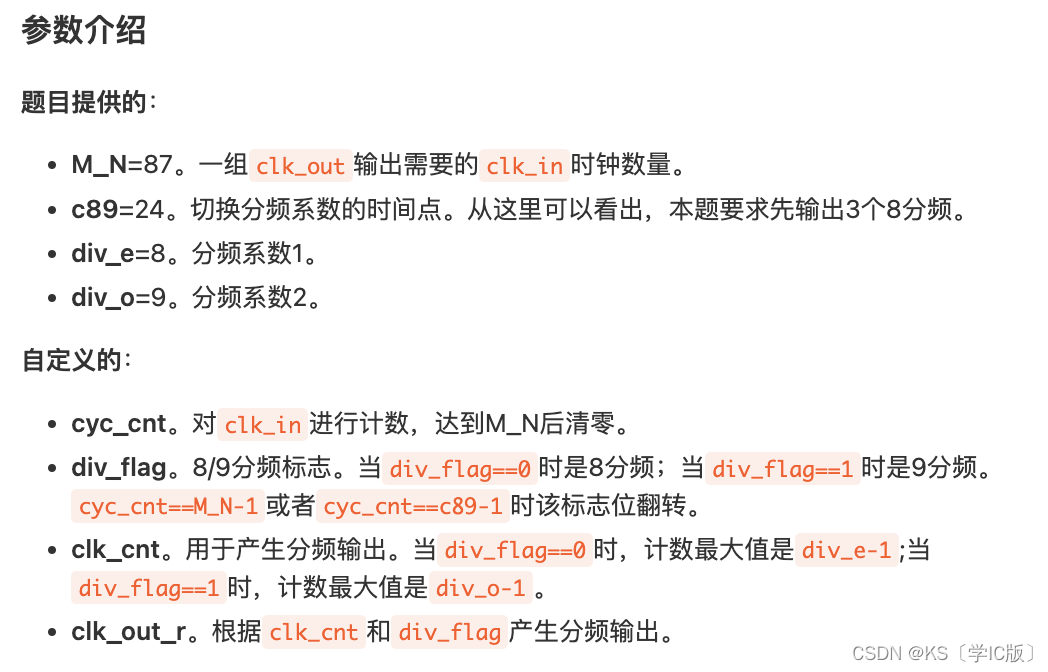

「Verilog学习笔记」任意小数分频

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 `timescale 1ns/1nsmodule div_M_N(input wire clk_in,input wire rst,output wire clk_out);parameter M_N = 8'd87; parameter c89 = 8'd24; //

整数分频,奇偶分频。

实验目标: 实现任意整数奇偶分频。 /* 二分频电路就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。 二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。 比如用一个脉冲时钟触发一个计数器,计数器每计2个数就清零一次并输出1个脉冲。 那么这个电路就实现了二分频功能。 四分频就是通过有分频作用的电路结构,在时钟每触发4个周期时,电路输

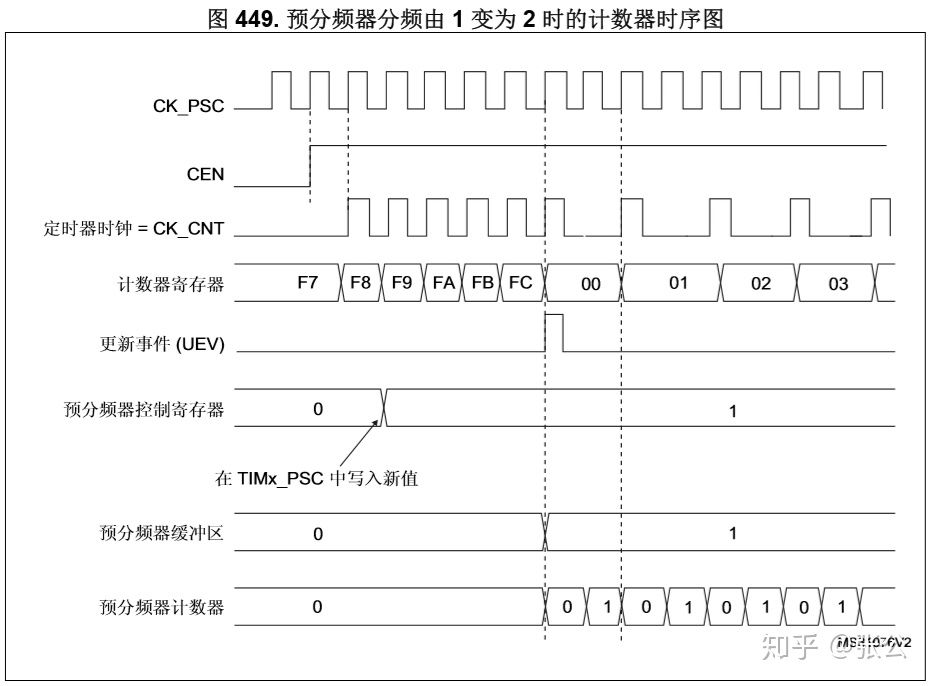

学习笔记——STM32中什么是预分频

在STM32的定时器中,预分频器(Prescaler-PSC)用来将定时器时钟源进行分频输出。 预分频器的值由寄存器TIMx_PSC设定,是一个16位正整数值。 STM32CubeMX中的TIM预分频设置 在STM32系统中,定时器的时钟源为内部时钟时,其频率一般都比较高,以STM32F103的TIM1为例,其总线时钟最大为72MHz,体现在16位的定时器上的效果就是从0计数到65535

PLL中计算目标频率的的M,N分频系数是如何来的?

下图是某款Sunxi平台的时钟树分布图,输入是24MHZ的晶震源,输出则是很多个不同的频点。 一般来讲,输出频率和输入频率满足如下的关系: 这篇文章讨论这个公式的原理和来历。 下图所示的是PLL的基本结构,这是一个负反馈电路,生成时钟信号的核心部分是压控振荡器(Voltage-Controlled Oscillator, VCO),VCO能够根据所加的电压调整频率的振荡器,从图中可

PLL中计算目标频率的的M,N分频系数是如何来的?

下图是某款Sunxi平台的时钟树分布图,输入是24MHZ的晶震源,输出则是很多个不同的频点。 一般来讲,输出频率和输入频率满足如下的关系: 这篇文章讨论这个公式的原理和来历。 下图所示的是PLL的基本结构,这是一个负反馈电路,生成时钟信号的核心部分是压控振荡器(Voltage-Controlled Oscillator, VCO),VCO能够根据所加的电压调整频率的振荡器,从图中可

分频器 偶分频 奇分频 任意分频

今天学习了一下分频器及其Verilog实现 1.偶分频 实现一个NUM_DIV分频的分频器,下面代码中 NUM_DIV= 6,占空比50% 设计代码 module divider_even(clk,rst_n,clk_div);input clk;input rst_n;output clk_div;reg clk_div;parameter NUM_DIV = 6;reg [3:

51单片机12分频 ----- 学习笔记

51单片机12分频的原因 由于初期设计硬件技术缺陷,使执行指令时需要子时钟,就把12个振荡周度期规定为1个机器周期。51单片机是12M晶振,如果是单指令周期的语句,刚好是1us,其他语句好似1us的整数倍,便于计算指令时间。AT公司的AT89系列51单片机,工艺上存在不足,分频后频率降低,程序得以稳定执行,不易跑飞。AT新出的单片机和一些公司出的新单片机不一定要用问12M的晶振,11.05925

数字电路中有关奇数偶数分频心得

1.1偶数分频简介 实现分频一般有两个方法,一个方法是直接使用 PLL 进行分频,比如 FPGA 或者 ASIC 设计中,都可 以直接使用 PLL 进行分频,但是这种分频倍数有时候受限于 PLL 本身的特性,比如输入 100Mhz 时钟,很 多 PLL 都实现不了分频到 1Mhz 的时钟,这个就是 PLL 本身特性限制的。还有一种实现方法就是直接使用 逻辑实现,即使用代码实现分频设计。我们本节介

EDA常用模块 奇数分频 偶数分频 冒泡排序

一、分频 1、偶数分频 .v文件 module FenPin (input clk,input rst,output wire clk_10k);parameter f=8; //即为偶分频的分频数reg [11:0] count=0; //存储分频计数reg clk_10k_tmp=0;assign clk_10k = clk_10k_tmp;// 复位信号rst低

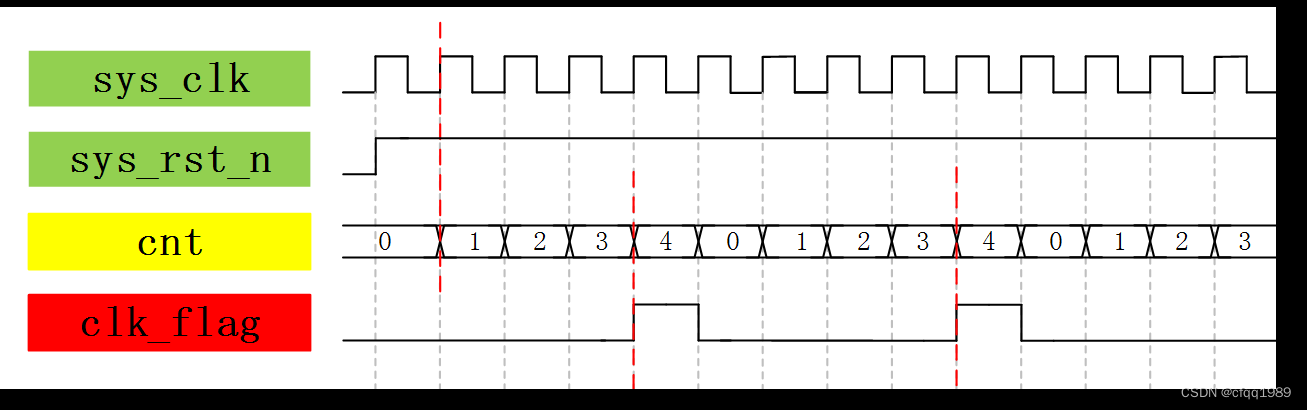

FPGA经典例程2 偶数分频与奇数分频

假设为 N(偶数)分频,只需计数到 N/2-1,然后时钟翻转、计数清零,如此循环就可以得到 N(偶)分频,可以通过改变参量 N 的值和计数变量 cnt 的位宽,实现任意偶分频, 我们由此可以写出如下代码: module Even_division ( input sysclk_i,input rst_n,output reg clk_o);parameter N = 8;reg [N-1