本文主要是介绍【牛客】VL76 任意奇数倍时钟分频,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

描述

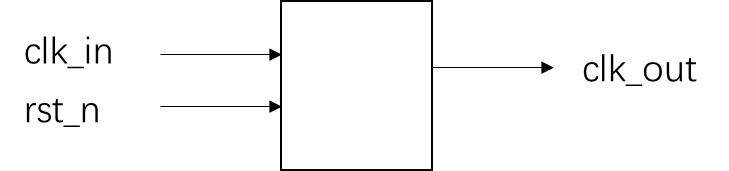

编写一个模块,对输入的时钟信号clk_in,实现任意奇数分频,要求分频之后的时钟信号占空比为50%。模块应包含一个参数,用于指定分频的倍数。

模块的接口信号图如下:

要求:使用Verilog HDL语言实现,并编写testbench验证模块的功能。

输入描述:

clk_in:输入时钟信号

rst_n:复位信号,低电平有效

输出描述:

clk_out:分频之后的时钟信号

`timescale 1ns/1nsmodule clk_divider#(parameter dividor = 5)

( input clk_in,input rst_n,output clk_out

);localparam dividor_sub1 = dividor - 1;

localparam dividor_sub1_div2 = dividor_sub1 / 2;

localparam cnt_r_phase = 1;

localparam cnt_r_init = (4'd0 + dividor_sub1_div2 + cnt_r_phase) % dividor;

localparam cnt_sub1_r_init = (dividor_sub1 + dividor_sub1_div2 + cnt_r_phase) % dividor;reg [3:0] cnt_r = 4'd0, cnt_sub1_r = dividor_sub1;

reg clkout_posedge_r = 1'b0;

reg clkout_negedge_r = 1'b0;

always @(posedge clk_in) beginif (~rst_n) begincnt_r <= cnt_r_init;end else beginif (cnt_r == dividor_sub1) begincnt_r <= 4'd0;end else begincnt_r <= cnt_r + 4'd1;endend

endalways @(posedge clk_in) beginif (~rst_n) begincnt_sub1_r <= cnt_sub1_r_init;end else beginif (cnt_sub1_r == dividor_sub1) begincnt_sub1_r <= 4'd0;end else begincnt_sub1_r <= cnt_sub1_r + 4'd1;endend

endalways @(posedge clk_in) beginif (~rst_n) beginclkout_posedge_r <= 1'b0;end else beginif (cnt_r == 4'd0) beginclkout_posedge_r <= 1'b1;end else if (cnt_r == dividor_sub1_div2) beginclkout_posedge_r <= 1'b0;endend

endalways @(negedge clk_in) beginif (~rst_n) beginclkout_negedge_r <= 1'b0;end else beginif (cnt_r == 4'd0) beginclkout_negedge_r <= 1'b1;end else if (cnt_r == dividor_sub1_div2) beginclkout_negedge_r <= 1'b0;endend

endassign clk_out = clkout_posedge_r | clkout_negedge_r;endmodule

这篇关于【牛客】VL76 任意奇数倍时钟分频的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!