本文主要是介绍数字IC后端实现之Innovus TA-152错误解析(分频generated clock定义错误),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

**ERROR: (TA-152): A latency path from the ‘Fall’ edge of the master clock at source pin…

Error Code

TA-152

在数字IC后端实现innovus中我们经常会看到这类Error,具体信息如下所示。

Error Message

**ERROR: (TA-152): A latency path from the ‘Fall’ edge of the master clock at source pin clk’ to the ‘Rise’ edge of generated clock ‘gen_clk’ at pin ‘gen_clk’ cannot be found. You must modify your create_generated_clock constraint to be consistent with the network topology. The analysis will continue using 0ns source latency for generated clock ‘gen_clk’. For backward compatibility with earlier releases or to remove the edge-to-edge sufficiency checking, you should set the global ‘timing_enable_genclk_edge_based_source_latency’ to false

**ERROR: (TA-152): A latency path from the ‘Rise’ edge of the master clock at source pin ‘clk’ to the ‘Fall’ edge of generated clock gen_clk’ at pin ‘gen_clk’ cannot be found. You must modify your create_generated_clock constraint to be consistent with the network topology. The analysis will continue using 0ns source latency for generated clock ‘gen_clk’. For backward compatibility with earlier releases or to remove the edge-to-edge sufficiency checking, you should set the global ‘timing_enable_genclk_edge_based_source_latency’ to false

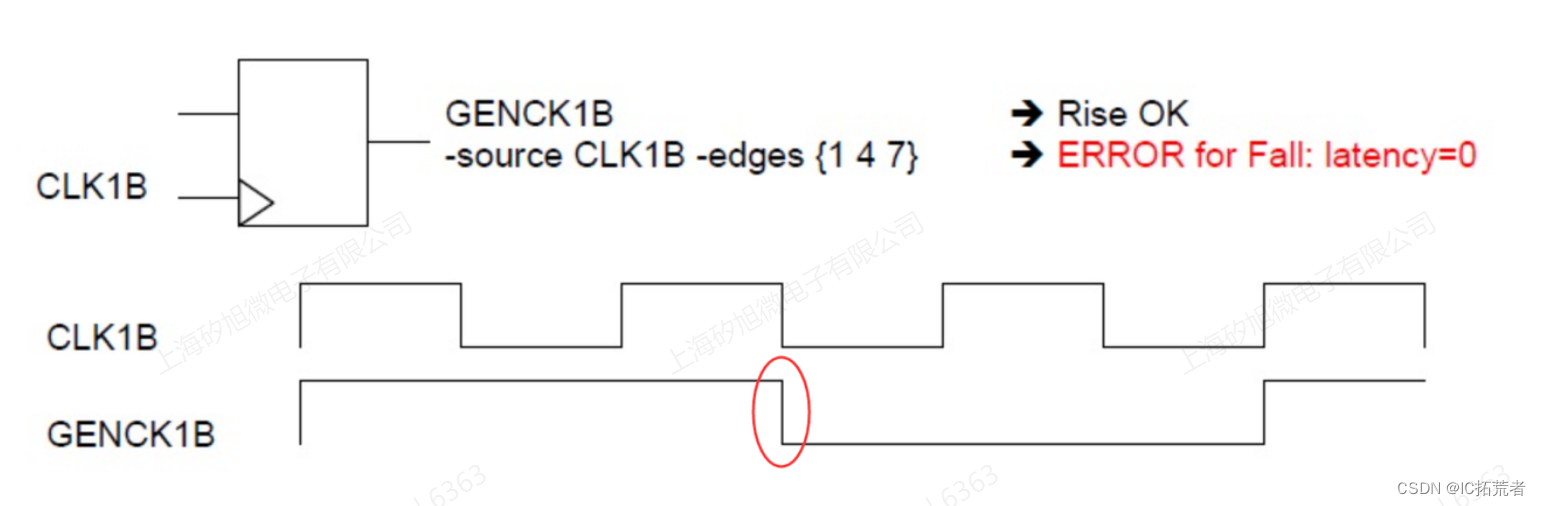

在innovus中出现这个错误,如果是第一次遇到,我们要学会根据工具提示的信息去分析。这里报的是generated clock的rise edge无法从master clock的fall edge获取到。

所以这类问题都是SDC中关于分频时钟的定义有问题。对于后端工程师来说,你可以直接反馈给前端或中端工程师。当然大家也可以研究到底应该怎么去改sdc。

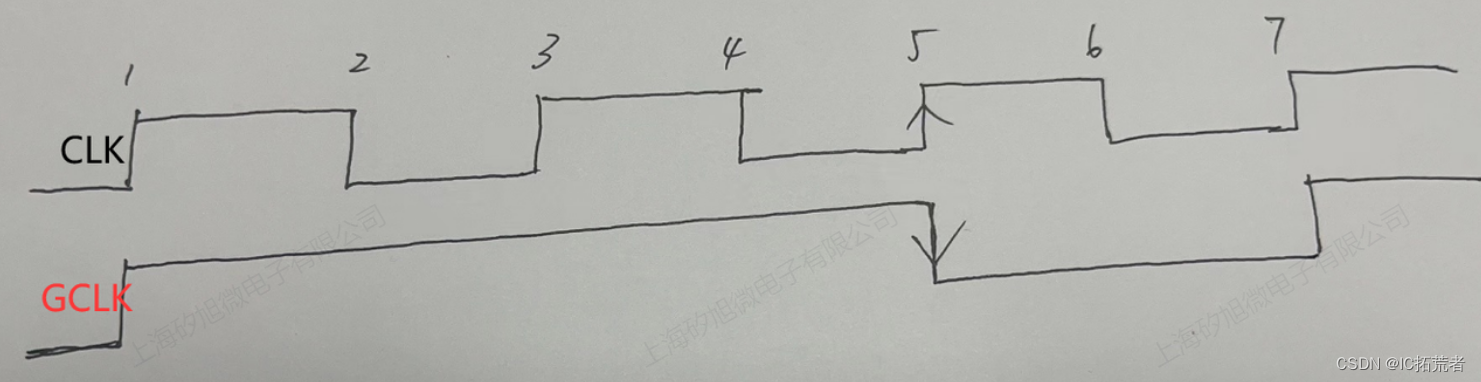

上图所示的三分频电路的时钟应该通过-edge {1 5 7} 来定义,这样工具就不会报这个错误了。

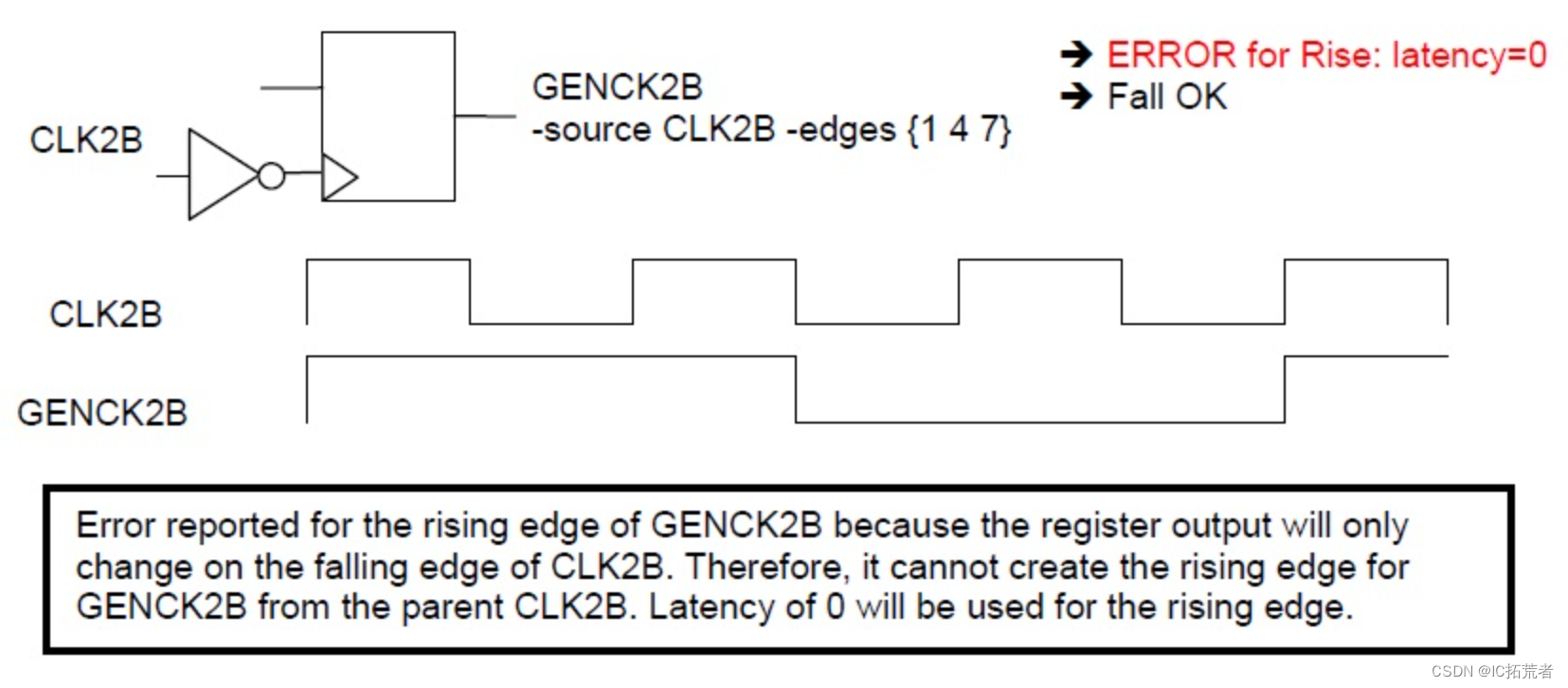

同理,如果source clock经过反相后到底分频寄存器的,那么下图所示的generated clock定义也会有问题。

这个错误不解决带来的后果,欢迎大家交流讨论下。100%是需要解决的!

这篇关于数字IC后端实现之Innovus TA-152错误解析(分频generated clock定义错误)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!