innovus专题

innovus:如何让部分sink长到target insertion delay的长度

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 来自星球提问: 参考命

innovus:report_area和reportGateCount报告module面积的差异

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 相关文章链接:

PT:pt write_change to innovus 脚本

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 #!usr/bin/perl open rf,"$ARGV[0]"; open wf,">test. tcl"; while (<rf>) { s/\[(\D[^\s\]]*)?\]/\\\[$1\\\]/g; if (/current _ instances$/)

Innovus命令合集

以下资料是我之前写过的,芯片数字后端中的一些Encounter/Innovus命令的中文介绍,主要是Floorplan部分,接下来会新增Timing部分命令介绍。整理了一下,做成合集,方便大家查询,按照字母顺序从下往上排列。 点击标题就可以选择文章查看,会直接挂在公众号的主页菜单栏里的“资料合集”里,感觉好的话,请多多推广喔~~

《数字版图设计实训》(Innovus/Encounter) 开课通知

课程简介 数字版图设计即利用EDA工具,实现自动布局布线,完成从netlist到GDS的转变。作为数字ASIC设计流程中的最后一步,数字版图设计是最重要的一个环节,决定着芯片设计成功与否。 随着工艺尺寸发展的越来越小,20nm以下的设计越来越成为设计主流。原有的EDA工具已经无法设计更为先进的工艺节点,作为IC设计的上游,各家EDA公司也争相推出第二代的后端设计工具。Innovus,作为第一代

Innovus/Encounter时序报告解读

最近在学report_timing这个命令,发现自己对timing report的认知只停留在看slack和delay数值上。于是,决定研究一下这个report。Innovus/Encounter的report格式确实有点不按套路出牌,初看有点凌乱。以下只是我的一些简单认识,各位timing大神可以直接忽略,希望对新人会有帮助: 首先,我们来看一条简单的timing path report

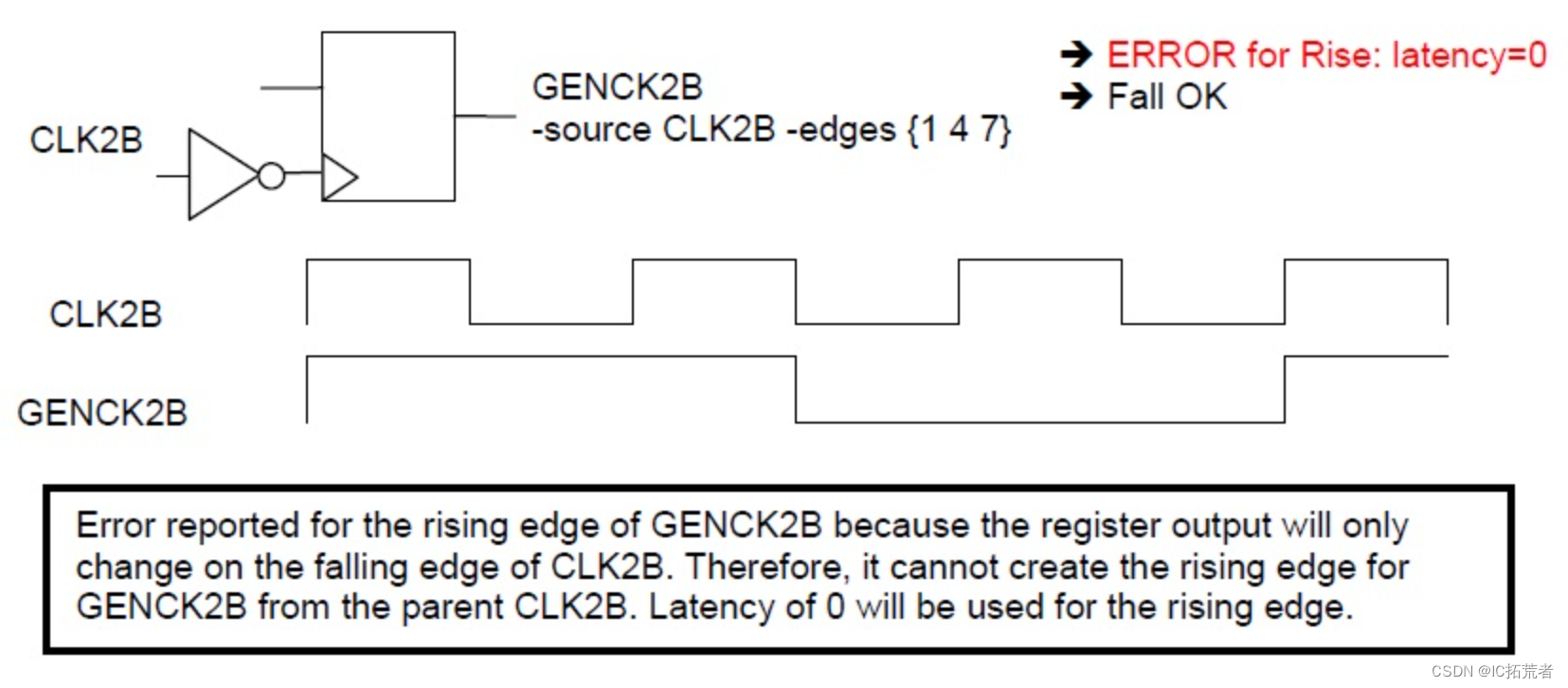

数字IC后端实现之Innovus TA-152错误解析(分频generated clock定义错误)

**ERROR: (TA-152): A latency path from the ‘Fall’ edge of the master clock at source pin… Error Code TA-152 在数字IC后端实现innovus中我们经常会看到这类Error,具体信息如下所示。 Error Message **ERROR: (TA-152): A latency pa

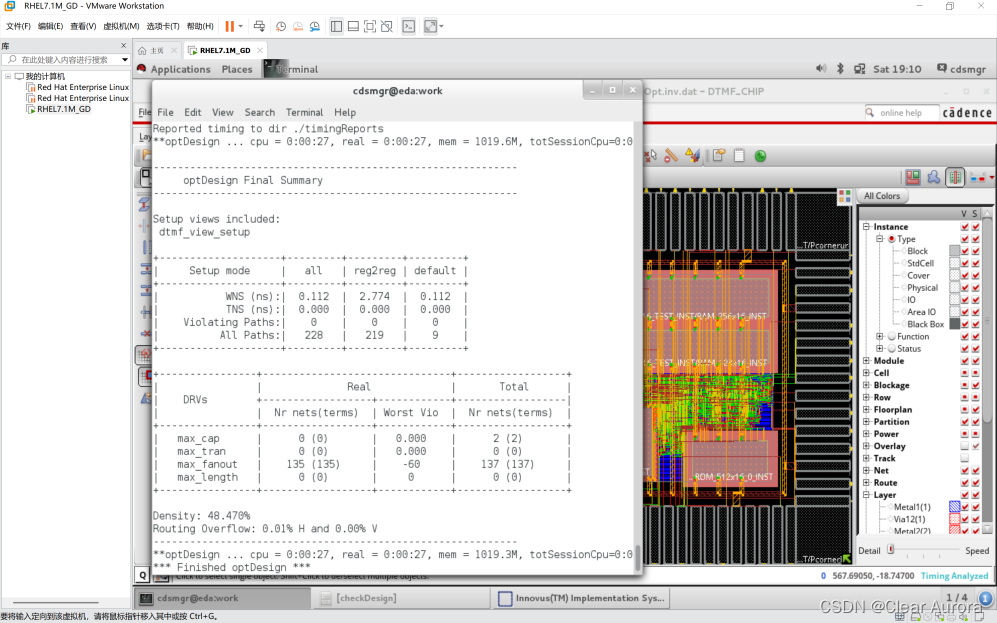

数字IC后端实现之快速获取innovus中drv violation的所有net list

在Innovus中place_opt_design和optDesign阶段,我们经常会看到如下所示的log提示信息,核心关键词是“ Reasons for remaining drv violations”。而且告诉我们总共有819条net存在drv violation,且无法被工具优化掉。 ====================================================

innovus:ccopt_design (1) check_prerequisites

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 相关文章链接 ICC2(三)CTS 阶段常用命令 ccopt_design -check_prerequisitessites类似与ICC2的report_clock_setting命令,可以报告clock tree需要用到的clock cell list/target 约束等等,详细内容可

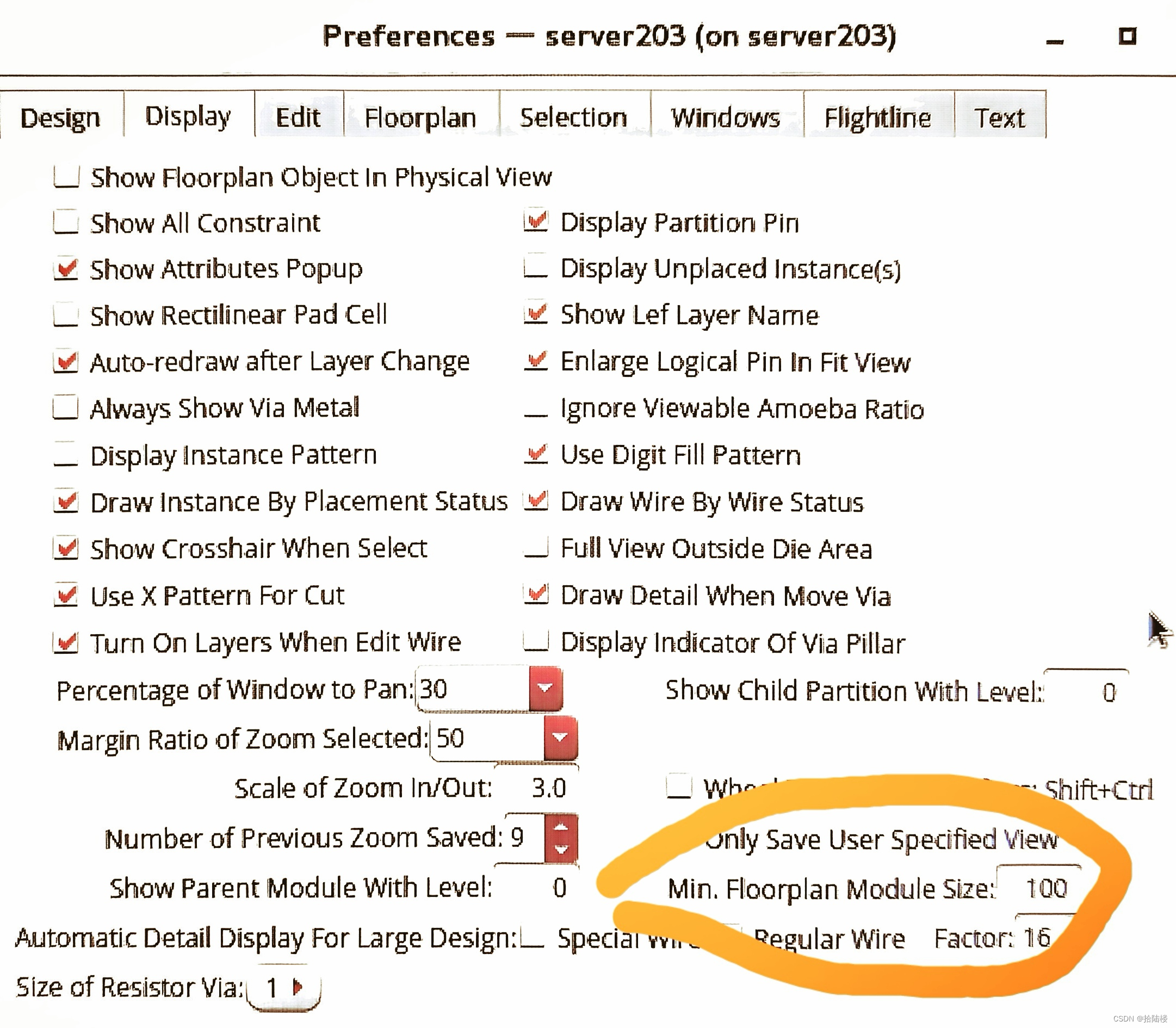

innovus如何在floorplan view显示所有module

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 如题,innovus的图形界面在floorplan view下默认只能显示instance数量超过100个的module,如果要显示更小的module,需要在VIEW-Set Perference改一下Min.Floorplan Module Size选项。如下图所示:

innovus如何在floorplan view显示所有module

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 如题,innovus的图形界面在floorplan view下默认只能显示instance数量超过100个的module,如果要显示更小的module,需要在VIEW-Set Perference改一下Min.Floorplan Module Size选项。如下图所示:

innovus:如何在init design之后新增参考库(lib/lef)

如题,在PR过程中经常会遇到这种问题,时序无法收敛,需要新增一套lvt或者hpc的库,怎么办? 1.仅更新lef innovus > loadLefFile 2.更新lef+lib 1)找到当前设计的$design.dat/libs/lef目录,把新增的lef copy进来; 2)修改$design.dat/$design.globals文件,参考init_lef_lef格式,列表

innovus:解决报告复制时一行拆成两行的问题

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? innovus复制报告时一行的东西出现在两行上,解决只需要一条命令: set_table_style -no_frame_width

innovus: 如何写出floorplan和power信息

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 相关文章链接: innovus 报告多边形floorplan的boundary坐标 defOut 如果是自己用的floorplan信息可用如下命令: defOut -floorplan -allLayers fp.def 如果是dcg需要的纯floorplan信息用如下命令: defOu

innovus:如何解决editAddRoute不能在平行线间打孔的问题

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 用户使用editAddRoute命令或者图形界面手动拉线,默认只能在相同net 的不同层net shape crossover(交叉)位置上打孔,如图右侧GNDD交叉的位置有打孔,而左侧平行的两条net shape无法自动打孔。 有两种方法解决这个问题: setEditMode -orthogonal

innovus:报告到clock root物理距离最远的sink

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球入口 分析clock tree的时候可以看到一些delay detour buffer,其作用是为了满足balance的要求不得已去垫delay,在版图上兜兜绕绕的插buffer,这时候分析就需要找到把它们拉长的原因,单纯分析latency最到的部分sink未必能找到原因,而找到距离root最远的sink也有很高的参考价

数字集成电路后端(Innovus)开发设计

一、本文目的是对数字IC进行: 1、平面规划设计(Floorplanning the Design); 2、电源路径设计(Routing Power with Special Route); 3、使用Early Global Router分析路径(布线)可行性(Analyzing Route Feasibility with the Early Global Router)。

innovus 报告多边形floorplan的boundary坐标

我正在「拾陆楼」和朋友们讨论有趣的话题,你⼀起来吧? 拾陆楼知识星球 历史文章: 常用dbGet命令 dbGet快速入门 使用"Cut Rectilinear"功能可以调整floorplan形状,使其变成非矩形多边形(polygon)。 Floorplan-Edit Floorplan-Cut Rectilinear 需要注意的是: 1) 此时layout应该处于

innovus之property

做IC后端工程师,和tool打交道是数不胜数的,记得最初想实现某个功能,试了很多办法,大多过于繁琐不够简洁,后来接触到一些command觉得真是瞬间晴空万里。把一些遇到很有帮助的经验记录下来,希望能帮助到和我一样的小白。 今天要介绍的是object的property property 是object的一些特性,或者属性值。常见的有clock的period, datapath的slac