本文主要是介绍Verilog经典题(三)——偶分频、奇分频,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

文章目录

- 偶分频

- 思路(看着就知道咋写的快速回顾)

- 代码

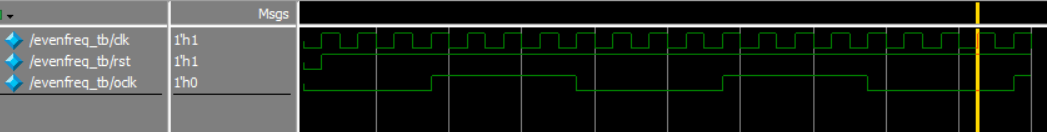

- 波形

- 奇分频

- 思路

- 代码

- 波形

偶分频

占空比50%的偶分频

思路(看着就知道咋写的快速回顾)

- 参数DivNum定义几分频

- 输入clk,rst 输出oclk,中间计数器count,tmp

- 0 1 2 3 置高,4 5 6 7 置低

if(count == ((DivNum>>1) - 1)) begincount <= count + 1; tmp <= 1'b1;

end

else if(count == (DivNum - 1)) begincount <= 0;tmp <= 1'b0;

end

elsecount <= count +1;

代码

Verilog

module evenfreq

#(parameter DivNum = 8

)(input clk,input rst,output oclk

);reg [2:0] count;reg tmp;always @(posedge clk or negedge rst)beginif(!rst) begincount <= 0;tmp <= 0;endelse beginif (count == DivNum - 1) begincount <= 0;tmp <= 0;endelse if (count == (DivNum>>1) - 1)begincount <= count + 1 ;tmp <= 1; endelse count <= count + 1 ;endendassign oclk = tmp;

endmodule

tb

module evenfreq_tb();reg clk;reg rst;wire oclk;initial beginclk = 0;rst = 0;# 5 rst = 1;endinitial beginforever #5 clk = ~clk;end evenfreq tb1(.clk(clk),.rst(rst),.oclk(oclk));

endmodule

波形

奇分频

占空比为50%的奇分频

思路

- 参数DivNum用来设置分频数

- 用clk上升沿分频出“3高4低”的7分频tmp

再用clk下降沿分频出“3高4低”的7分频tmp1

将tmp与tmp1相或即可得到占空比50%的7分频oclk - 输入clk,rst输出oclk

if(count1 == DivNum-1)begincount1 <= 0;tmp1 <= 0;

end

else if(count1 == (DivNum-1) >> 1)begincount1 <= count1 + 1;tmp1 <= 1;

end

else count1 <= count1 + 1;

代码

Verilog

代码中opsd,ongd,c1,c2为方便观看波形,实际输出并不需要

module oddfreq

#(parameter DivNum = 9

)

(input clk,input rst,output opsd, //上升沿控制输出output ongd, //下降沿控制输出output [DivNum:0]c1, //上升沿计数器output [DivNum:0]c2, //下降沿计数器output oclk

);reg [DivNum:0] count1;reg [DivNum:0] count2;reg tmp1;reg tmp2;always @(posedge clk or negedge rst)beginif(!rst) begincount1 <= 0;tmp1 <= 0;endelse begin if(count1 == DivNum-1)begincount1 <= 0;tmp1 <= 0;endelse if(count1 == (DivNum-1) >> 1)begincount1 <= count1 + 1;tmp1 <= 1;endelse begin count1 <= count1 + 1;endendendalways @(negedge clk or negedge rst)beginif(!rst) begincount2 <= 0;tmp2 <= 0;endelse begin if(count2 == DivNum-1)begincount2 <= 0;tmp2 <= 0;endelse if(count2 == (DivNum-1) >> 1)begincount2 <= count2 + 1;tmp2 <= 1;endelse count2 <= count2 + 1;endendassign c1 = count1;assign c2 = count2;assign opsd = tmp1;assign ongd = tmp2;assign oclk = tmp1 || tmp2;

endmodule

tb

module oddfreq_tb();reg rst;reg clk;wire [7:0]c1;wire [7:0]c2;wire opsd;wire ongd;wire oclk;initial beginclk = 0;rst = 0;# 5 rst = 1;endinitial beginforever #5 clk = ~clk;end oddfreq tb1(.clk(clk),.rst(rst),.c1(c1),.c2(c2),.opsd(opsd),.ongd(ongd),.oclk(oclk));

endmodule

波形

参考https://blog.csdn.net/xvrixingkong/category_10393817.html

有没有大佬热心告知我波形能直接导出吗?截图好像有点low而且不太清楚。还有还有 为什么我的代码块没有颜色的区别??

这篇关于Verilog经典题(三)——偶分频、奇分频的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!