verilog专题

数字电路专题:verilog 阻塞赋值和非阻塞赋值

verilog 阻塞赋值 和 非阻塞赋值 “=”阻塞赋值, ”<=”非阻塞赋值。阻塞赋值为执行完一条赋值语句,再执行下一条,可理解为顺序执行,而且赋值是立即执行; 非阻塞赋值可理解为并行执行,不考虑顺序,在 always 块语句执行完成后,才进行赋值。 如下面的阻塞赋值: //代码如下:module top(din,a,b,c,clk);input din;input clk;out

systemverilog、verilog的部分常用内部函数

1. $ceil 作用:将给定的实数或浮点数向上取整。示例:$ceil(3.2) 返回 4。 2. $floor 作用:将给定的实数或浮点数向下取整。示例:$floor(3.9) 返回 3。 3. $value$plusargs 作用:从命令行读取传递给仿真器的参数。格式:$value$plusargs("格式", 变量),格式 用来匹配命令行的参数,变量 是用来存储匹配到的值。示例:$

Verilog语法+:和-:有什么用?

Verilog语法+:和-:主要用于位选择,可以让代码更简洁。 一、位选择基础 在Verilog中,位选择可以通过直接索引来实现,例如: reg [7:0] data; wire select_a; wire [2:0] select_b; assign select_a = data[3]; assign select_b = data[2:0]; 二、+: 和 -: 语法

Verilog和Matlab实现RGB888互转YUV444

文章目录 一、色彩空间1.1 RGB色彩空间1.2 CMYK色彩空间1.3 YUV色彩空间 二、色彩空间转换公式2.1 RGB转CMYK2.2 CMYK转RGB2.3 RGB888转YUV4442.4 YUV444转RGB888 三、MATLAB实现RGB888转YUV4443.1 matlab代码3.2 matlab结果 四、Verilog实现RGB888转YUV444 一、

FPGA第 10 篇,Verilog 中的运算符和分支语句

前言 我们都知道 Verilog 作为一种硬件描述语言,不仅用于设计和仿真数字电路,还为开发者提供了强大的工具,用于控制和优化硬件的行为。其中运算符和分支语句是 Verilog 中的两大核心组成部分,它们负责执行逻辑操作、数学运算以及决定逻辑流的控制。 运算符 在 Verilog 中用于进行各种计算和逻辑操作,它们类似于软件编程中的运算符,但特定于硬件操作,涵盖了算术、逻辑、按位操作、移位操

verilog仿真激励

简介 本章节主要描述verilog激励仿真函数的介绍。 initial 主要针对寄存器初始化值,基本所有仿真都会使用到该语句,使用如下: initial beginsys_clk = 'd0; sys_rst_n = 'd0; #2000;sys_rst_n = 'd1; end repeat 重复有限次数地执行一段代码,使用如下:

verilog语法错误

1.写敏感列表always(@posedge or @negedge ext_rst_n),语法检查报错ERROR:HDLCompiler:806 - "E:\ISE14.6\Project\sp6\sp6ex1\source_code\sp6.v" Line 27: Syntax error near "(".仔细检查应为always @(posedge ext_clk_25m or neged

在使用VScode自动生成verilog testbench文件时,提示No module named 'chardet'

https://www.cnblogs.com/whylinux/p/9839162.html 解决方法为: pip install certifi pip install chardet pip install idna pip install urllib3

FPGA第 8 篇,硬件描述语言Verilog HDL,初识Verilog HDL

前言 我们都知道 FPGA 是一种高度可编程的集成电路,适用于实现各种数字逻辑功能,而 Verilog HDL是一种广泛使用的硬件描述语言(Hardware Description Language, HDL),主要用于数字电子系统的描述、仿真和综合,以及其他数字系统的逻辑设计。通过使用 Verilog,工程师可以高效地设计和验证 FPGA 电路,从而实现所需的数字系统功能。

Verilog刷题笔记62

题目: Exams/review2015 fancytimer This is the fifth component in a series of five exercises that builds a complex counter out of several smaller circuits. You may wish to do the four previous exercises

Verilog实现VGA显示控制器

Verilog实现VGA显示控制器具体原理就不详细讲了,这里给出完整的代码以及Nexys3开发板的引脚文件。最终实现的效果是:以 640*480 的分辨率在显示器屏幕显示一个矩形方块,方块在屏幕中以 45 度的角度、60 像素/秒的速度移动,到达屏幕边沿的时候反弹。Verilog代码 收藏代码// 设计文件:vga_controller.v `timescale 1ns / 1ps modu

Nexy3开发板Verilog Demo

Nexys3开发板Verilog Demo这个学期开始学FPGA开发,使用的开发板是Nexys3,硬件编程语言是Verilog。苦于之前一直没有找到很好的代码学习资料,于是在这里将自己写过的一些相对简单的代码整理了一下分享开来,希望能对各位初学者有所帮助。本文提供的Verilog代码都是属于Demo级别的,不过限于本人水平,也不免会有一些瑕疵,这里仅供参考,还请各位慎思!(“博学、审问、慎思、明

FPGA开发——使用verilog实现异步FIFO

一、FIFO 介绍 1、FIFO的分类 FIFO ( First In First Out)先进先出存储器。根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。 FIFO 底层是基于双口 RAM ,同步 FIFO 的读写时钟一致,异步 FIFO 读时钟和写时钟不同。 作用: 同步 FIFO:主要用于数据缓冲,类似于乒乓缓存思

Verilog刷题笔记59

题目: Exams/m2014 q6c 解题: module top_module (input [6:1] y,input w,output Y2,output Y4);assign Y2=y[1]&w==0;assign Y4=(y[2]&w==1)|(y[3]&w==1)|(y[5]&w==1)|(y[6]&w==1);endmodule 结果正确: 注意点: 起初,我的代码有错误

verilog中$clog2

在Verilog中,$clog2 是一个系统任务(system task),用于计算并返回给定值以2为底的对数的向上取整结果。这个函数在处理位宽相关的计算时非常有用,尤其是在需要自动根据变量的大小确定位宽的场景中。 $clog2 的使用非常直接,其语法如下: integer result; result = $clog2(value); 这里,value 是你想要计算其以2为底的对数的值

verilog中两个常数相除

在Verilog中,两个常数(即编译时已知的值)相除,其结果的处理方式取决于几个因素,包括这些常数的类型(整数还是实数)、Verilog的版本(Verilog-2001之前的版本与SystemVerilog有所不同,尽管后者在很大程度上与Verilog兼容并扩展了其功能),以及你期望的结果类型。 整数除整数 如果两个操作数都是整数,那么结果也将是整数,并且结果会向下取整(即,丢弃小数部分)。这

Verilog刷题笔记55

题目: Exams/ece241 2014 q5a You are to design a one-input one-output serial 2’s complementer Moore state machine. The input (x) is a series of bits (one per clock cycle) beginning with the least-signifi

Verilog刷题笔记54

题目: Fsm serialdp See also: Serial receiver and datapath We want to add parity checking to the serial receiver. Parity checking adds one extra bit after each data byte. We will use odd parity, where t

【FPGA】`include 和 verilog header的区别

作用域区别 include 是把文件 粘贴到当前位置,作用域也仅限当前文件header 作用域是整个工程 .f添加方式的区别 include “xxx.v” 写在当前文件中,.f文件无需另外添加header文件用+incdir+./…/pathname/ fpga添加方式的区别 include “xxx.v” 写在当前文件中,.f文件无需另外添加header文件需要设置filetype

Verilog中端口应该设置为wire形还是reg形

初学Verilog时,一直搞不清Verilog描述模块时端口应该取什么类型;是reg形?还是wire形?模块对应测试文件的端口类型为什么又与模块的端口类型不一样?因此有必要进行学习与整理: 先写结论: verilog中的端口具有三种传输方向:input、output、和inout,所有的端口均默认为wire类型; 模块描述时,input端口只能为线网形,output端口可以为线网/reg,in

模拟14位相机输出输入到bram Verilog代码

1 模拟输出代码 `timescale 1ns / 1psmodule simulate_camera_out (input clk,input rest_n,output camera_clk, //像素时钟output [13:0] camera_data, //像素值数据output [19:0] pixel_xy, //此时输出的像素值坐标output reg frame_vali

模拟14位相机输出Verilog代码

1 代码 `timescale 1ns / 1psmodule simulate_camera_out (input clk,input rest_n,output camera_clk, //像素时钟output [13:0] camera_data, //像素值数据output [19:0] pixel_xy, //此时输出的像素值坐标output reg frame_valid /

Verilog综合出来的图

Verilog写代码时需要清楚自己综合出来的是组合逻辑、锁存器还是寄存器。 甚至,有时写的代码有误,vivado不能识别出来,这时打开综合后的schematic简单查看一下是否综合出想要的结果。 比如:误将一个always模块重复一遍,vivado没有识别出来导致没有生成想要的状态机,打开综合后的schematic一看,被优化掉了。 一、部分Verilog语句综合出来的原理图 1.1

Verilog-Behavior Level 和 RTL Level 和 GATE Level的区别

硬件设计中对硬件的描述可以具有不同的抽象级别,以Verilog为例: Behavior Level。描述的是硬件的行为,当我们在看到如下关键字时就是行为级别的代码:#,wait,while,force,release等,行为级别的代码通常比较直观,但可能不可综合。RTL Level。RTL即Register Transfer Level寄存器传输级别,使用always和assign语句块组成的代

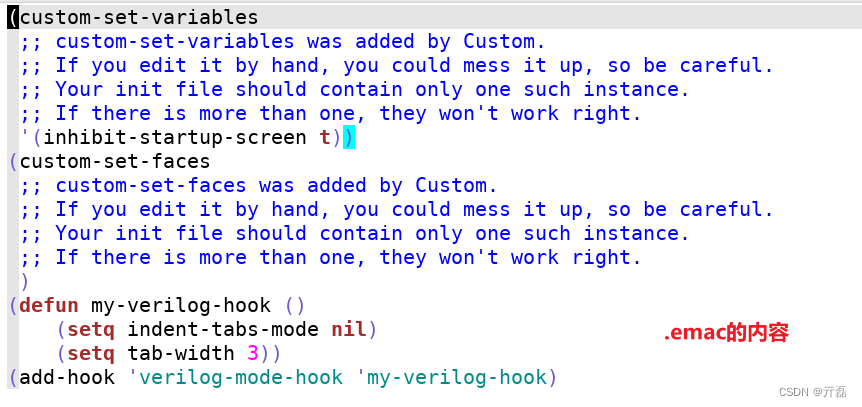

emacs evil-matchit实现verilog配对的代码跳转

背景emacs插件evil-matchit参考文档 背景 vim里常使用%进行跳转。遇到代码段较长的情况,跳转方便而且有助于debug。 vim 实现begin end 配对 使用matchit插件 - 岁月长河 - 博客园 http://www.cnblogs.com/air-of-code/p/4733151.html emacs怎么搞? emacs插件evil-

emacs verilog-mode方式实现verilog实例化集成

文章目录 背景介绍AUTOINST和AUTOWIRE的应用推荐使用方法auto_template命令总结[],中括号,里面没内容。表示auto_inst时,会显示[3:0]类似内容@,常用于相同module,多次实例化情况。我不常用。这里仅是提一下有这种功能。下面第一段,表示auto_template有一个可选变量,支持正则表达式;如果没有正则表达,@符号就会默认匹配实例化名称里的 **数字