本文主要是介绍FPGA经典例程2 偶数分频与奇数分频,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

假设为 N(偶数)分频,只需计数到 N/2-1,然后时钟翻转、计数清零,如此循环就可以得到 N(偶)分频,可以通过改变参量 N 的值和计数变量 cnt 的位宽,实现任意偶分频, 我们由此可以写出如下代码:

module Even_division

( input sysclk_i,input rst_n,output reg clk_o

);

parameter N = 8;

reg [N-1:0] cnt;

always @ (posedge sysclk_i or negedge rst_n) begin

if (!rst_n) begin

clk_o <= 1'b0;

cnt <= 0;

end

else begin if (cnt== N/2-1) begin clk_o <= ~ clk_o;cnt<=0;end

elsecnt<=cnt+1'b1;end

end

endmodule

testbench代码:

module tb_Even_division

();

reg sysclk_i;

reg rst_n;

wire clk_o;always #10 sysclk_i = ~ sysclk_i;

initial begin sysclk_i <= 0;rst_n <= 1'b0;#100 rst_n <= 1'b1;

end

Even_division u_Even_division

(.sysclk_i (sysclk_i),

.rst_n (rst_n),

.clk_o (clk_o)

);endmodule

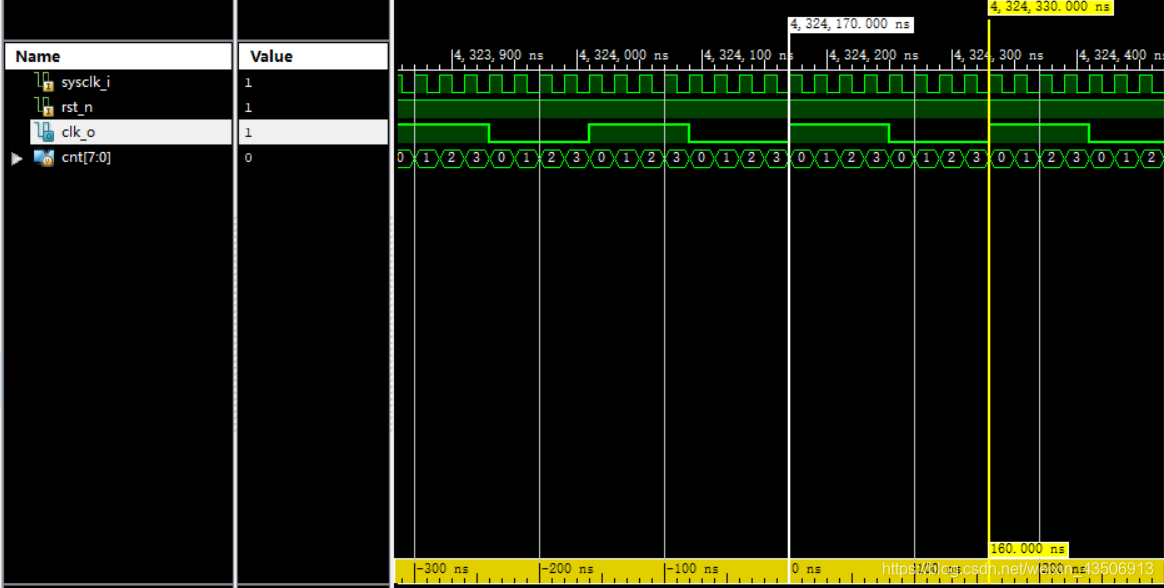

波形:

奇数分频代码:

module odd_division(input sysclk,input rst_n,output clk_out);

parameter N = 5;

reg [N/2:0] cnt1;

reg [N/2:0] cnt2;

reg clk_o1,clk_o2;

always @(posedge sysclk or negedge rst_n) begin if (!rst_n) beginclk_o1 <= 0;cnt1 <= 1;endelse begin if (clk_o1 == 0) begin if (cnt1==N/2+1) begin clk_o1 <= ~clk_o1;cnt1 <= 1;endelse cnt1 <= cnt1 + 1'b1;endelse if (clk_o1==1) begin if (cnt1==N/2) begin clk_o1 <= ~clk_o1;cnt1 <= 1;endelse cnt1 <= cnt1 +1;endend

end

always @(negedge sysclk or negedge rst_n) begin if (!rst_n) beginclk_o2 <= 0;cnt2 <= 1;endelse if (clk_o2 == 0) beginif (cnt2==N/2+1) begin clk_o2 <= ~clk_o2;cnt2 <= 1;endelse cnt2 <= cnt2 +1;endelse if (clk_o2 == 1) begin if (cnt2==N/2) beginclk_o2 <= ~clk_o2;cnt2 <=1;endelse cnt2 <= cnt2 +1;end

end assign clk_out = clk_o1 | clk_o2;

endmodule

testbench :

`timescale 1ns / 1ps

module tb1;// Inputsreg sysclk;reg rst_n;// Outputswire clk_out;// Instantiate the Unit Under Test (UUT)odd_division uut (.sysclk(sysclk), .rst_n(rst_n), .clk_out(clk_out));

always #10 sysclk <= !sysclk;initial begin// Initialize Inputssysclk = 0;rst_n = 0;// Wait 100 ns for global reset to finish#100;rst_n = 1; // Add stimulus hereendendmodule

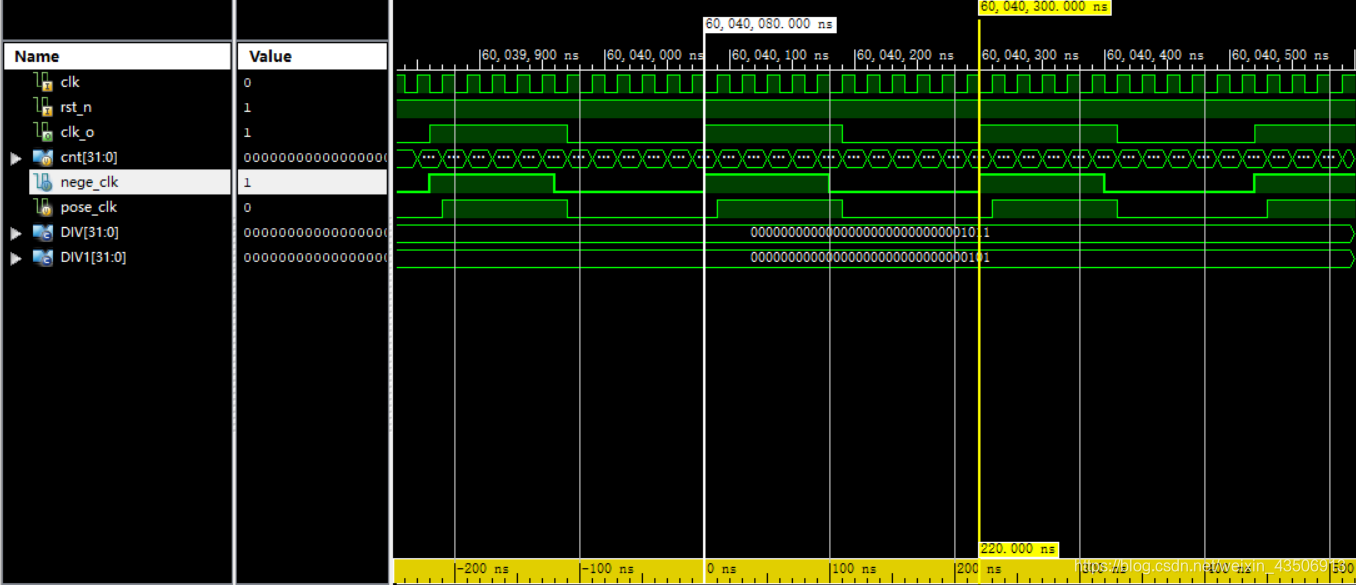

仿真:

这篇关于FPGA经典例程2 偶数分频与奇数分频的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!