ultrascale专题

petalinux,Zynq UltraScale+ MPSoC;WARNING: Failed to load PMUFW, doesn't exist in pre-built.

petalinux-package --pmufw ./images/linux/pmufw.elf 这个参数貌似没有生效; 解决办法: cp images/linux/pmufw.elf ./pre-built/linux/images/

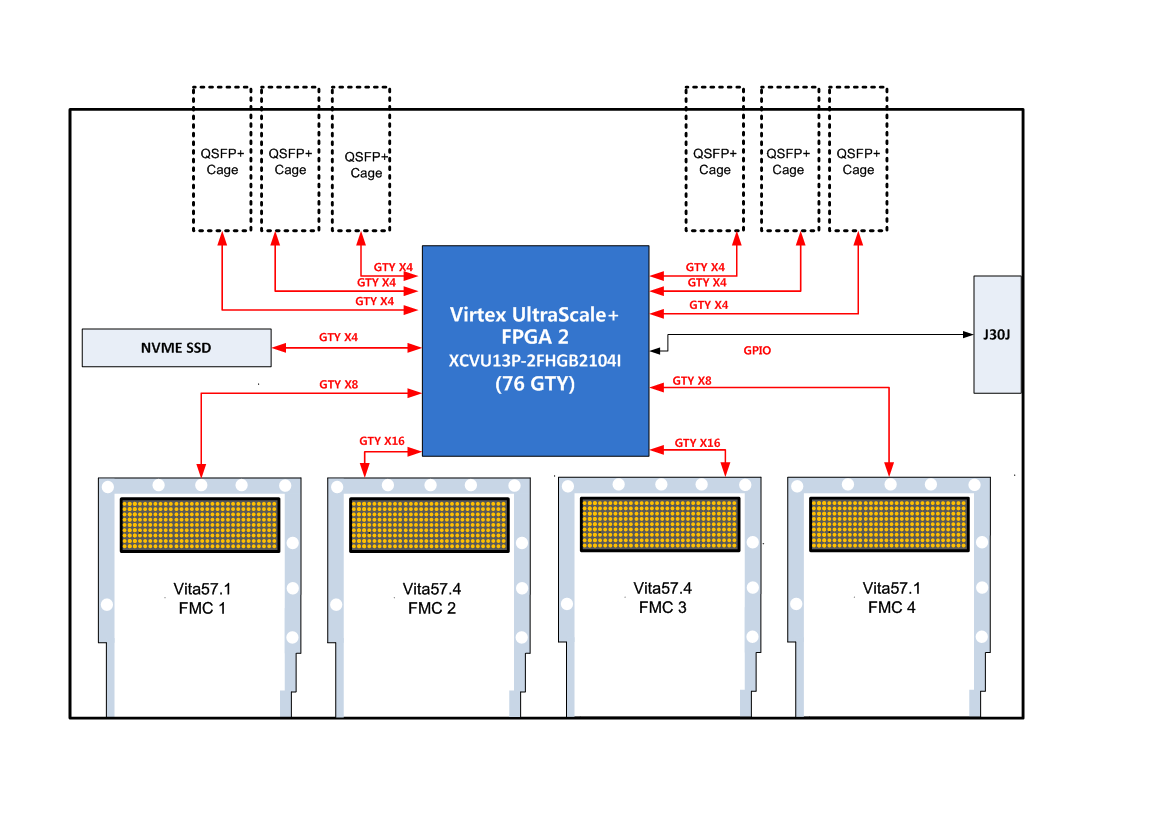

基于Virtex UltraScale+ VU13P FPGA的4路FMC接口基带信号处理平台

Virtex UltraScale+系列 FPGA处理器:XCVU13P-2FHGB2104I动态存储数量:2组DDR4 SDRAM动态存储容量:每组4GByte,每个颗粒为8GBit动态存储带宽:工作时钟1000MHz,数据率2000Mbps板载6路QSFP+光纤接口板载4个FMC+高速扩展接口 基于Virtex UltraScale+系列FPGA的高性能4路FMC接口基带信号处理平台,该

Ultrascale/+的SYSMON获取温度值

XADC与SYSMON SYSMON结构框图 参考电压 有两种形式提供参考电压:外部供电和内部供电。 源语结构 温度计算 SYSMONE1 使用内部参考电压的话,计算公式如下: 通过ADC Code来计算温度的公式: 通过温度来计算ADC Code的公式: 举例:获取到的16bit的Code值为38940(981Ch),取其高10bit后为608(2

UltraScale Soft Error Mitigation

https://forums.xilinx.com/t5/%E5%85%B6%E4%BB%96FPGA%E5%99%A8%E4%BB%B6%E6%9E%B6%E6%9E%84/Xilinx-%E8%BD%AF%E9%94%99%E8%AF%AF%E7%BC%93%E8%A7%A3-SEM-IP%E5%86%85%E9%83%A8%E5%B7%A5%E4%BD%9C%E6%9C%BA%E7

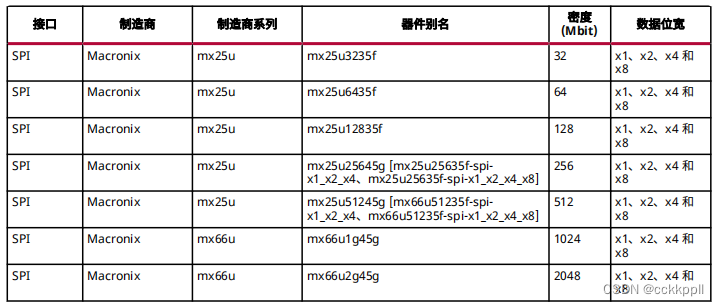

vivado Kintex UltraScale+ 配置存储器器件

Kintex UltraScale+ 配置存储器器件 下表所示闪存器件支持通过 Vivado ® 软件对 Kintex UltraScale+ 器件执行擦除、空白检查、编程和验证等配置操作。 本附录中的表格所列赛灵思系列非易失性存储器将不断保持更新 , 并支持通过 Vivado 软件对其中所列非易失性存储器 进行擦除、空白检查、编程和验证。赛灵思竭尽所

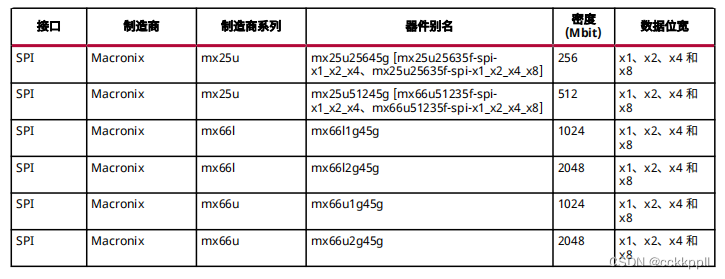

vivado Kintex UltraScale 配置存储器器件

Kintex UltraScale 配置存储器器件 下表所示闪存器件支持通过 Vivado ® 软件对 Kintex UltraScale 器件执行擦除、空白检查、编程和验证等配置操作。 本附录中的表格所列赛灵思系列非易失性存储器将不断保持更新 , 并支持通过 Vivado 软件对其中所列非易失性存储器 进行擦除、空白检查、编程和验证。赛灵思竭尽所能保

产品推荐 | 基于 Zynq UltraScale+ RFSoC 的iW-RainboW-G42M 核心板

01 产品概述 Xilinx Zynq UltraScale+基于RFSoC的系统模块采用带有FFVF1760封装的Zynq Scale+RFSoC ZU49/ZU39/ZU29设备。RFSoC支持高达1.3GHz的Quad Cortex A53和高达533MHz的Dual Cortex R5F。SOM支持高达16通道的射频ADC@2.5Gsps和16通道的RF DAC@10Gsps,所有这些都

产品推荐 | 基于 Virtex UltraScale+ XCVU3P的FACE-VPXSSD-3PA 存储板

01 产品概述 FACE(FPGA Algorithm aCceleration Engine)FPGA算法加速开发引擎是基于FPGA可编程器件构建的一系列算法加速开发引擎平台。FACE-VPXSSD-3PA存储平台是FACE系列中的一员。该平台板载2组2GB 64bit DDR4、2路QSFP28光接口、4个NVME SSD M.2接口、NVME SSD扩展槽;板卡数据存入接口支持VPX、QS

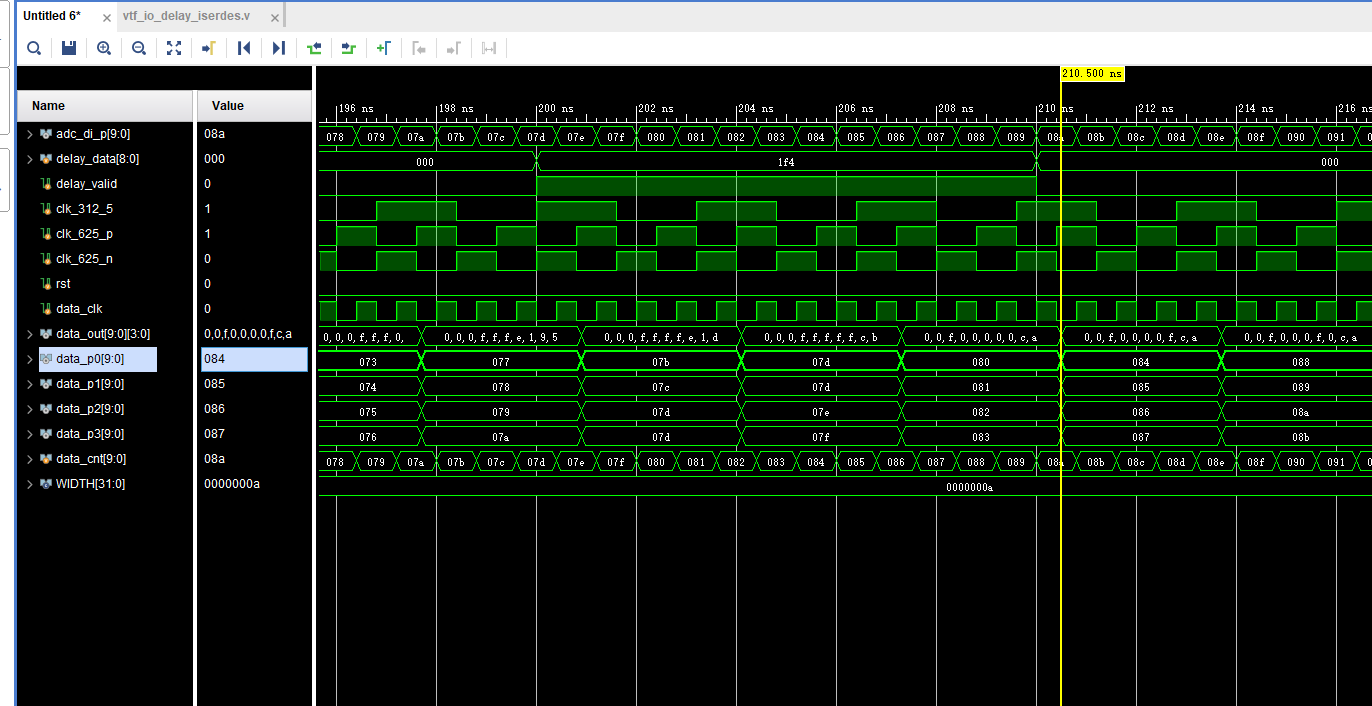

UltraScale 架构 SelectIO 资源之IODELAY与IOSERDES仿真与使用

平台:vivado2018.3 具体内容见ug571-ultrascale-selectio IDELAYE3 在调试超高速信号的时候,需要使用iodelay+iserdes来调试校准输入信号。例如外部某ADC采样率为5GHZ,外部ADC使用2.5GHZ的时钟去采集输入信号。为了实现采集,adc芯片使用了4个1.25ghz采样率的小ADC来采集。但是由于FPGA的工艺,在FPGA内部无法

产品推荐 | 基于VIRTEX UltraScale+系列的 FACE-VU3P-B高性能FPGA开发平台

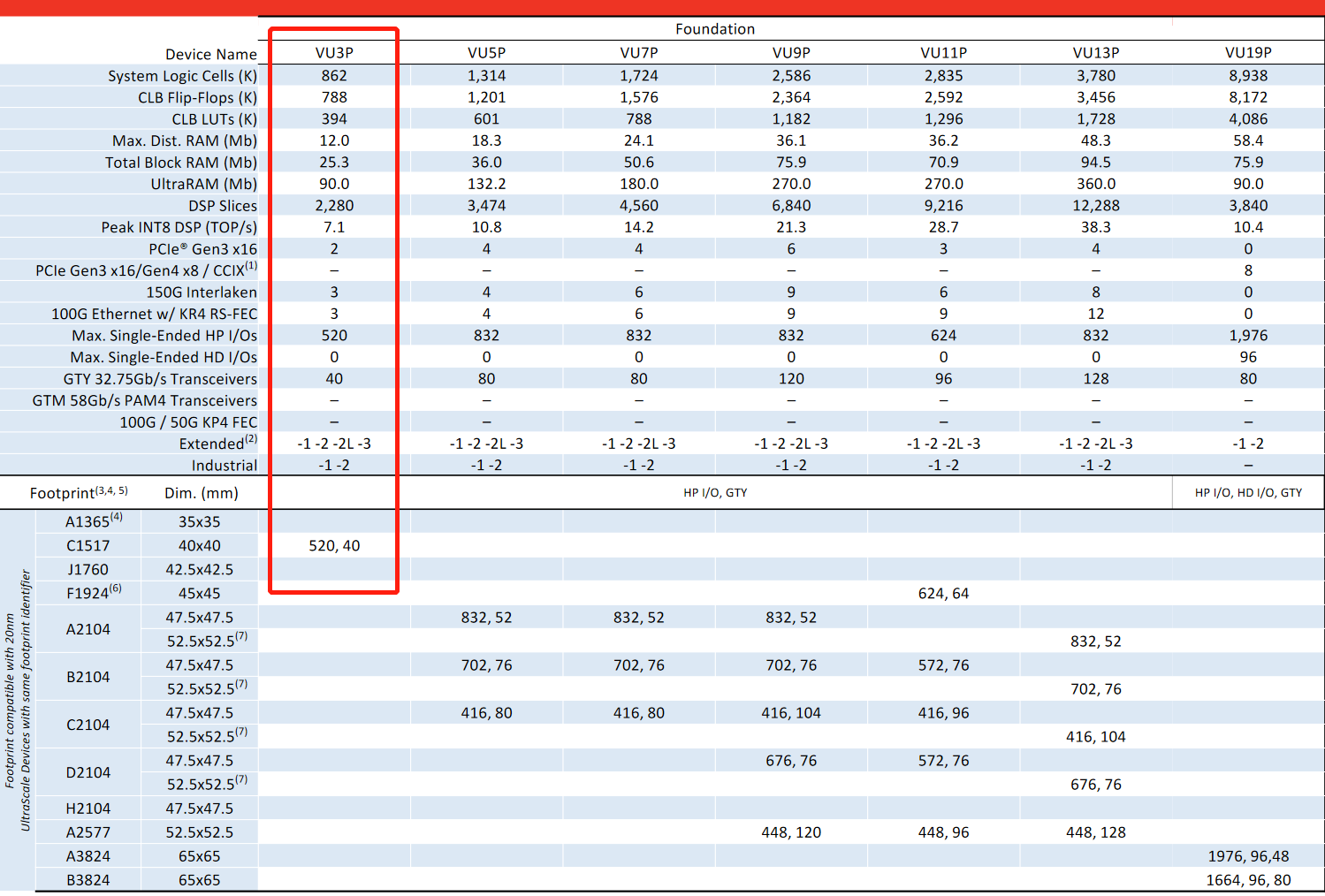

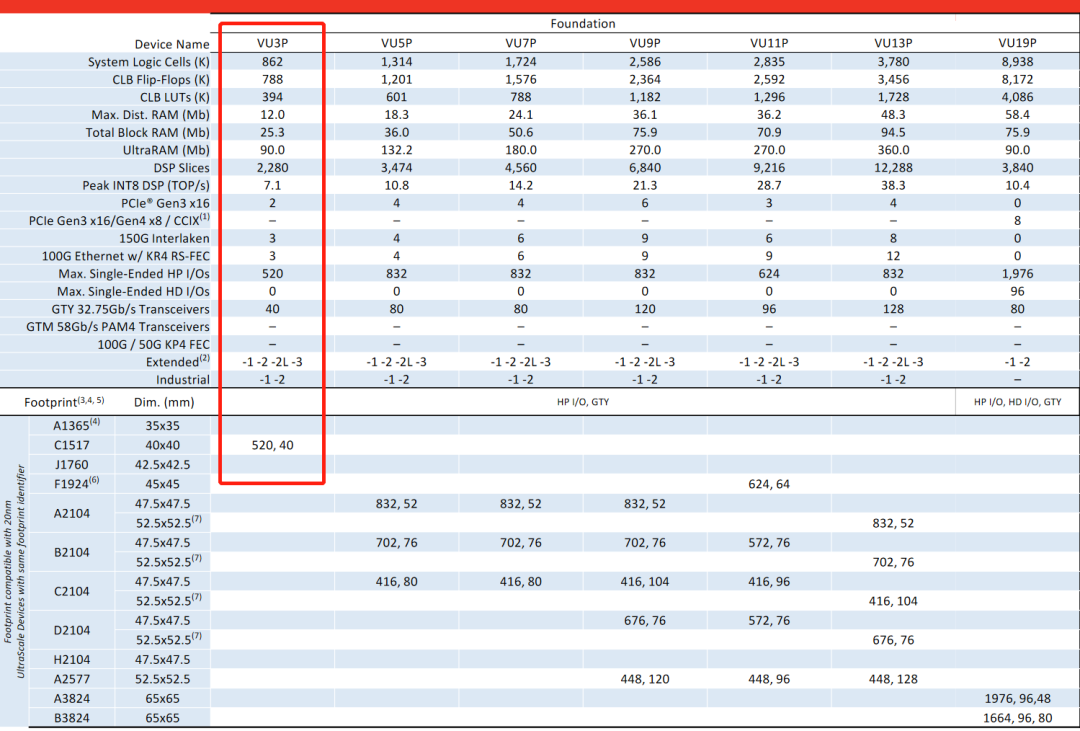

01、产品概述 FACE-VU3P-B高性能FPGA开发平台是FACE系列的新产品。FACE-VU3P-B搭载有16nm工艺的VIRTEX UltraScale+系列主器件XCVU3P。该主器件具有丰富的FPGA可编程逻辑资源,其资源量高于常用的V7-690器件,并且其性能远远高于V7-690器件。 平台板载有丰富计算资源的同时还具备有非常丰富的外设接口:QSFP28、FMC+、U.2 N

UltraScale系列底层结构(1)——引言

目录 一、概述 二、Kintex UltraScale FPGA 三、Kintex UltraScale+™ FPGA 四、Virtex UltraScale FPGA 五、Virtex UltraScale+ FPGA 六、Zynq UltraScale+ MPSoCs 一、概述 Xilinx® UltraScale™ 架构是一种革命性的方法,用于创建可编

产品推荐 | 基于 Zynq UltraScale+ XCZU27DR的 FACE-RFSoC-C高性能自适应射频开发平台

一、产品概述 FACE-RFSOC-C自适应射频开发平台,是FACE系列新一代的产品。 平台搭载有16nm工艺的Zynq® UltraScale+™ RFSoC系列主器件。该器件集成数千兆采样RF数据转换器和ARM® Cortex®-A53处理子系统和UltraScale+可编程逻辑,是一款单芯片自适应射频平台。 二、核心特点 有Zynq UltraScale+ X

产品推荐 - 基于Xilinx Virtex UltraScale+的XUP-P3R FPGA加速卡

1、产品概述 XUP-P3R还集成了一个板卡管理控制器(BMC),用于先进的系统监控,这大大简化了平台的集成和管理。所有这些特点结合起来,使XUP-P3R成为广泛的数据中心应用的理想选择,包括网络处理和安全、加速、存储、广播和SigInt。 主要特点 1、通过4个QSFP28的4x 100GbE 2、高达512GBytesDDR4 3、Up to VU9P: 2.5 million

赛灵思 Xilinx UG583 - UltraScale 架构 PCB 设计: 用户指南 (v1.19)

本文档旨在描述使用 UltraScale™ 和 UltraScale+™ 器件进行 PCB 层面的设计和接口层面的设计的策略。 下载链接: https://china.xilinx.com/support/documentation/user_guides/c_ug583-ultrascale-pcb-design.pdf

基于 Kintex UltraScale 系列 2 路 QSFP+40G 光纤 PCIe 数据传输卡 / 光纤适配器(5GByte/s 带宽KU060光纤 PCIe 数据传输卡)

PCIE732 是一款基于 PCIE 总线架构的高性能数据传输卡,板卡具有 1 个 PCIex8 主机接口、2 个 QSFP+40G 光纤接口,可以实现 2路 QSFP+40G 光纤的数据实时采集、传输。板卡采用 Xilinx 的高性能 Kintex UltraScale 系列 FPGA 作为实时处理器,板载 2 组独立的72 位 DDR4SDRAM 大容量缓存。板卡具有 1 个 RJ4

XCKU060光纤卡学习资料保存:基于kintex UltraScale XCKU060的双路QSFP+光纤PCIe 卡

基于kintex UltraScale XCKU060的双路QSFP+光纤PCIe 卡 一、板卡概述 本板卡系我司自主研发,基于Xilinx UltraScale Kintex系列FPGA XCKU060-FFVA1156-2-I架构,支持PCIE Gen3 x8模式的高速信号处理板卡,搭配两路40G QSFP+接口,两组64-bit DDR4,每组容量8Gbyte,可稳定

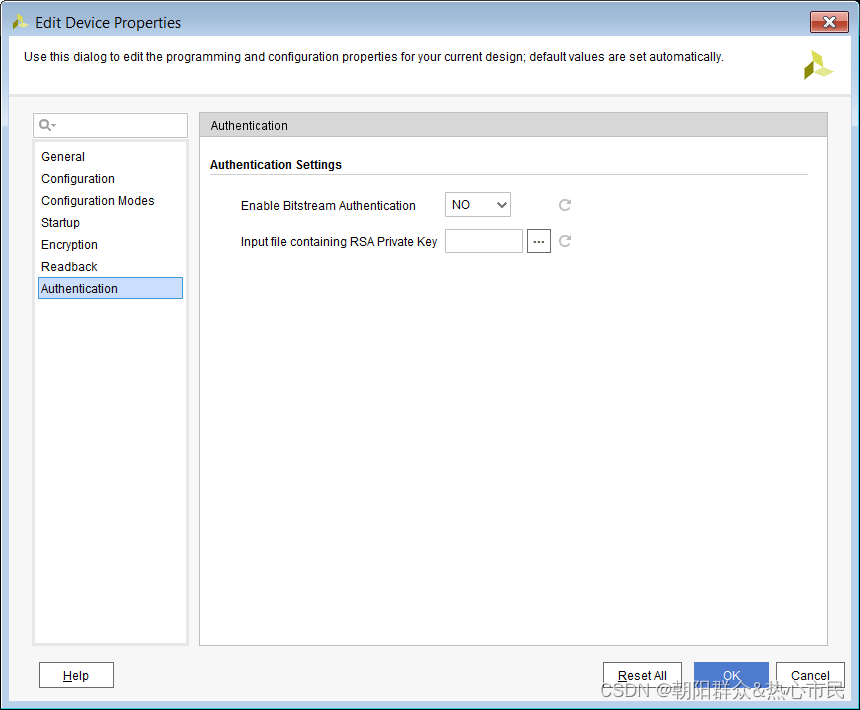

UltraScale 和 UltraScale+ 生成已加密文件和已经过身份验证的文件

注释 :如需了解更多信息,请参阅《使用加密和身份验证确保 UltraScale/UltraScale+ FPGA 比特流的安全》 (XAPP1267)。 要生成加密比特流,请在 Vivado IDE 中打开已实现的设计。在主工具栏中,依次选择“Flow” → “Bitstream Settings”(流程 > 比特流设置),这样即可显示“Settings”(设置)对话框。在此对话框顶部,单击“Co

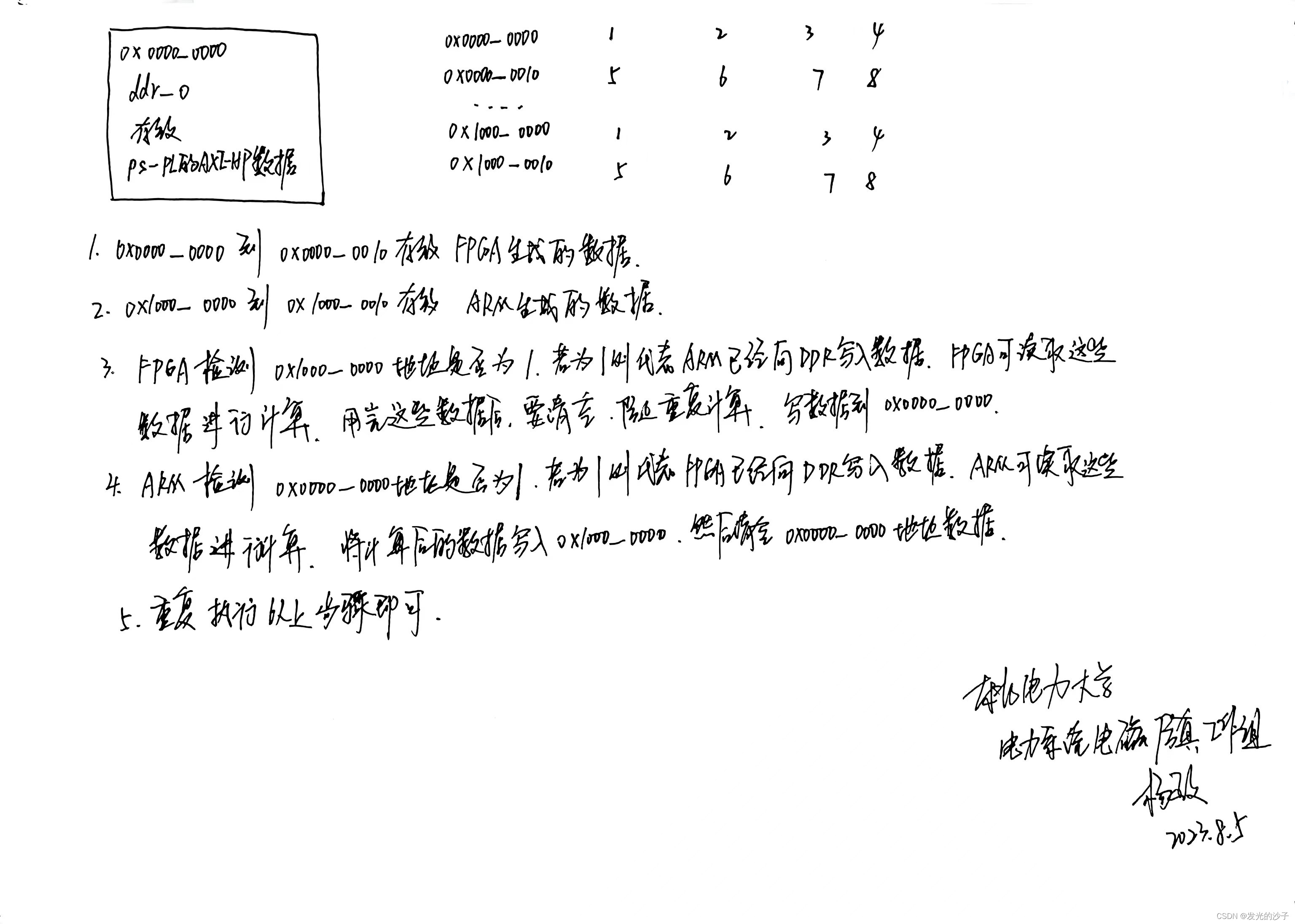

FPGA----UltraScale+系列的PS侧与PL侧通过AXI-HP交互(全网唯一最详)附带AXI4协议校验IP使用方法

1、之前写过一篇关于ZYNQ系列通用的PS侧与PL侧通过AXI-HP通道的文档,下面是链接。 FPGA----ZCU106基于axi-hp通道的pl与ps数据交互(全网唯一最详)_zcu106调试_发光的沙子的博客-CSDN博客大家好,今天给大家带来的内容是,基于AXI4协议的采用AXI-HP通道完成PL侧数据发送至PS侧(PS侧数据发送至PL侧并没有实现,但是保留了PL读取PS测数据的接口)本

Zynq UltraScale+ MPSoC 多媒体应用

消费者渴望更高的视频质量,推动了视频技术的发展。MPSoC 基于 Zynq-7000SoC ,包括一个可编程逻辑 (PL) 的桥接处理系统 (PS),但它在 Zynq UltraScale+ MPSoC进行了额外的扩展,因而非常适合多媒体应用领域。主要的区别包括:针对 UHD-4K 集成了支持 H.264 / H.265 的视频编解码器单元,适用但不仅仅适用于监控、视频会议、嵌入式视觉和一些广

Ultrascale+ GTY transceivers Quad pll

每个Quad 包含两个基于LC的PLL,称为Quad PLL(qpl0和qpl1)。任何一个QPLL都可以由同一个四路中的串行收发器信道共享,但不能由其他四路中的信道共享。当以高于CPLL工作范围的线路速率操作信道时,需要使用QPLL0/1。gtye3/4_common原语封装了gty qpll0/1,并且在使用qpll时必须实例化。 当信道运行速度超过16.375 GB/s时,QPLL0必须使

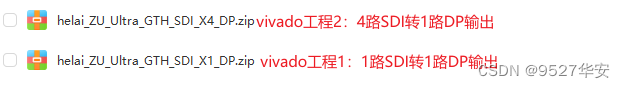

FPGA高端项目:UltraScale GTH + SDI 视频解码,SDI转DP输出,提供2套工程源码和技术支持

目录 1、前言免责声明 2、相关方案推荐我这里已有的 GT 高速接口解决方案我目前已有的SDI编解码方案 3、详细设计方案设计框图3G-SDI摄像头LMH0384均衡EQUltraScale GTH 的SDI模式应用UltraScale GTH 基本结构参考时钟的选择和分配UltraScale GTH 发送和接收处理流程UltraScale GTH 发送接口UltraScale GTH 接收

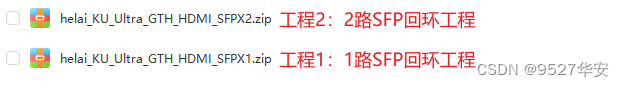

FPGA UltraScale GTH 全网最细讲解,aurora 8b/10b编解码,HDMI视频传输,提供2套工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 GT 高速接口解决方案3、详细设计方案设计框图视频源选择ADV7611解码芯片配置及采集动态彩条视频数据组包UltraScale GTH 全网最细解读UltraScale GTH 基本结构参考时钟的选择和分配UltraScale GTH 发送和接收处理流程UltraScale GTH 发送接口UltraScale GTH 接收接口UltraScale

ultrascale FPGA

1.工艺从mos到FIN,查了半天资料,不如bili的intel介绍视频,其实是把DS做成3D结构,减小DS漏电流; 2.型号的尾数是以百万门为标定的; 3.slice(切片)是CLB的组成单元,slice又包含LUT,slicel和slicem的区别组要是m包含ram单元; 4.DSP模块,数字信号处理大量使用的二进制乘法器和累加器; 5.IO分为HR(宽范围)和HP(高性能)模式;

UltraScale FPGA 可编程逻辑块(CLB)

写在前面 AMD Adaptive Computing Documentation Portal 本文为作者对AMD UltraScale FPGA可编程逻辑块的资源和设计方法的学习笔记,主要参考文献为AMD官方文档:UltraScale Architecture Configurable Logic Block User Guide(UG574)。官方文档链接已放在文章最前面,以供大家参考学

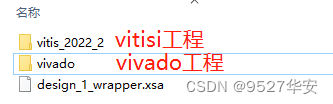

Zynq UltraScale+ XCZU7EV 纯VHDL解码 IMX214 MIPI 视频,2路视频拼接输出,提供vivado工程源码和技术支持

目录 1、前言免责声明 2、我这里已有的 MIPI 编解码方案3、本 MIPI CSI2 模块性能及其优越性4、详细设计方案设计原理框图IMX214 摄像头及其配置D-PHY 模块CSI-2-RX 模块Bayer转RGB模块伽马矫正模块VDMA图像缓存Video Scaler 图像缓存DP 输出 5、vivado工程详解PL端FPGA硬件设计PS端Vitis SDK软件设计 6、工程移植说明

Xilinx UltraScale+ MPSOC(ZU9EG/ZU15EG)高性能 PCIe 数据预处理板

PCIE707 是一款基于 PCIE 总线架构的高性能数据预处理 FMC 载板,板卡具有 1 个 FMC+(HPC)接口,1 路 PCIe x4 主机接口、1 个 RJ45 千兆以太网口、2 个 QSFP+ 40G 光纤接口。板卡采用 Xilinx的高性能 UltraScale+ MPSOC 系列 FPGA 作为实时处理器,实现FMC 接口数据的采集、处理、以及设备间互联传输。PS 端外挂 1 组