本文主要是介绍Xilinx 千兆以太网TEMAC IP核 AXI4-Lite接口信号,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

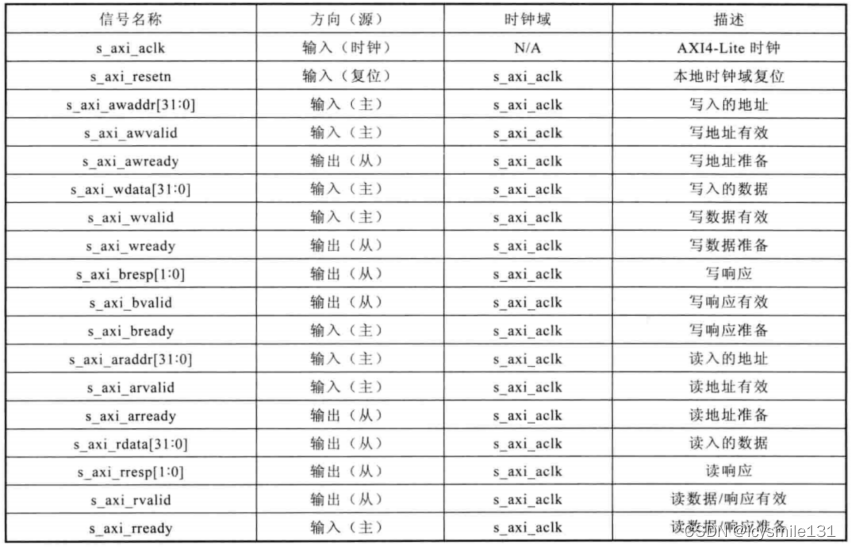

在AX4总线标准中,AXI4-Lite主要由向她址映射型通信。TEMAC的管理法口采用AXI4-Lite标准接口,TEMAC核的AX14-Lite接口信号如表1所示,根据AX14-Lite标准,接口角色分为主接口(Maser Interface)和从接口(Slave Interface)。主接口为通节发起方,这里指的是用户端控制的AX14-Lite接口;从接口为通信接收方,这里指的是MAC核内部的寄存器。

表1 TEMAC核的AX14-Lite接口信号

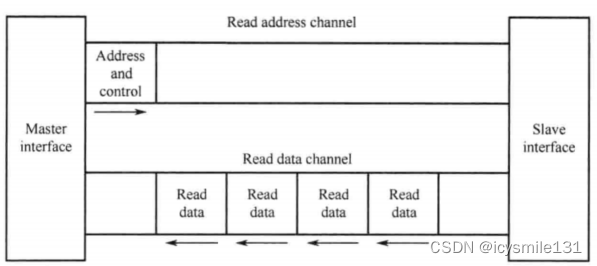

1 基于AXI4-Lite接口的读过程

TEMAC通过AXI4-Lite接口访问不同的MAC寄存器,从而实现TEMAC核的功能配置与管理。掌握AXI4-Lite标准的读/写过程尤为关键,如图2所示为AXI4-Lite接口的读过程,首先由主接口发出读地址请求和控制信号,从接口接收后对其进行响应,把请求读取的数据发送给主接口。

图1 AXI4-Lite接口的读过程

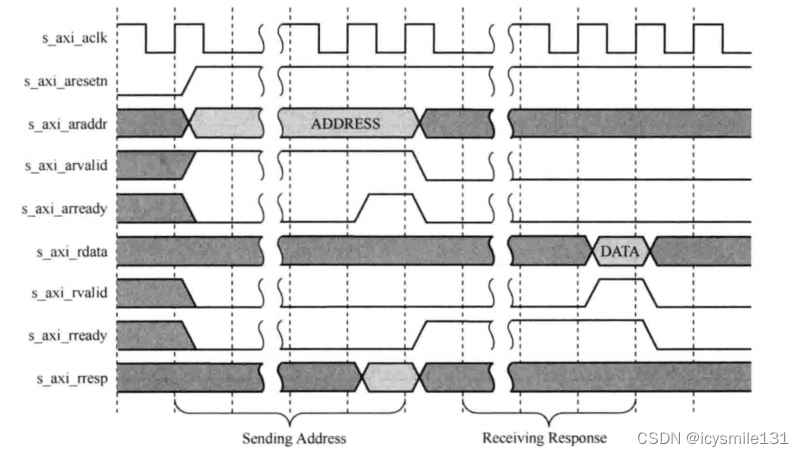

用户基于AXI4-Lite接口读取MAC寄存器的时序如图2所示,整个读过程分为地址发送和响应接收两个阶段。在读寄存器过程中,将主接口请求读入的地址置于s_axi_ araddr 总线上,同时将s_axi_arvalid信号置为有效,表示主接口的有效信息已经在信道上等待从接口完成接收,同时等待从接口发出的接收响应。当从接口输出的s_axi_arready有效时,表示从接口允许接收信息,从接口只在s_axi_arvalid和s_axi_arready同时有效时才能完成信息的接收,即完成主接口的读地址发送。主接口发送完地址请求后,发送接收数据请求信号,将s_axi_rready信号置为高,表示主接口可以接收数据。从接口接收到主接口的接收请求后做出响应,准备发送主接口请求的数据,在s_axi_rdata总线发送被请求的数据,利用s_axi_rvalid信号表示s_axi_rdata总线上的数据有效。主接口根据s_axi_rvalid信号指示接收数据,从而完成读数据过程。

图2 基于AXI4-Lite接口读取MAC寄存器的时序

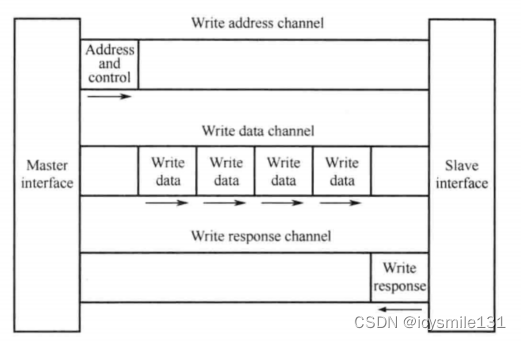

2 基于AXI4-Lite接口的写过程

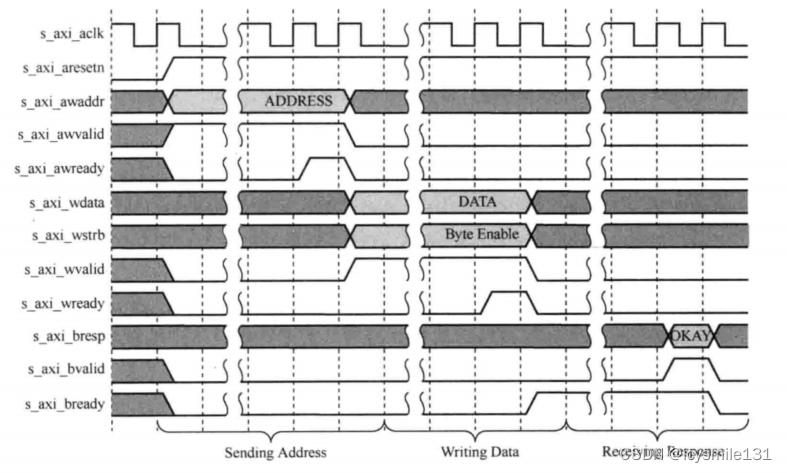

如图3所示为AX14-Lite接口的写过程,首先由主接口发出写地址请求和控制信号从接口接收后允许其写入,主接口将数据写入及接口后,等待以接口发出的写操作完成响应。从而完成一次完整的写过程。

图3 AXI-Lite接口的写过程

基于AXI4-Lite标准接口的写过程分为地址发送,数据写入和响应接收三个阶段。从AXI4-Lite接口写入MAC寄存器的时序如图4所示。

图4 从AXI-Lite接口写入MAC寄存器的时序图

1.地址发送阶段

在写寄存器过程中,将主接口请求写入的地址置于s_axi_awaddr总线上,同时将s_ axi_awvalid信号置为有效,表示主接口的有效信息已经在信道上等待从接口完成接收,同时等待从接口发出的接收响应。当从接口发送的s_axi_awready有效时,表示从接口允许接收地址信息,从接口只在s_axi_awvalid和s_axi_awready同时有效时才能完成地址信息的接收,即完成主接口的写地址发送。

2、数据写入阶段

主接口发送完地址信息后,准备写入数据,将待写入的数据置于。s_axi_wdata总线上(s_axi_wstrb表示写入的选通信号,默认值为“11”。Byte Elable表示写数据总线都可用即s_axi_wstrb为“11”)。并将s_axi_wvalid 置为有效,表示数据已经在信道上等待从接口发出的写入响应信号,进而写入从接口,从接口将s_axi_wready置为高时。表示从接口可以被写人数据。当s_axi_wvalid 与s_axi_wready同时有效后,表示完成了数据写入。

3.响应接收阶段

主接口完成数据写入后,s_axi_bready置为有效并等待从接口的响应信号:从接口的 s_axi_bresp[1:0]用二进制“00”表示写入成功,即OKAY;从接口的s_axi_bvalid 有效时表示写响应有效;当主接口的s_axi_bready有效,且从接口s_axi_bresp为OKAY, s_axi_bvalid有效时,表示主接口确认从接口已完成了数据的写入,从而完成一次完整的基于AXI4-Lite接口的写寄存器过程。

3 MAC地址/帧内容过滤

1.地址/帧内容过滤功能介绍

基于AXI4-Lite标准的管理接口可以配置TEMAC核的地址/帧过滤功能。TEMAC核的地址/帧过滤模块主要包括两个功能:

(1)检查收到的任意数据帧是否匹配事先定义的目的地址(如暂停控制帧地址、广播地址和用户定义单播地址等);

(2)比较数据帧中的前64字节是否符合用户定义的匹配模式。

第1个功能得到的匹配结果通常被TEMAC核中的其他模块(如流控、生成统计矢量等)使用;第2个功能则具有更大的灵活性,因为基于数据帧包头区域或包头区域组合定义的模式可以用来过滤特定的数据帧,而且由数据帧的前64字节定义相关模式可忽略数据帧的其他字段。

用户最多可以在TEMAC核中定义8个地址/帧过滤模块,每个地址/帧过滤模块的功能都可以通过AXI4-Lite标准接口访问寄存器地址值来实现。每个地址/帧过滤模块都包含两个64字节的寄存器。

(1)地址/帧过滤值寄存器(Address/Frame Filter Value Register):地址/帧过滤值寄存器用于与接收到的数据帧的前64字节进行匹配。

(2)地址/帧过滤掩码寄存器(Address/Frame Filter Mask Value Register):若地址/帧过滤掩码寄存器中的某一位为“1”,表示地址/帧过滤值寄存器与接收到的数据帧对应的比特位必须相同,这一比特位才算匹配成功。当地址/帧过滤掩码寄存器中的某一位为“0”,则表示不管接收到的数据帧对应的比特位是否与地址/帧过滤值寄存器中的对应位相同,都认为这一位匹配成功。在地址/帧过滤的匹配过程中,必须保证所有比特位都匹配成功,这样才算整体匹配。

2.地址/帧内容过滤功能的使用

通过设定地址/帧过滤模块的地址/帧过滤值寄存器可以实现简单的目的地址过滤、多播组匹配、源地址匹配和VLAN域匹配等功能,更复杂的过滤功能可以在此基础上通过配合设定地址/帧过滤掩码寄存器完成。通过选用或禁用混杂模式,用户可以开启或禁用地址/帧内容过滤功能(在混杂模式下不过滤数据帧,关闭混杂模式时才进行过滤)。当配置多个地址/帧过滤模块时,需要对地址/帧过滤控制寄存器进行写操作,以此决定对配置寄存器具有优先操作权限的地址/帧过滤模块;当某一特定过滤模块被禁用时,它将不匹配任何数据帧。地址/帧过滤模块寄存器的详细配置请参阅UG800。

默认条件下,所有的地址/帧过滤模块都把地址/帧过滤值寄存器和地址/帧过滤掩码寄存器的低48比特位配置为全1,使广播帧满足事先定义的目的地址过滤条件。建议将地址/帧过滤值寄存器和地址/帧过滤掩码寄存器更新至期望值后再启用地址/帧过滤模块。

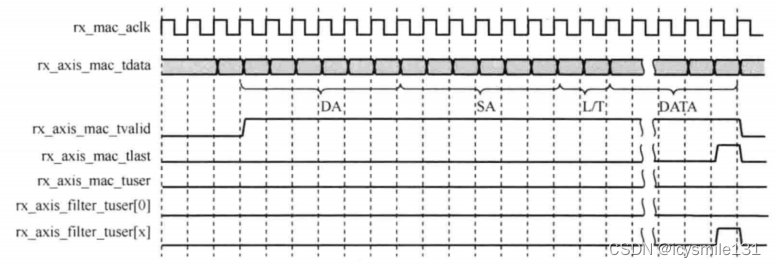

当生成单个或多个过滤模块时,rxaxisfilter tuser总线的位宽会比过滤模块多1比特位(例如,生成4个过滤模块时是5位总线)。当数据与用户定义的过滤模块相匹配时,最高比特位置高。如图5所示为一个与filter0匹配的无差错帧应答过程,此时 rx axis filter tuser[0]信号置为低,rxaxisfilter_tuser[X]信号置为高。

图5 与filter0匹配的无差错帧应答过程

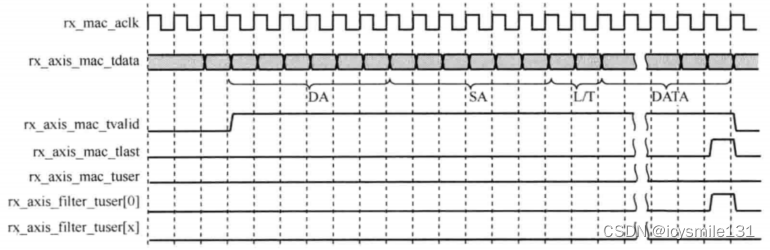

如图6所示为数据帧与事先定义的目的地址匹配,但与用户配置的任意过滤模块都不匹配的应答过程,此时rx_axis_filter_tuser[0]信号为高,rx_axis_filter_tuser[X]信号为低。

图6 与过滤模块不匹配的应答示例

若选用了地址/和过滤模块,但生成的TEMAC核未设置AXD4-Lite管理楼口,则只可以使用地址/帧过滤模块的部分动能,这是国为地址/帧过滤模块没有访问接口时,其内部的配营寄存幕不可访问,更彰不了相关设置,此时基本的目的地址过滤功能仍可被 MAC用于廉别或过述广播地址,特定的暂终多播地址和用户指定的暂件/单播地址。

4 基于AXI4-Lite接口的相关配置和管理

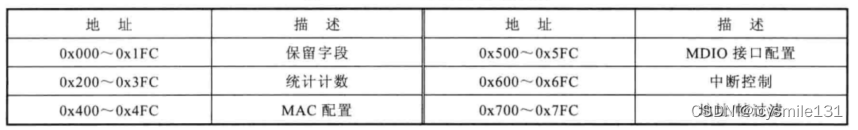

在掌握AXI4-Lite接口读/写寄存器的时序之后,实现TEMAC核的相关设置与管理,需要参考UG800中关于MAC寄存器功能和设定的详细说明,直接对寄存器进行相应的读/写操作即可。配置设定的信息变更可以在任何时间写入配置寄存器,而配置的变化只在帧间间隔生效。MAC寄存器地址映射如表8所示,按功能的不同分为统计计数、 MAC配置、MDIO接口配置、中断控制和地址/帧过滤5个部分。

表2 MAC寄存器地址映射

这篇关于Xilinx 千兆以太网TEMAC IP核 AXI4-Lite接口信号的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!