temac专题

Xilinx 千兆以太网TEMAC IP核 AXI4-Lite接口信号

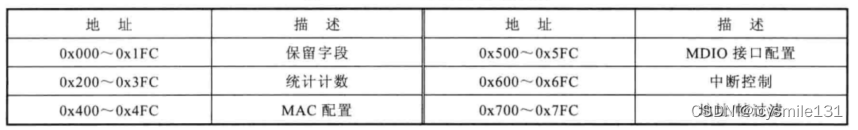

在AX4总线标准中,AXI4-Lite主要由向她址映射型通信。TEMAC的管理法口采用AXI4-Lite标准接口,TEMAC核的AX14-Lite接口信号如表1所示,根据AX14-Lite标准,接口角色分为主接口(Maser Interface)和从接口(Slave Interface)。主接口为通节发起方,这里指的是用户端控制的AX14-Lite接口;从接口为通信接收方,这里指的是MAC核内部的

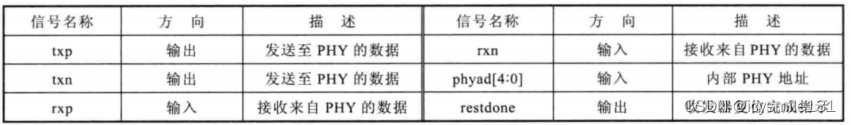

Xilinx 千兆以太网TEMAC IP核 MDIO 配置及物理接口

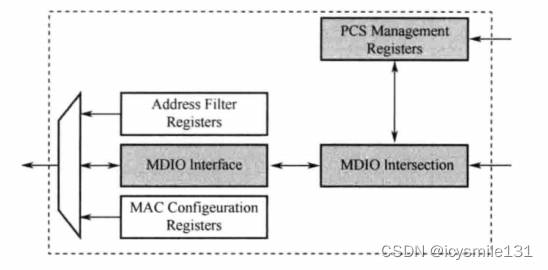

基于AXI4-Lite接口可以访问MDIO(Management Data Input/Output)接口,而MDIO接口连接MAC外部的PHY芯片,用户可通过AXI4-Lite接口实现对PHY芯片的配置。 1 MDIO接口简介 开放系统互连模型OSI的最低两层分别是数据链路层和物理层,数据链路层的主要功能包括数据帧的构建、数据差错检查、发送控制和向网络层提供标准的数据接口等;物理层定义了数据

Xilinx 千兆以太网TEMAC IP核简介

Xilinx 公司提供了千兆以太网MAC控制器的可参数化LogiCORET™IP解决方案,通过这个IPCore可以实现FPGA与外部网络物理层芯片的互连。基于Xilinx FPGA 的以太网设计,大大降低了工程的设计复杂度,缩短了开发周期,加快了产品的面市速度。 Xilinx公司的千兆以太网解决方案按IP类型可以分为三态以太网软核、嵌入式三态以太网硬核、以太网AVB和Ethernet 1000