本文主要是介绍【总线】AXI总线:FPGA设计中的通信骨干,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

AXI4:高性能地址映射通信的基石

AXI4-Lite:轻量级但功能强大的通信接口

AXI4-Stream:高速流数据传输的利器

结语:AXI总线在FPGA设计中的重要性

大家好,欢迎来到今天的总线学习时间!如果你对电子设计、特别是FPGA和SoC设计感兴趣,那你绝对不能错过我们今天的主角——AXI4总线。作为ARM公司AMBA总线家族中的佼佼者,AXI4以其高性能和高度可扩展性,成为了现代电子系统中不可或缺的通信桥梁。

这里会有一系列的课程,和大家分享AMBA总线家族,欢迎大家一起学习,收藏点赞。

系列文章

【总线】AMBA总线架构的发展历程-CSDN博客

【总线】设计fpga系统时,为什么要使用总线?-CSDN博客

【总线】AMBA总线家族的明星成员:AXI协议简介-CSDN博客

【总线】AXI4第一课时:揭秘AXI4总线的五大独立通道-CSDN博客

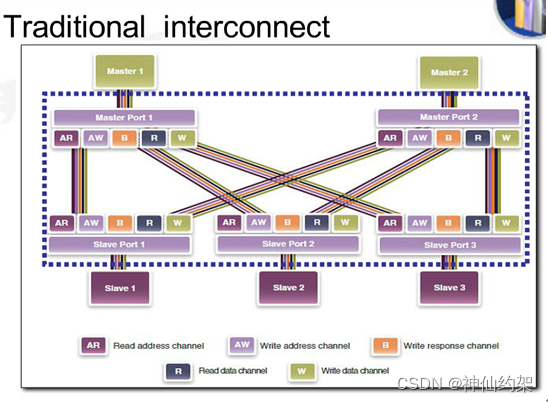

在现代电子设计中,FPGA扮演着至关重要的角色。Xilinx的Vivado设计套件及相关IP核,为工程师提供了强大的工具来实现复杂的系统级集成。其中,AXI(Advanced eXtensible Interface)总线作为FPGA内部通信的支柱,以其高性能、灵活性和扩展性,支撑着各种高速数据处理任务。本文将带您深入了解AXI总线的三种主要变体:AXI4、AXI4-Lite和AXI4-Stream。

AXI4:高性能地址映射通信的基石

AXI4总线是专为高性能内存映射通信设计的接口。它支持复杂的事务处理,如突发传输和流水线操作,极大地提高了数据传输的效率。AXI4的主要特性包括:

- 高带宽支持:AXI4能够支持最大256字的数据突发,这使得它非常适合于需要处理大量数据的应用,如图像处理和高性能计算。

- 低延迟:AXI4的设计优化了数据传输的延迟,确保了快速响应。

- 灵活性:AXI4接口支持多种数据宽度和地址空间配置,以适应不同的设计需求。

AXI4-Lite:轻量级但功能强大的通信接口

AXI4-Lite是AXI4的轻量级版本,专为简单、低吞吐量的内存映射通信设计。它的优势在于:

- 资源占用少:AXI4-Lite占用的逻辑单元数量较少,适合资源受限的应用。

- 易于集成:简化的接口设计使得AXI4-Lite更容易集成到现有的FPGA设计中。

- 高效通信:尽管是轻量级接口,AXI4-Lite依然能够提供高效的单次数据传输。

AXI4-Stream:高速流数据传输的利器

AXI4-Stream是专为高速流数据传输设计的协议。它去除了地址和控制信息,专注于数据的连续流动:

- 无限制的突发传输:AXI4-Stream允许无限制的数据流,非常适合视频流、音频流和其他连续数据流的应用。

- 高吞吐量:专为高吞吐量设计,AXI4-Stream能够实现数据的快速传输。

- 简化的接口:由于去除了地址和控制信息,AXI4-Stream的接口更加简洁,便于实现。

结语:AXI总线在FPGA设计中的重要性

AXI总线家族以其多样化的接口和高性能的特性,满足了FPGA设计中对不同通信需求的支持。从高性能的AXI4到轻量级的AXI4-Lite,再到专为流数据处理设计的AXI4-Stream,AXI协议为FPGA设计提供了强大的通信能力。

随着电子技术的不断进步,AXI总线将继续演进,以适应未来电子系统设计的新挑战。对于工程师和设计者而言,深入理解AXI总线的原理和应用,将有助于他们构建更加高效、可靠的电子系统。

敬请期待我后续的文章,将为您带来关于AXI4-Stream协议的深入介绍和应用案例。让我们一起探索AXI4-Stream在高速数据流领域的无限可能。

这篇关于【总线】AXI总线:FPGA设计中的通信骨干的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!