本文主要是介绍设置AXI主寄存器切片和AXI数据FIFO,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

设置AXI主寄存器切片和AXI数据FIFO

打开MHS文件,并为每个AXI主机设置启用寄存器切片/启用数据FIFO。到

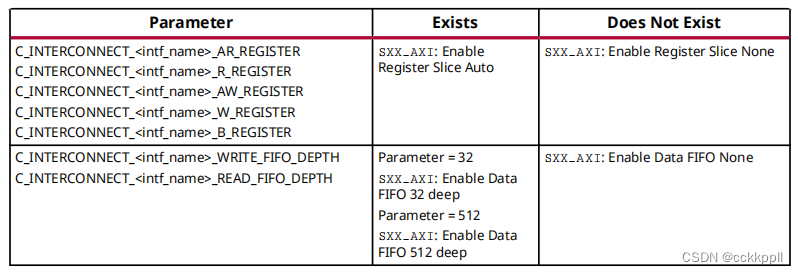

确定正确的设置,使用下表中的信息搜索MHS。

进行搜索时,将<intf_name>替换为相关的BUS_INTERFACE名称。

例如,BUS_INTERFACE M_AXI_MM2S的<intf_name>为

M_AXI_MM2S,并且BUS_INTERFACE M_AXI_GP0的<intf_name>将是M_AXI_GPO。

笔记

•每个IP可能有多个AXI主接口。

•AXI主设备连接到AXI互连从设备连接。在“从属”中进行选择

“接口”选项卡。

设置AXI从寄存器切片和AXI数据FIFO

打开MHS文件,并为每个AXI从机设置启用寄存器切片/启用数据FIFO。到

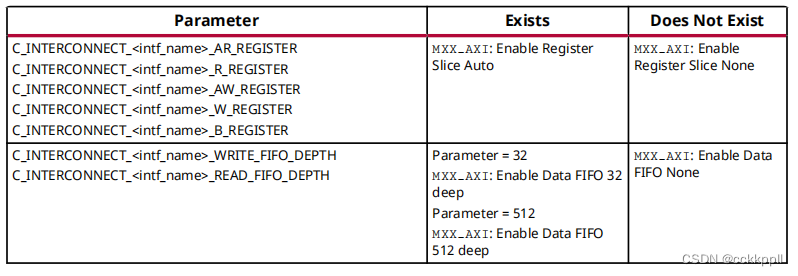

确定正确的设置,使用下表中的信息搜索MHS。

将<intf_name>替换为相关的BUS_INTERFACE名称。例如

BUS_INTERFACE S_AXI的<intf_name>为S_AXI

BUS_INTERFACE S_AXI_HP0将是S_AXI_HPO。

笔记

•每个IP可能有多个AXI从接口。

•AXI从设备连接到AXI互连主设备连接。您在Master中进行选择

“接口”选项卡。

验证设计

单击验证设计按钮以帮助解决可能包括信号的设计问题,

连接或其他问题。

验证的XPS和IP Integrator设计之间的参数

基于Zynq平台处理器的AXI主从式设计

1.确保XPS设计已生成网表。这将为创建顶级IP包装文件

<xps_project>/hdl目录中的每个IP。

例如,<xps_project>/hdl/system_leds_4bits_wrapper.vhd包含

EDK设计中AXI_GPIO的包装器。包装的重要部分是

映射到参数,如下所示。

以下命令:

以下示例显示了用于比较的行。

C_ALL_OUTPUTS_2,这是最新的用于IP积分器的AXI GPIO IP上的新参数。

3.设置这些参数时,请查找参数中的添加或差异

适当IP产品规范的值。

如果需要更改参数:

双击方框图中的IP实例,并对其进行适当的参数更改

更新XCI文件。

如果在GUI中找不到参数:

a.在方框图中选择IP。

b.选择“块特性”下的“特性”选项卡。

c.展开Config(配置)并输入参数值。

d.恢复report_property命令,必要时进行修改。

e.单击“验证设计”以确保设计不存在任何问题。

完成设计

1.在“源”选项卡中,右键单击design_1,然后选择“生成输出产品”。

2.单击“生成”。

3.在Sources选项卡中,生成后,右键单击design_1,然后选择Create HDL Wrapper。

4.为Vivado选择“确定”以管理顶级包装。

5.创建一个XDC文件,锁定(1)设计中与板无关的引脚或(2)

MIG的附加约束。例如,XDC文件可能会锁定的位置

MIG的复位引脚和DCI_ CASCADE设置。

这篇关于设置AXI主寄存器切片和AXI数据FIFO的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!