fifo专题

LabVIEW FIFO详解

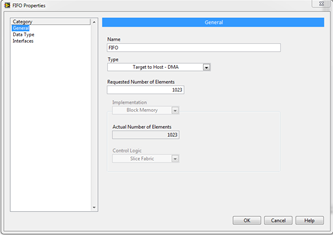

在LabVIEW的FPGA开发中,FIFO(先入先出队列)是常用的数据传输机制。通过配置FIFO的属性,工程师可以在FPGA和主机之间,或不同FPGA VIs之间进行高效的数据传输。根据具体需求,FIFO有多种类型与实现方式,包括目标范围内FIFO(Target-Scoped)、DMA FIFO以及点对点流(Peer-to-Peer)。 FIFO类型 **目标范围FIFO(Target-Sc

LabVIEW开发FPGA方法与FIFO数据丢失处理

开发基于NI 7975R FPGA的系统涉及一系列流程,包括驱动安装、LabVIEW项目设置、开发调试、编译和与Windows系统的通信。重点在于FIFO的正确配置,避免数据丢失是关键环节之一,尤其是在使用高速数据流传输时。以下将详细介绍这些过程,并重点讨论FIFO数据丢失的原因与解决方案。 FPGA开发流程 驱动安装与工具准备:开发FPGA需要安装LabVIEW FPGA模块以及N

页面置换算 - FIFO、LFU、LRU

缓存算法(页面置换算法)-FIFO、LFU、LRU 在前一篇文章中通过leetcode的一道题目了解了LRU算法的具体设计思路,下面继续来探讨一下另外两种常见的Cache算法:FIFO、LFU 1.FIFO算法 FIFO(First in First out),先进先出。其实在操作系统的设计理念中很多地方都利用到了先进先出的思想,比如作业调度(先来先服务),为什么这个原则在很多地方都会

【ZYNQ MPSoC开发】lwIP TCP发送用于数据缓存的软件FIFO设计

设计背景 任务是在ZYNQ的PS上使用裸机运行lwIP协议栈使用TCP把PL端通过AXI DMA传来的将近100K采样率的ADC数据发送出去,但由于数据带宽很大,有853.3mbps,所以在每一次AXI DMA简单传输结束后,lwIP未必有足够的发送buffer立即把数据发送走,如果是发送完再进行下一次简单传输的思路,则会很大地限制了整个系统的带宽,一个简单的思路是每次传输完成后判

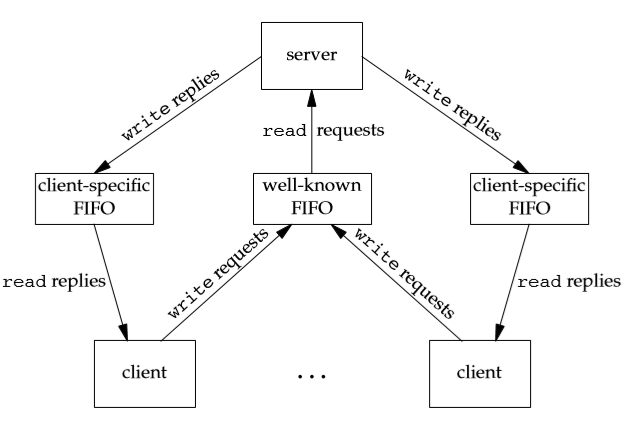

APUE-FIFO理解

1.FIFO是一种文件类型。struct stat结构体中st_mode字段指明该文件是否是FIFO类型。可使用宏S_ISFIFO进行测试。2.FIFO操作函数:mkfifo, open, read, write, close, unlink等对文件进行操作的函数。 注:打开FIFO时同其他文件一样可以指定打开标识(如非阻塞,默认是阻塞打开),以及文件访问权限。3.阻塞打开FIFO:只读

LRU、LFU、FIFO算法总结

一、概述 (1)FIFO:First In First Out,先进先出 (2)LRU:Least Recently Used,最近最少使用 (3)LFU:Least Frequently Used,最不经常使用 FIFO表示先进先出,类似于对列,在数据的结构上使用对列来实现。 结构图: 1. 新访问的数据插入FIFO队列尾部,数据在FIFO

OutOfRangeError PaddingFIFOQueue '_1_get_batch/batch/padding_fifo_queue 解决方案

最近使用Faster-RCNN训练模型时,遇到了如标题所示的问题,最终得到解决,现在记录解决方式如下: 一般这种问题都不是代码的问题,请先检查训练数据: 1. 训练数据中图像文件和标注文件数量是否相同 2. 训练数据中是否有损坏的图片(数量多的话可以用PIL写个简单的加载方法去判断) 3. 标注文件中标注的长宽与实际长宽是否相同(我的问题在这里得到了解决,下面列出检测的代码): from

FPGA开发——使用verilog实现异步FIFO

一、FIFO 介绍 1、FIFO的分类 FIFO ( First In First Out)先进先出存储器。根据接入的时钟信号,可以分为同步 FIFO 和异步 FIFO 。 FIFO 底层是基于双口 RAM ,同步 FIFO 的读写时钟一致,异步 FIFO 读时钟和写时钟不同。 作用: 同步 FIFO:主要用于数据缓冲,类似于乒乓缓存思

[ip核][vivado]FIFO 学习

<xlinx FPGA应用进阶 通用IP核详解和设计开发>读书摘录: 1. 2.3.仿真模型 特点总结:1)复位后会有busy状态,需要等待wr_rst_busy信号低电平后才能正常写入 2)prog_full信号的高电平长度可调 3)仿真中的读状态很奇怪,并没有正常读取,都是XXX的状态。 所用的te

什么是FIFO管理单元?(First-In-First-Out)

FIFO(First-In-First-Out,先进先出)管理单元是一种广泛用于数据处理和存储系统中的机制,其核心理念是确保最早进入系统的数据最早被处理或移出。这种管理方法类似于排队的方式,最早进入队列的项目会最先得到服务。 FIFO管理单元通常用于缓冲区(Buffer)设计、任务调度、内存管理等多个领域。在硬件和软件系统中,FIFO机制有助于保证数据的有序处理,

陀螺仪LSM6DSV16X与AI集成(7)----FIFO数据读取与配置

陀螺仪LSM6DSV16X与AI集成.6--检测自由落体 概述视频教学样品申请源码下载主要内容生成STM32CUBEMX串口配置IIC配置CS和SA0设置串口重定向参考程序初始换管脚获取ID复位操作BDU设置设置量程设置FIFO水印设置速率使用流模式设置FIFO时间戳批处理速率使能时间戳FIFO状态寄存器演示 概述 LSM6DSV16X是一款高性能、低功耗的6轴IMU传感器,集成

第十五章(二) FIFO、消息队列及信号量

FIFO FIFO也称为命名管道,没有了未命名管道只能在两个相关进进程之间才能运行的局限性; 通过FIFO, 两个不相关的进程也能交换数据。 FIFO是一种文件类型,通过stat结构的 st_mode 成员的编码可以知道文件是否是FIFO类型。 可以用 S_ISFIFO宏对此进行测试。 创建FIFO类似于 创建文件,路径名是事实存在的。 函数 in

【C语言】进程间通信之命名管道fifo

进程间通信之命名管道fifo 命名管道fifo()fifo_write.cfifo_read.c 最后 命名管道fifo() FIFO可以用于没有血缘关系的进程间通信。FIFO是Linux基本文件类型的一种,文件类型为p。 简单来说,FIFO可以理解为一个特殊的文件,创建它之后,可以使用 ls或ll来进行查看文件基本信息。 FIFO就是标识内核的一条管道,进程可以通过read

java动态缓存成长小纪(二)——缓存算法的实现:LRU、LFU、FIFO

缓存算法也叫作淘汰算法,主要是为了当JVM空间不足时,用来清理掉缓存的。那么要清理的话,我们先清理掉哪些缓存呢?按照正常人的思维,当然是接下来一段时间内不大可能用到的缓存啦!根据这个思路,我们需要做出一定的判断,判断的方法通常有3个,即LFU、LRU、FIFO。 还有个问题,什么时候进行清理?when? 我觉得一般可以设置一个阈值,标记最小剩余空间,是在插入时候检查JVM剩余空间。或者还

STM32高级篇—按键FIFO

想成问一名非常优秀的嵌入式软件工程师,是需要掌握很多知识的。完成STM32的基础内容的学习后,我们也进入到学习STM32高级的内容上。本人也是一名嵌入式的初级入坑人,写的内容可能会有错误,或者不正确的地方也请大家多多指教,我们一起努力。 文章目录 一、FIFO(先进先出)1.1 按键FIFO的意义1.2 FIFO的实现 二、按键FIFO的实现2.1 按键FIFO的初始化2.2 按键F

嵌入式应用之FIFO模块原理与实现

FIFO介绍与原理 FIFO是First-In First-Out的缩写,它是一个具有先入先出特点的缓冲区。FIFO在嵌入式应用的非常广泛,可以说有数据收发的地方,基本就有FIFO的存在。或者为了降低CPU负担,提高数据处理效率,可以在积累到一定的数据量之后,再一次性处理。在嵌入式系统中,FIFO是基于一维数组和结构体实现的循环队列(Queue),或者叫环形队列。可以分为同步FI

C++: 有名管道(FIFO)通信bug

这里给出一个写的比较清晰的管道通信的文章: https://www.cnblogs.com/boyxiao/archive/2011/01/02/1924188.html 项目场景: 场景: Windows下,进程间使用FIFO通信,用于传输视频帧。 问题描述: 1. 客户端第一次在read(即createFile)那里会阻塞,客户端第二次运行的时候才会读取出信息; 2. 在传输过

【FPGA】賽灵思FIFO内核的配置

想的是尽量每天更新一篇,前期先把常用内核配置简单总结一下。内核之后想再总结一下时许约束这部分。可能计划赶不上变化,今天先把FIFO说一下吧。关于FIFO常用的内核有几个细节, 1.关于DRAM和BRAM的区别在上篇转的文章里说过了, 2.还有一个就是关于异步FIFO需满和需空的问题: 参考http://xilinx.eetop.cn/viewthread-613258里提到的问题,感

头歌页面置换算法第1关:计算FIFO算法缺页率

2 任务:FIFO算法 2.1 任务描述 设计算法模拟程序:从键盘输入访问串。模拟页表、页框的装入与淘汰,计算FIFO算法在不同内存页框数时的缺页数和缺页率。 2.2任务要求 输入串长度作为总页框数目,补充程序完成FIFO算法。 #include <stdio.h>#include <stdlib.h>#ifndef TRUE#define TRUE 1#define FALSE

阻塞队列BlockingQueue(FIFO)

一:简介 阻塞队列:从定义上来说是队列的一种,那么肯定是一个先进先出(FIFO)的数据结构。与普通队列不同的是,它支持两个附加操作,即阻塞添加和阻塞删除方法。 阻塞添加:当阻塞队列是满时,往队列里添加元素的操作将被阻塞。 阻塞移除:当阻塞队列是空时,从队列中获取元素/删除元素的操作将被阻塞。 二:java中对阻塞队列的定义 BlockingQueue接口与Queue接口【Queue 和 Bl

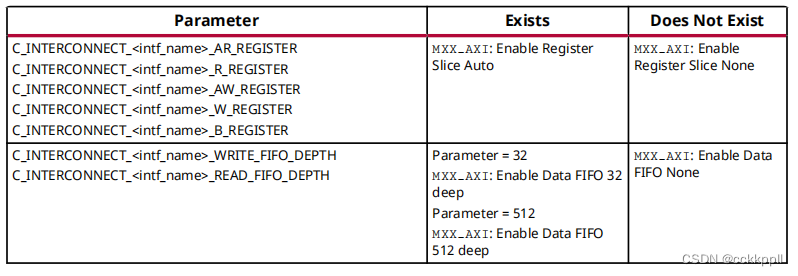

设置AXI主寄存器切片和AXI数据FIFO

设置AXI主寄存器切片和AXI数据FIFO 打开MHS文件,并为每个AXI主机设置启用寄存器切片/启用数据FIFO。到 确定正确的设置,使用下表中的信息搜索MHS。 进行搜索时,将<intf_name>替换为相关的BUS_INTERFACE名称。 例如,BUS_INTERFACE M_AXI_MM2S的<intf_name>为 M_AXI_MM2S,并且BUS_INTERFACE M_AXI_GP

链表类型的无界阻塞线程安全队列-ConcurrentLinkedQueue(FIFO)

ConcurrentLinkedQueue是非阻塞线程安全(volatile不能完全保证线程安全)的队列,适用于“高并发”的场景。是一个基于链表节点的无界线程安全队列,按照 FIFO(先进先出,尾先进头先出)原则对元素进行排序。队列元素中不可以放置null元素(内部实现的特殊节点除外)。 volatile作用: volatile的作用是保证共享变量的可见性,不能保证原子性,也不能保证线程安

STM32F1之OV7725摄像头·像素数据输出时序、FIFO 读写时序以及摄像头的驱动原理详解

STM32F1之OV7725摄像头-CSDN博客 STM32F1之I2C通信-CSDN博客 目录 1. 像素数据输出时序 2. FIFO 读写时序 2.1 写时序 2.2 读时序 3. 摄像头的驱动原理 1. 像素数据输出时序 主控器控制 OV7725 时采用 SCCB 协议读写其寄存器,而它输出图像时则使用 VGA 或

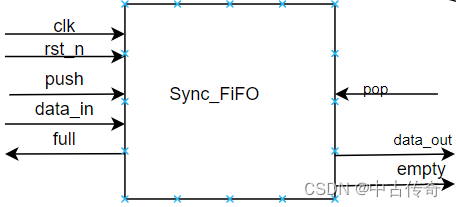

【Sync FIFO介绍及基于Verilog的实现】

Sync FIFO介绍及实现 1 Intro2 Achieve2.1 DFD2.2 Intf2.3 Module 本篇博客介绍无论是编码过程中经常用到的逻辑–FIFO;该FIFO是基于单时钟下的同步FIFO; FiFO分类:同步FiFO VS 异步FiFO; 1 Intro FIFO可以自己实现,但是因为FiFO太常用,为了减少造轮子和出错率,基本上每个公司都有自己的C

关于FIFO Generator IP和XPM_FIFO在涉及位宽转换上的区别

在Xilinx FPGA中,要实现FIFO的功能时,大部分时候会使用两种方法: FIFO Generator IP核XPM_FIFO原语 FIFO Generator IP核的优点是有图形化界面,配置参数非常直观;缺点是参数一旦固定,想要更改的化就只能重新generate IP核。 XPM_FIFO原语的优点就是参数配置方便。 对于两者,还有一个非常重要的区别。!!!大小端不一样!!!

HLS进阶技巧——反压fifo

在Vitis HLS设计中,由于只能获取到fifo的empty、full信号,而不像RTL设计中还能拿到write/read count,所以在dataflow中,只能通过empty、full信号来进行数据驱动。反压fifo是通过fifo的full信号来控制程序的运行。下面介绍两种笔者涉及到的反压技巧,以便大家在自己的设计中举一反三。 技巧1 下图所示为dataflow中一个最基本的结构,在反

![[ip核][vivado]FIFO 学习](https://img-blog.csdn.net/2018062400334231?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3UwMTIxMzUwNzA=/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)