circuits专题

Circuits--Sequential--More circuits

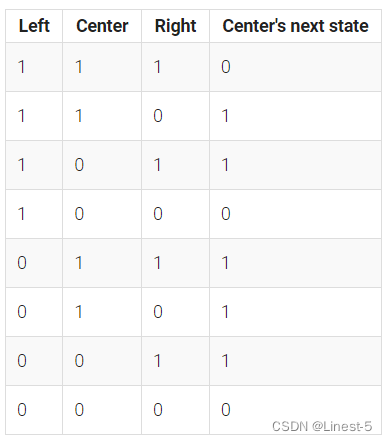

1. Rule 90 module top_module(input clk,input load,input [511:0] data,output [511:0] q ); always@(posedge clk)beginif(load)q<=data;elsebeginq<={1'b0,q[511:1]}^{q[510:0],1'b0}; //左邻居矩阵^右邻居矩阵endendendmo

「HDLBits题解」Building Larger Circuits

本专栏的目的是分享可以通过HDLBits仿真的Verilog代码 以提供参考 各位可同时参考我的代码和官方题解代码 或许会有所收益 题目链接:Exams/review2015 count1k - HDLBits module top_module (input clk,input reset,output [9:0] q);always @(posedge clk) beginif

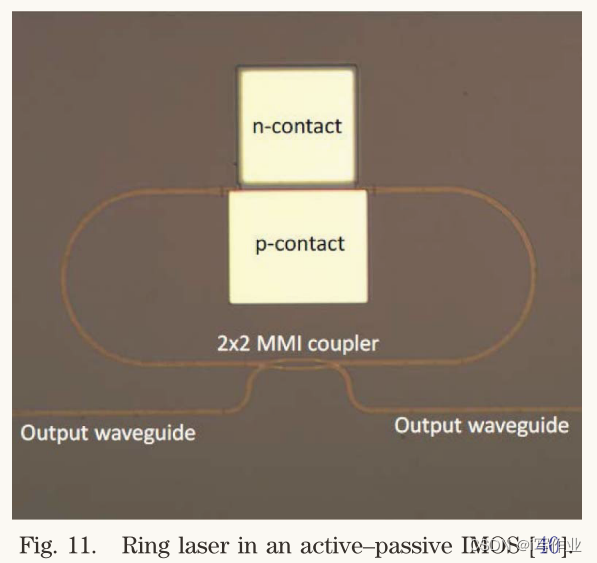

论文笔记_InP_photonic_circuits_using_generic_integration

InP_photonic_circuits_using_generic_integration 时间:2015年5月 文章目录 InP_photonic_circuits_using_generic_integrationⅠ IntroductionⅡ 通用集成平台A. 对特定信号进行处理B. Multiwavelength TransmitterC. 超快激光(皮秒激光、飞秒激光)D.

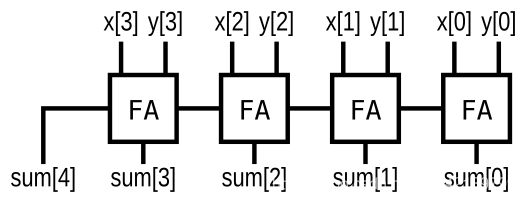

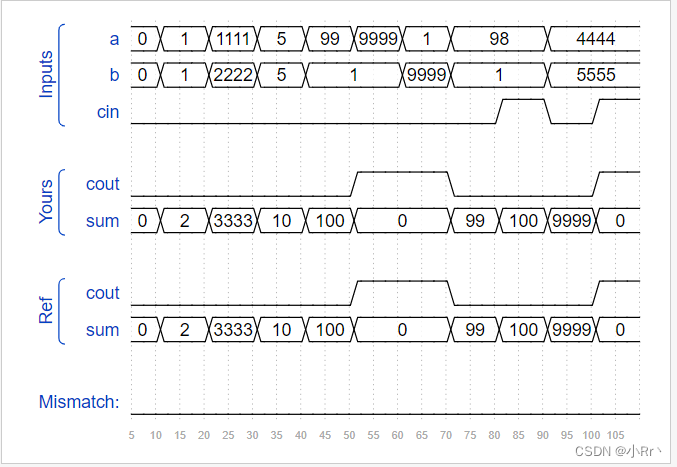

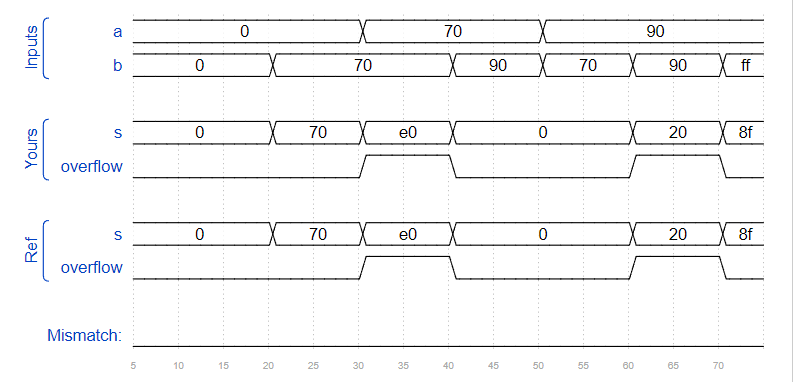

Circuits-Combinational Logic-Arithmetic Circuits

目录 1、Half adder2、Full adder3、3-bit binary adder4、Adder5、Signed addition overflow6、100-bit binary adder7、4-digit BCD adder参考资料:https://hdlbits.01xz.net/ 1、Half adder Create a half adder. A ha

Verilog学习笔记HDLBits——Arithmetic Circuits

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、Arithmetic Circuits1. Half adder2. Full adder3. 3-bit binary adder4. Adder5. Signed addition overflow6. 100-bit binary adder7. 4-digit BCD adder 总结

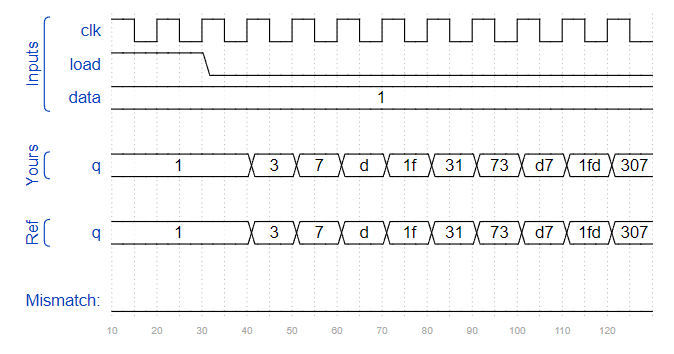

【HDLBits 刷题 8】Circuits(4)Sequential Logic---Shifts Registers More Circuits

目录 写在前面 Shifts Registers Shift4 Rotate100 Shift18 Lfsr5 Mt2015 lfsr Lfsr32 Shift registier Shift registier2 3 input LUT More Circuits Rule90 Rule110 Conwaylife 写在前面 本篇博客对 Circu

HDLBits——Arithmetic Circuits

HDLBits——Arithmetic Circuits Problem 65 : Half adder (Hadd) Requirement: 本题中需要实现一个 2 进制 1bit 加法器,加法器将输入的两个 1bit 数相加,产生两数相加之和以及进位。 Solution: module top_module( input a, b,output cout, sum );as

HDLBits——More Circuits

HDLBits——More Circuits Problem 115 Rule90 Requirement: Rule90 是一道根据一些有趣的规则来生成一维序列的题目。 规则很简单:一维序列中元素有 1、0 两种状态,分别对应开、关状态。在每个时钟边沿到来时刻,元素的下一个状态为元素相邻两个元素的异或。下表更详细地给出了跳变的规则(可以视为状态转移表),元素下一个状态可以视作输出,输入为

HDLBits 系列(10)——Building Larger Circuits

目录 3.3 Building Larger Circuits 1 . Counter with period 1000 2. 4-bit shift register and down counter 3. FSM: Sequence 1101 recognizer 4. FSM: Enable shift register 5. FSM: The complete FSM 6

HDLBits练习 Circuits;Combinational Logic;Arithmetic Circuits

Circuits;Arithmetic Circuits 1.Half adder2.Full adder3.3-bit binary adder4.Adder5.Signed addition overflow6.100-bit binary adder7.4-digit BCD adder7. ==问题== 要点: 1. 异或的理解: 异或(相异的时候进行或运算)真值

smithchart matlab,Electronic Circuits with MATLAB, PSpice, and Smith Chart

Electronic Circuits with MATLAB, PSpice, and Smith Chart By 作者:Won Y. Yang Jaekwon Kim Kyung W. Park Donghyun Baek Sungjoon Lim Jingon Joung Suhyun Park Han L. Lee Woo June Choi Taeho Im Release Fin

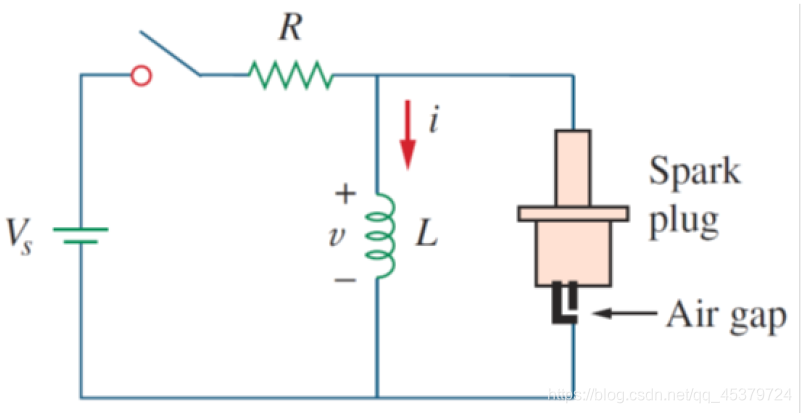

电路Circuit- Chapter 7 First-Order Circuits(一阶电路)

First-Order Circuits 7.1 IntroductionRC circuits(动态电路及其阶数)RL circuits总结例题 7.2 The Source-Free(无源) RC Circuit(RC电路的零输入响应)7.3 The Source-Free RL Circuit(RL电路的无源响应)7.4 Singularity Functionsunit step f

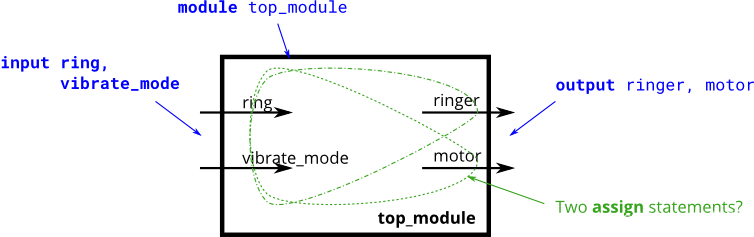

HDLBits-Circuits学习小结(一)初探门电路(basic gates)

目录 1 Basic Gates1.1 GND NOR and Another gate1.1.1 GND1.1.2 NOR1.1.3 Another gate 1.2 Two gates1.3 More logic gates 2 Simple Circuit2.1Truth tables2.2 Two-bit equality2.3 Simple circuit2.3.1 Simple

2023年第二锅,TCSVT(IEEE Transactions on Circuits and Systems for Video Technology),中科院一区

TCSVT投稿记录 1. 2022年12月28日 提交稿件。 2. 2023年2月3日 拒稿 3. 2023年2月24日 修改拒稿重投 4. 2023年4月19日 小修 5.2023年4月24日 小修改提交 6. 2023年5月17日 接收 可以中TCSVT差不多是我现在领域的顶峰了,主要我做的现在是夕阳产业,要发好的期刊真难。 后续需要提交最终文件,这需要提交那些文件有投过的可以指导

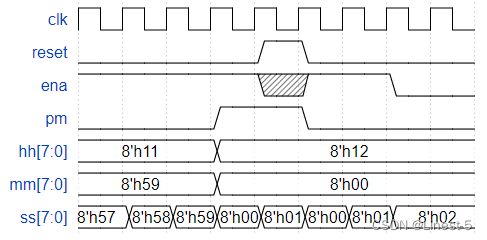

【HDLBits 刷题 7】Circuits(3)Sequential Logic---Counters

目录 写在前面 Counters Count15 Count10 Countslow Counter1-12 Counter1000 Countbcd Count clock 总结 写在前面 本篇博客对 Circuits 部分的组合逻辑前两节做答案和部分解析,一些比较简单的题目就直接给出答案,有些难度再稍作讲解,每道题的答案不一定唯一,可以有多种解决方案,欢迎共同讨论。