进位专题

史上最全BigDecimal的5种进位方式:ROUND_UP,ROUND_DOWN,ROUND_CEILING,ROUND_FLOOR,ROUND_HALF_UP,ROUND_HALF_DOWN的比较

先上JAVA官方文档 /*** Rounding mode to round away from zero. Always increments the* digit prior to a nonzero discarded fraction. Note that this rounding* mode never decreases the magnitude of the cal

组队赛4解题报告(组合数学+禁位排列+容斥原理+精度进位+贪心背包+矩阵快速幂)

B题:ZOJ 3687 链接:http://acm.zju.edu.cn/onlinejudge/showProblem.do?problemId=4970 题意:在d天看不了c章,问复习的方案有多少种? 思路:这题比赛的时候看出是组合数组和容斥原理了,不过不会做,所以一直托到现在了才做。而且自己又看别人的解题报告理解了一下午才理解明白……笨了…… 我在百度文库上已经知道错排和禁位排列是什

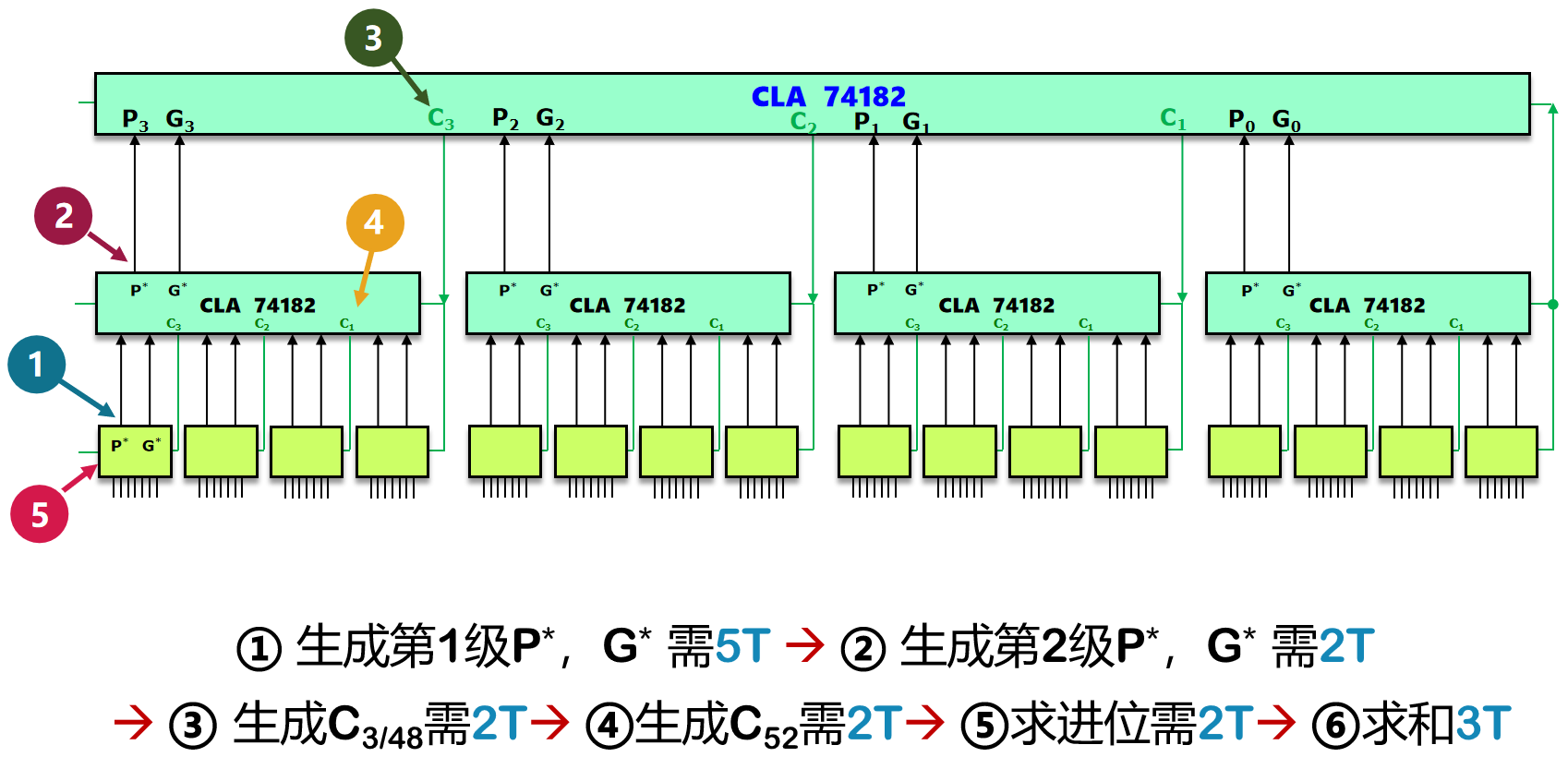

计算机组成原理·定点加减法与先行进位

重点理解一下加减法的电路实现,先行进位的原理,以及时间延迟分析。挑重点记录一下我的理解。 定点加减法的运算 运算原理 在计算机内,定点数都是以补码的形式进行运算的。两个数 x , y x,y x,y 的加减法满足下面的规则: { [ x + y ] 补 = [ x ] 补 + [ y ] 补 [ x − y ] 补 = [ x ] 补 − [ y ] 补 = [ x ] 补 +

为什么ROUND(9.95,1) 返回 9.9 而不是 10.0? 难道9.95 不该向上进位么

SQLite 内部使用二进制运算,9.95用 64-bit IEEE 浮点数 ( SQLite 内部使用的) 表示为 9.949999999999999289457264239899814128875732421875。所以当你输入 "9.95"时, SQLite 就理解为上述的数字,进而四舍五入得到9.9。这个问题在处理浮点二进制数总会产生。通常的规则是十进制的有限浮点数通常无法表示为二进制有限

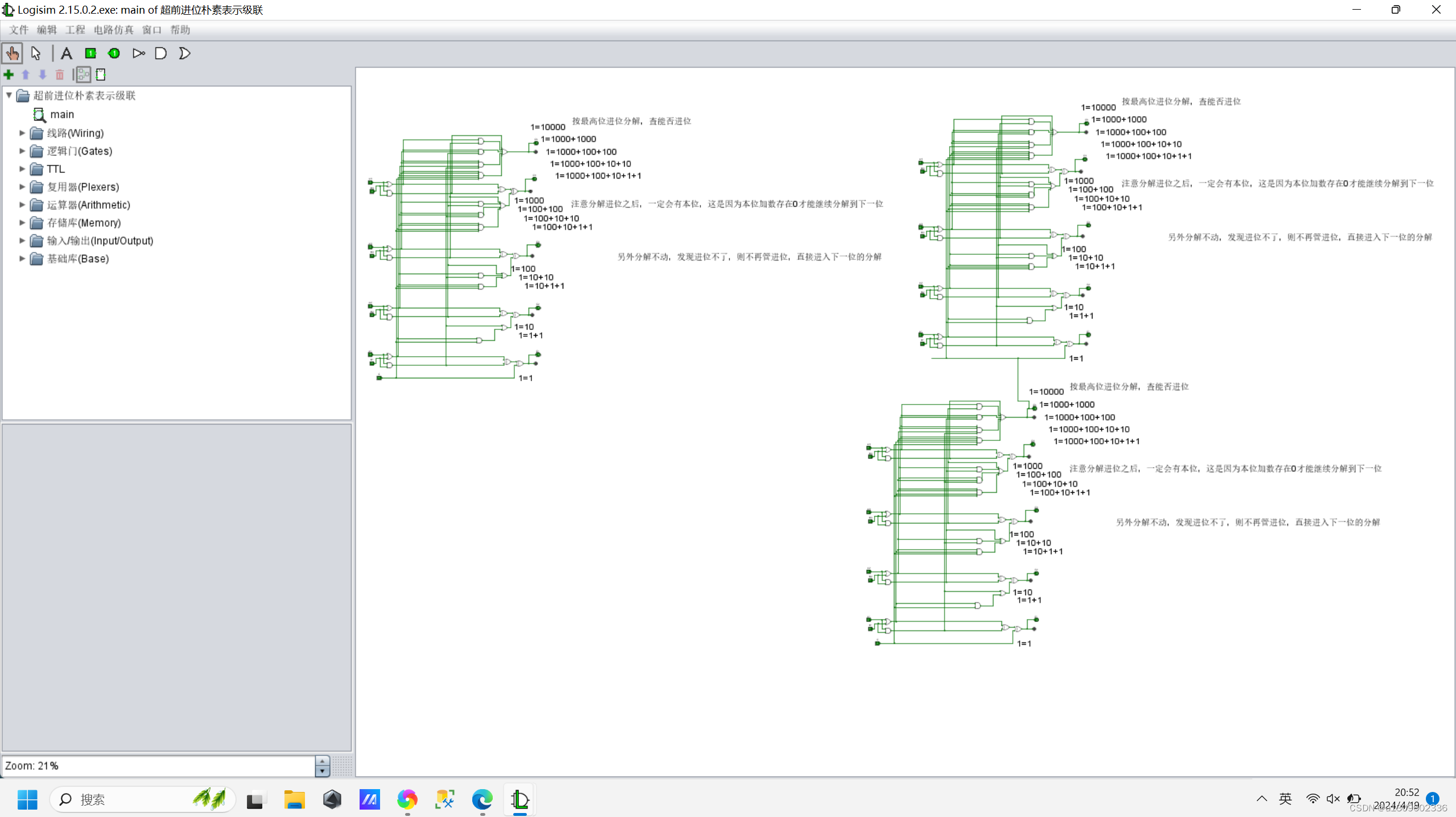

logisim 图解超前进位加法器原理解释

鄙人是视频作者,文件在视频简介的网盘链接。 找规律图解超前进位加法器与原理解释_哔哩哔哩_bilibili 一句话就是“把能导致进位到这个位置的情况全都穷举一遍。” 穷举情况看图中算式。 视频讲解比较啰嗦。

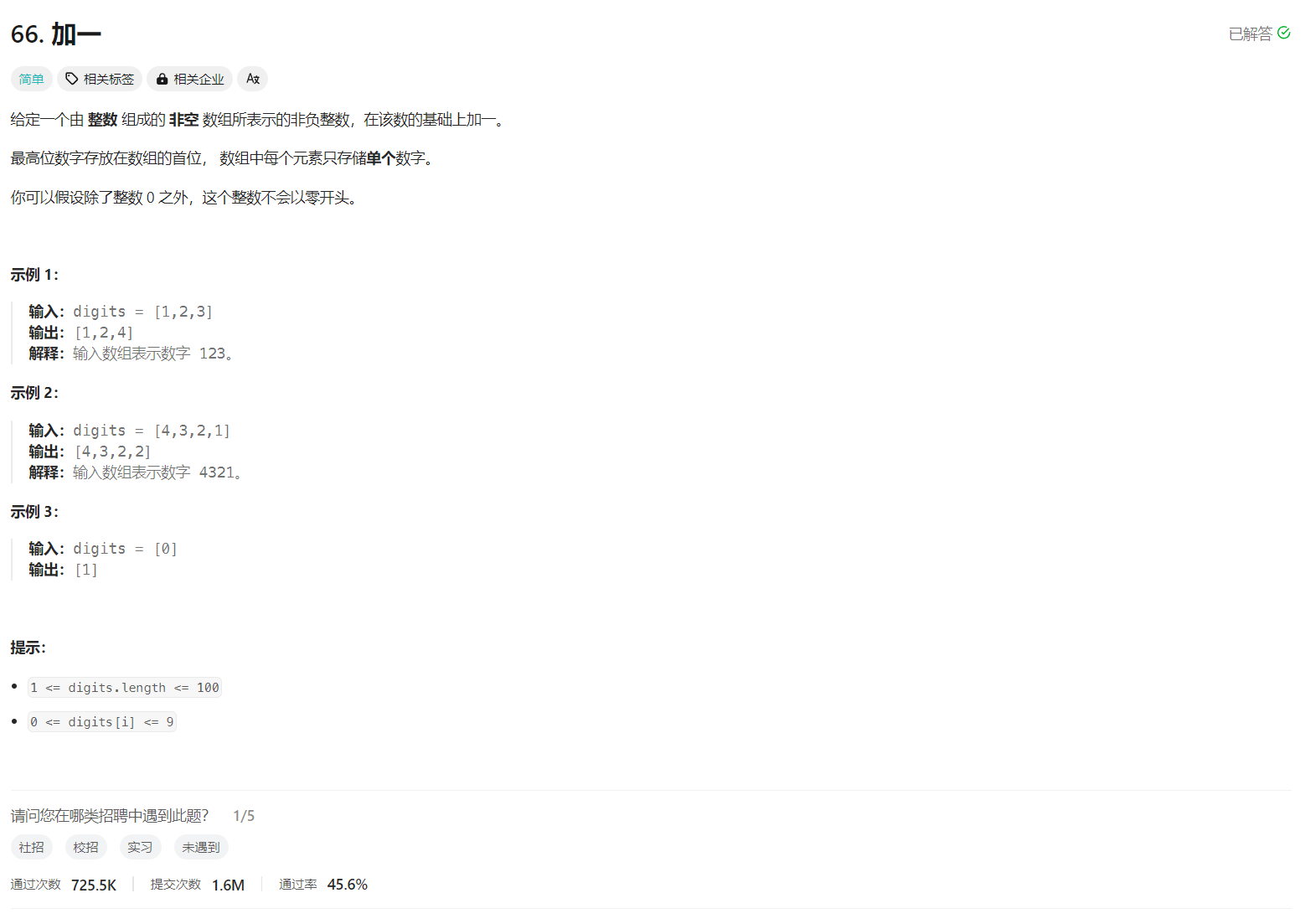

力扣面试150 加一 模拟 加法进位

Problem: 66. 加一 文章目录 思路复杂度Code 思路 模拟加法运算,逢十进一 复杂度 时间复杂度: O ( n ) O(n) O(n) 空间复杂度: O ( 1 ) O(1) O(1) Code class Solution {public int[] plusOne(int[] d) {int n = d.length;for(int i

【8086汇编】带进位的加法adc 和 带借位的减法sbb

1.adc 带进位加法指令add carry 示例:大数相加 应用:128位数据的相加 思路 代码 2.sbb 带借位的减法 sub borrow 示例

js、ts保留两位或n位小数,包括四舍五入 以及 不进位

javascript、typescript 保留两位或n位小数,包括四舍五入 和 不四舍五入进位 一般保留小数基本会先想到用toFixed(x),x区间[0,20],但会四舍五入 let num = 3.141592653;//n :3.142let n = num.toFixed(3); toPrecision(x),x区间[0,21],和上面的方法一样,但是会

Codeforces Round 807 (Div. 2)(C复制字符串找第k位 D 固定01段 E线段树上二分解决进位问题)

A.直接最小的n个数匹配最大的n个数 #include<bits/stdc++.h>using namespace std;const int N=1e6+10,M=2*N,mod=1e9+7;#define int long longconst long long inf=2e18;typedef pair<int,int> PII;typedef long long LL;us

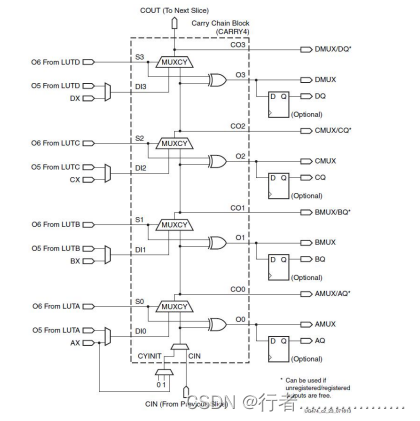

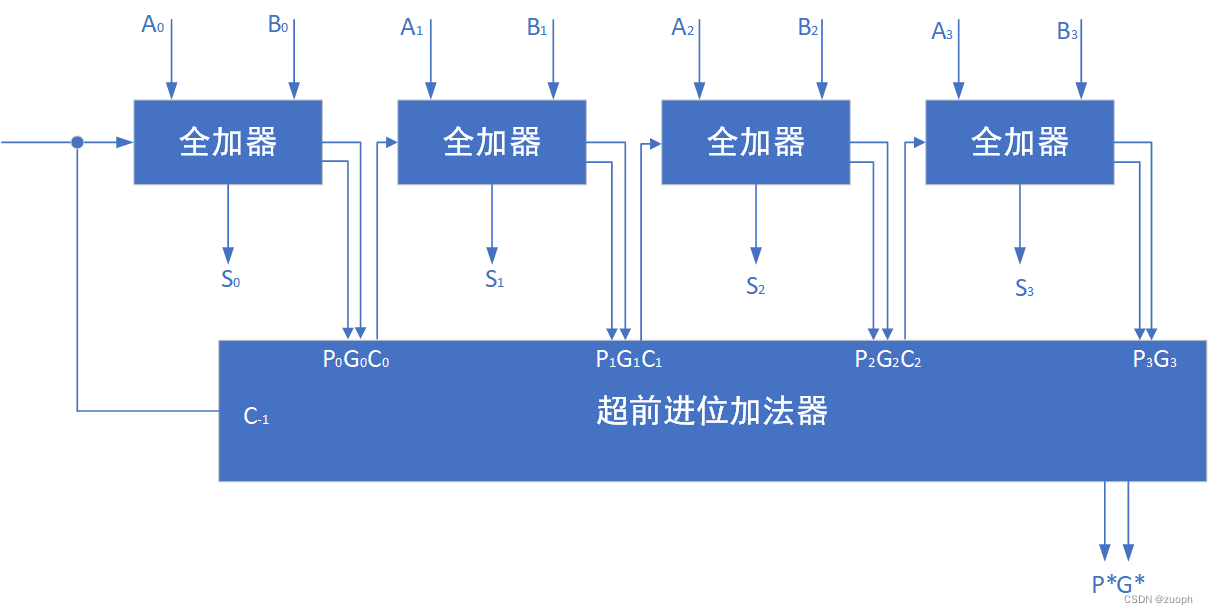

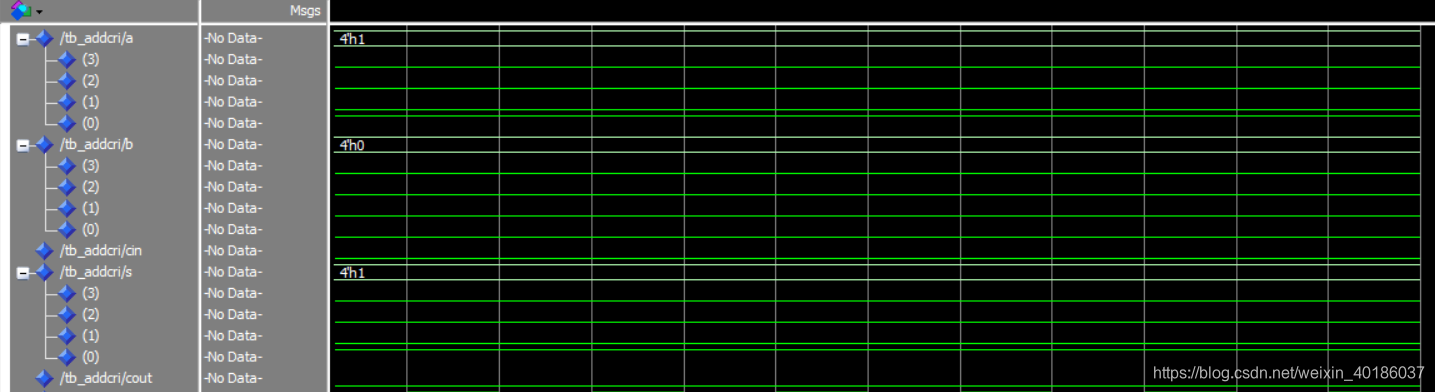

超前进位加法器(verilog)

文章目录 1.串行进位加法器2.超前进位加法器 加法器单元可以分为全加器和半加器,半加器没有输入进位端,所以半加器时两个比特相加,而全加器时3个比特相加。如下为一个1位半加器, 而一个1位全加器单元的逻辑门数量要比半加器多,: 1.串行进位加法器 多位数相加时,直接描述产生串行进位加法器。代码如下: //3位半加器module(cout,sum,a,b

【机组】算术逻辑单元带进位运算实验的解密与实战

🌈个人主页:Sarapines Programmer🔥 系列专栏:《机组 | 模块单元实验》⏰诗赋清音:云生高巅梦远游, 星光点缀碧海愁。 山川深邃情难晤, 剑气凌云志自修。 目录 🌺一、 实验目的 🌼二、 实验内容 🌻三、 实验详情 实验1:算术逻辑单元带进位位的加法运算实验 实验2:带进位移位实验 🍀四、 实验步骤 实验1 算术逻辑单元带进

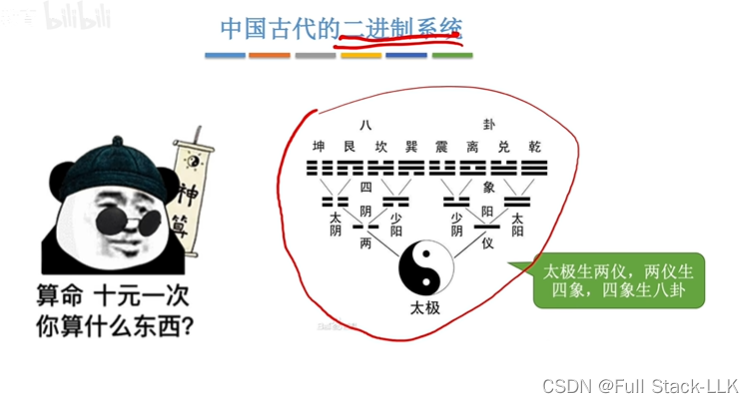

计算机组成原理-进位计数制(进制表示 进制转换 真值和机器树)

文章目录 现代计算机的结构总览最古老的计数方法十进制计数法推广:r进制计数法任意进制->十进制二进制<--->八进制,十六进制 各种进制常见的书写方式十进制->任意进制整数部分小数部分 十进制->二进制(拼凑法)真值和机器数小结中国古代的二进制系统 现代计算机的结构 总览 最古老的计数方法 一条竖线对应一个苹果,但数量太多竖线太多画不下 后来用横线表示5,所画的线可

算法:全排列问题——n进位法

对于输出1 ~ n这些数组成的所有全排列的方法有最暴力的递归枚举法和相对简单写的递归交换法,但是有时我们只希望可以找到一个全排列的下一个全排列,就这样出现了n进位法。 例题 洛谷1706 全排列问题 题目描述 输出自然数1到n所有不重复的排列,即n的全排列,要求所产生的任一数字序列中不允许出现重复的数字。 输入格式 一个整数n。 输出格式 由1~n组成的所有不重复的数字序列,每行一个序列

算法:全排列问题——递减进位法

求一个全排列的下m个全排列,我们发现递增进位法每次进位的次数太多,因此为了对其进行优化出现了递减进位法。 例题 原创例题 题目描述 求排列a[1],a[2],a[3],……,a[n]之后按递减进位法的第m个全排列。 输入格式 共三行。 第一行一个正整数N(1 <= N <= 10000)。 第二行一个正整数M(1 <= N <= 100)。 下一行是1到N这N个整数的一个排列,用空格隔开。

算法:全排列问题——递增进位法

求一个全排列的下m个全排列,有时我们并不想按字典序找,而是想换一种顺序去找。 例题 原创例题 题目描述 求排列a[1],a[2],a[3],……,a[n]之后按递增进位法的第m个全排列。 输入格式 共三行。 第一行一个正整数N(1 <= N <= 10000)。 第二行一个正整数M(1 <= N <= 100)。 下一行是1到N这N个整数的一个排列,用空格隔开。 输出格式 N个整数,表示

每日好题-A+B problem 高精度的加法和进位计算

C - A + B Problem Description 给定两个整数 A,B,计算A+B 的值,并计算出现进位的次数。 Input 两个整数 A,B(0≤A,B≤10^10^6)---没错就是10^1000000 Output 两行两个整数表示 A+B 的值与出现进位的次数。 Samples Sample #1 Input 1516 Output 311 Hin

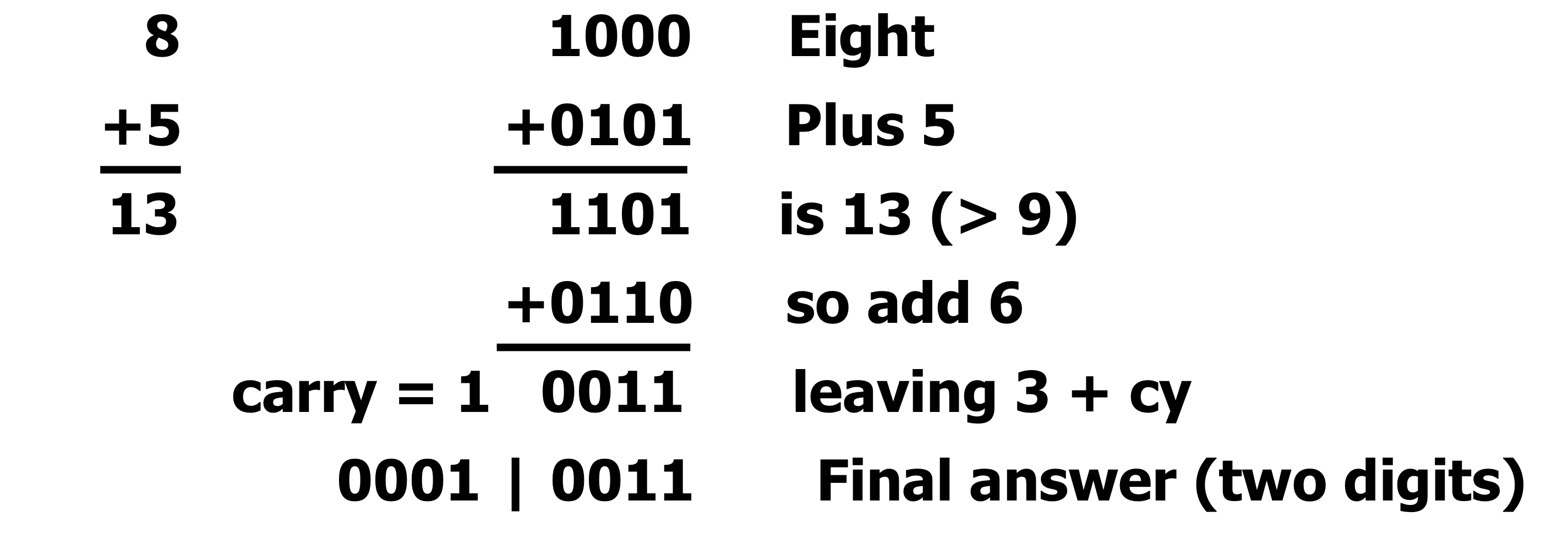

【FPGA】Verilog:BCD 加法器的实现 | BCD 运算 | Single-level 16 bit 超前进位加法器 | 2-level 16-bit 超前进位加法器

0x00 BCD 运算 在 BCD 中,使用4位值作为操作数,但由于只表示 0 到 9 的数字,因此只使用 0000 到 1001 的二进制数,而不使用 1010 到 1111 的二进制数(don't care)。 因此,不能使用常规的 2'complement 运算来计算,需要额外的处理:如果 4 位二进制数的运算结果在 1010 到 1111 的范围内,需要将 6 (即 0110)

数字逻辑电路基础-组合逻辑电路之4位先行进位加法器

文章目录 一、问题描述二、verilog源码三、仿真结果 一、问题描述 前面介绍4位行波进位全加器(串行加法器)的原理及verilog实现,但是它是一种串行加法器,当位数多时,比如32位的二进制数相加,由于进位逐位从低位向高位传递,这会造成相当大的延迟。对于需要快速加法运算的信号处理电路来说,我们需要对其进行改进,一个常见的想法就是将进位提前计算出来,这样我们可以实现一种称

【FPGA】Verilog:二进制并行加法器 | 超前进位 | 实现 4 位二进制并行加法器和减法器 | MSI/LSI 运算电路

Ⅰ. 前置知识 0x00 并行加法器和减法器 如果我们要对 4 位加法器和减法器进行关于二进制并行运算功能,可以通过将加法器和减法器以 N 个并行连接的方式,创建一个执行 N 位加法和减法运算的电路。 4 位二进制并行加法器 4 位二进制并行减法器 换句话说,4 位二进制并行加法器可以执行两个 4 位二进制数之间的加法运算,而 4 位二进制并行减法器可以执行两个 4

【HDL系列】进位旁边加法器原理与设计

一、进位旁边加法器 进位旁路加法器(Carry Skip Adder,CSA),也称Carry Bypass Adder。需要注意的是,CSA也是另外一种加法器——进位保存加法器(Carry Save Adder)的简称,关于这种加法器后期会介绍。 此前介绍了行波进位加法器RCA,第k位的进位Ck必须等待之前的Ck-1的结果才能计算出来,如下图进位c16必须等到前一级全加器的c15输出才可以计

linux 嵌入式汇编 adc,汇编语言ADC指令:带进位加法

ADC(带进位加法)指令将源操作数和进位标志位的值都与目的操作数相加。该指令格式与 ADD 指令一样,且操作数大小必须相同: ADC reg, reg ADC mem, reg ADC reg, mem ADC mem, imm ADC reg, imm 例如,下述指令实现两个 8 位整数相加 (FFh+FFh),产生的 16 位和数存入 DL:AL,其值为 01FEh: mov dl, 0 m

VHDL逐级进位加法器

关于逐级进位加法器: VHDL实现: library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity adder_cripple isgeneric(n:integer:=4);port(a,b:in std_logic_vector(n-1 downto 0);cin: in std_logic;s:out std_logic_vector(n-1 down

博弈论补充 异或(不进位加法)

博弈论 小游戏(可以和家人玩..讲真) (1)每次最多拿m+1个 (2)大脸盘子 放对称的 (3)有两堆石子 怎么放(数量不同) tips 1 在典型的nim问题中,一堆石子,(每次拿任意个)先手如果要赢,(输了就是-1),有多少种走法 *** 通过公式(石子数量直接异或可以拿到结果) 这个时候,先手是怎么赢的? 走任意的,就可以赢吗?并不是。 要想达到能够赢了的状态,要达到的是必胜客的状态