riscv专题

RISCV汇编编程讲解

第一章 引言 为什么要讲riscv? riscv的特点: -诞生于顶尖学术机构:诞生于加州大学伯克利分校的体系结构研究院。吸引了大批的顶尖企业参与(e.g. 谷歌、华为、高通、阿里巴巴为rsicv的发展提供了大量的资金支持和贡献了技术和人才)。 -精简指令集:指令相对精简,指令格式规整,易于实现和理解。只包含了最基本和常用的指令,避免了复杂

riscv 开发板 HiFive Unmatched 总览

板子在这里买 https://www.crowdsupply.com/sifive/hifive-unmatched资料在这里下 https://www.sifive.com/boards/hifive-unmatched 1_soc_datasheet_fu740-c000-manual-v1p3.pdf*2_板级软件总体介绍_hifive-unmatched-sw-reference-

riscv 的 CSR

每一个hart有一套寄存器(4096csr?+gpr+fpr) csr由riscv定义标准部分和厂家实现定义csr 分类1.标准和实现riscv privileged P6 2.2 CSR Listingmisamvendoridmarchidmimpidmhartidfflagsfrmfcsr // Float 指令扩展才有mstatusmtvecmepcmcausemtvalmiemip

riscv的异常与中断

文章目录 广义异常分类广义异常的发生广义异常处理流程狭义异常的编程狭义中断的编程 广义异常分类 riscv 的异常(广义的异常)包括 // 与 arm 类似 , 参考 https://blog.csdn.net/u011011827/article/details/117431707狭义的异常 // 异常总是同步的,精确的取指令访问到非法的地址空间读写数据访问地址属性出错取

riscv 常见的ABI

RISC-V 编译器支持多个 ABI,具体取决于 F 和 D 扩展是否存在。RV32 的 ABI 分别名为 ilp32,ilp32f 和 ilp32d。ilp32 表示 C 语言的整型(int),长整型(long)和指针(pointer)都是 32 位,可选后缀表示如何传递浮点参数。在 lip32 中,浮点参数在整数寄存器中传递;在 ilp32f 中,单精度浮点参数在浮点寄存器中传递;在

riscv 架构的思考

按道理,pc指到哪里,就应该执行哪里(前提是该位置支持XIP)该位置在 system memory map该位置最好还有二进制指令pc的设置,可以由reset jtag 异常(生成和返回) 跳转指令 和顺序加4/2 来改变条件分支、无条件分支、异常生成和异常返回指令 riscv汇编语法类似 arm,第一个是目标数,第二个是源操作数(S type 指令相反) 指令分类1.按功能2.按存储

openocd riscv 对应的jtag动作解析

openocd 服务器开启时1.探测存在的核心2.halt住核心3.读misa4.resume核心5.循环查询dmstatus traget remote时1.halt住核心2.读了X0-X31和PC2.读各种CSR寄存器(TODO) disconnect 时1. resume request openocd 服务器 被ctrl-c 结束时1. resume req

编译链中的riscv指令集与寄存器

编译链 https://blog.csdn.net/u011011827/article/details/120086961$ which riscv64-unknown-elf-gcc/home/suweishuai/x-tools/riscv64-unknown-elf/bin/riscv64-unknown-elf-gcc code FreeRTOSv202111.00/Free

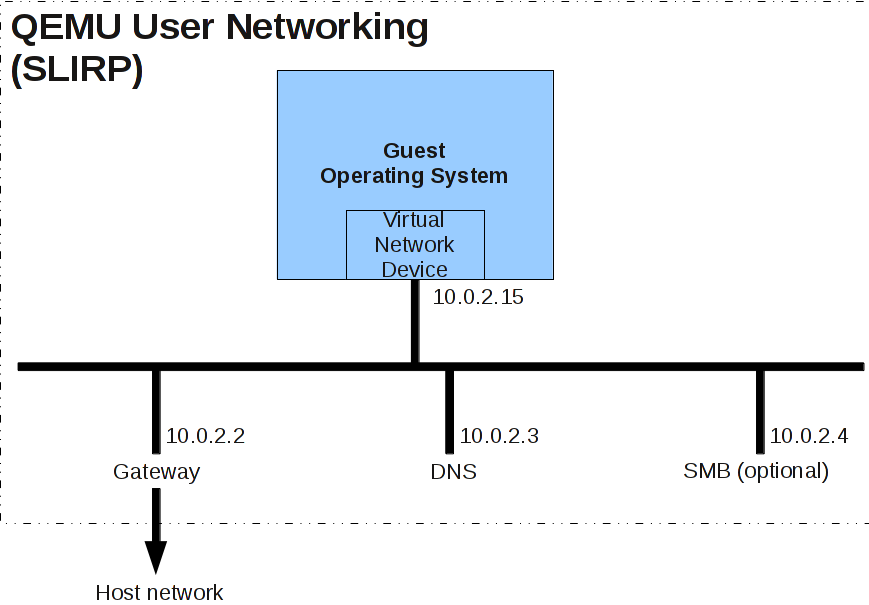

FreeBSD RISCV 在QEME中实践-网络配置

在前一篇文章中,我们一起进行了FreeBSD RISCV 在QEME中实践 现在,让我们配置好网络吧! 先上结论:用默认配置启动即可,网络就加载好了,只是不能ping罢了。因为不能ping,以为网络没通,走了一些弯路。这个坑帮大家踩过,大家就放心走吧! 调试坎坷历程 一开始不知道默认网络配置好了,到处看文档找解决方案。 看官方wiki:riscv - FreeBSD Wiki 当

使用riscv-tests进行指令测试(二)

使用riscv-tests进行指令测试(二) 1 测试用例命名规则2 测试用例dump文件介绍 本文属于《 TinyEMU模拟器基础系列教程》之一,欢迎查看其它文章。 1 测试用例命名规则 用例名称 = TVM Name + “-” + Target Environment Name + “-” + “指令” 比如,rv64ui-p-add,表示在用户模式下,测试ris

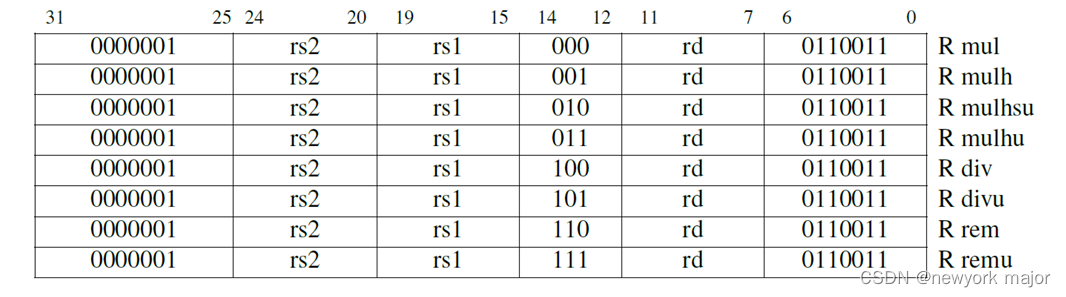

RISCV指令集体系简读之RV32M

RV32M向RV32I中添加了整数乘法和除法指令; RV32M具有有符号和无符号整数的除法指令:divide(div)和divide unsigned(divu),它们将 商放入目标寄存器。在少数情况下,程序员需要余数而不是商,因此RV32M提供 remainder(rem)和 remainder unsigned(remu),它们在目标寄存器写入余数,而不是商。要测试除数是否为零,只需要在

riscv-gnu-toolchain 交叉编译器如何构建?

安装依赖工具 sudo apt-get install git autoconf automake autotools-dev curl python3 libmpc-dev libmpfr-dev libgmp-dev gawk build-essential bison flex texinfo gperf patchutils bc libexpat-dev libglib2.0-dev

第六十一回 放冷箭燕青救主 劫法场石秀跳楼-编译安装飞桨paddlepaddle@openKylin+RISCV

卢俊义在水里被张顺抓住,用轿子抬到了梁山。宋江等人下马跪在地上迎接,请他坐第一把交椅。卢俊义宁死不从,大家只好说留他在山寨几天,先让李固带着马车货物回去。吴用对李固说,你的主人已经答应坐第二把交椅了,上山之前家里的四句诗是藏头诗,每句话的第一个字合起来就是“卢俊义反”。 在梁山大家每天都请卢俊义喝酒,每个头领都单独请,这样过了近两个月,卢俊义才离开梁山。快到家的时候见到浪子燕青,他说李固和卢俊义

ONNX @riscv+OpenKylin

安装onnxruntime-riscv 下载软件: git clone https://github.com/ucb-bar/onnxruntime-riscv apt install unzip cd onnxruntime-riscv && sh build.sh 报错... 改了g++环境变量部分还是不行,放弃。 安装onnxruntime 使用这个库 git clone

【2022集创赛】芯来RISCV杯全国三等奖作品:基于RISC-V的生理信号加速专用SOC

本篇文章是2022年第六届全国大学生集成电路创新创业大赛芯来RISC-V杯三等奖作品分享,参加极术社区的**【有奖征集】分享你的2022集创赛作品,秀出作品风采**活动。 1.团队介绍 参赛单位:上海理工大学 指导老师:闫士举 参赛队员:夏鹏、李宪龙、张涛 总决赛奖项:三等奖 2.项目简介 2.1项目背景 目前体外自动电除颤仪诊断不够准确、使用不够智能,急需提升诊断效率

ubuntu(20.04)+Riscv工具链编译licheeRvD1 linux内核(5.17.0)

ubuntu(20.04)+Riscv工具链编译licheeRvD1 linux内核(5.17.0) 注:Riscv工具链版本:riscv64-unknown-linux-gnu-gcc (g2ee5e430018) 12.2.0 编译riscv-gnu-toolchain来获取工具链请参考 https://blog.csdn.net/weixin_43283275/article/detai

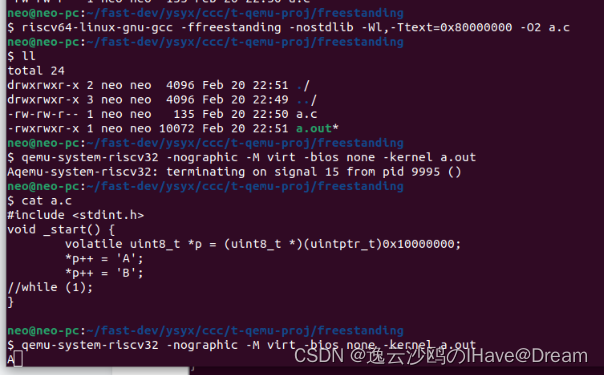

【riscv】使用qemu运行riscv裸机freestanding程序

文章目录 1. 运行显示2. 工具准备3. 裸机代码和编译3.1 源码3.2 编译 4. 使用qemu仿真运行riscv裸机程序 1. 运行显示 详见左下角, 运行时串口输出的字符 A ; 2. 工具准备 # for riscv64-linux-gnu-gccsudo apt-get install gcc-riscv64-linux-gnu# for qemu-syst

QEMUKVM 虚拟机实例demo以及RISCV上KVM的实现分析

KVM(Kernel Virtual Machine)是基于Linux内核的开源的虚拟化解决方案,KVM从linux-2.6.20版本开始被合入kernel主分支维护,成为linux的重要模块之一。KVM本身能够提供CPU虚拟化和内存虚拟化等部分功能,而其它设备的虚拟化和虚拟机的管理工作,则需要依靠QEMU完成,在KVM虚拟化环境中,一个虚拟机就是一个传统的Linux 进程,运行在Qemu-KVM

LLVM每日谈之二十六 riscv-llvm

说起riscv-llvm,可能一下子让人摸不到头脑,因为有些人没有关注RISC-V。如果从RISC说起,RISC-V, riscv-llvm都会变得更容易理解。RISC就是经常说的精简指令集,这在之前计算机行业的发展过程中起到的作用,怎么形容都不为过了。真正做过编译器相关和CPU相关工作的人,可能对这些有更深的感触。RISC-V简单点来说,就是一个开源版本的RISC,并且由于设计团队包含了很多之前

LLVM libc++的RISCV支持

libc++的官方主页:http://libcxx.llvm.org/ libc++文档主页:https://libcxx.llvm.org/docs/ 简介: libc++ is an implementation of the C++ standard library, targeting C++11, C++14 and above. All of the code in li

深入研究Clang(十九) Clang的RISCV支持2

前文Clang的RISCV支持1介绍了Clang中有关RISCV的代码主要集中在三个地方:Driver部分、Basic部分和CodeGen部分,并且对Basic部分和CodeGen部分的内容和关系进行了介绍,只有Driver部分因为涉及到了ToolChain、Tool和Command(job)等概念体系而未进行深入介绍。 在介绍完ToolChain、Tool和Command(job)等概念和调用

neovim调试xv6-riscv过程中索引不到对应头文件问题

大家好,我叫徐锦桐,个人博客地址为www.xujintong.com,github地址为https://github.com/jintongxu。平时记录一下学习计算机过程中获取的知识,还有日常折腾的经验,欢迎大家访问。 和这篇文章neovim调试linux内核过程中索引不到对应头文件问题 出现的问题一样。 也是通过生成一个compile_commands.json文件来解决。 生成co

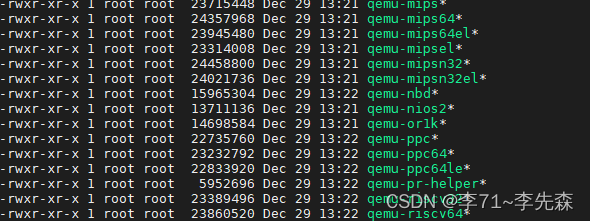

Ubuntu 18.04搭建RISCV和QEMU环境

前言 因为公司项目代码需要在RISCV环境下测试,因为没有硬件实体,所以在Ubuntu 18.04上搭建了riscv-gnu-toolchain + QEMU模拟器环境。 安装riscv-gnu-toolchain riscv-gnu-toolchain可以从GitHub上下载源码编译,地址为:https://github.com/riscv-collab/riscv-gnu-toolcha

[RISCV] 为android14添加一个新的riscv device

本篇博客将基于android-14-r18添加Sifive unmatched板子的支持。 Setup build envoronment Establishing a build environment $ sudo apt install git-core gnupg flex bison build-essential zip curl zlib1g-dev libc6-dev-i38

ArchLinux搭建riscv测试环境(失败)

参考 Boot an Arch Linux RISC-V using qemu-system - JieJiSS' Blog 安装ArchLinux安装所需包 sudo pacman -S arch-install-scripts git qemu-img qemu-system-riscvsudo pacman -S riscv64-linux-gnu-gcc 安装yay git