本文主要是介绍riscv 开发板 HiFive Unmatched 总览,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

板子在这里买 https://www.crowdsupply.com/sifive/hifive-unmatched

资料在这里下 https://www.sifive.com/boards/hifive-unmatched

1_soc_datasheet_fu740-c000-manual-v1p3.pdf*

2_板级软件总体介绍_hifive-unmatched-sw-reference-manual-v1p0.pdf*

3_产品硬件简介_HiFive Unmatched Product Brief (released).pdf

4_产品硬件介绍_hifive-unmatched-datasheet.pdf*

5_产品入门指南_hifive-unmatched-gsg-v1p4_ZH.pdf*

6_电路图_hifive-unmatched-schematics-v3.pdf*

7_SDK介绍.png*

A_bom表_bill-of-materials-hifive-unmatched-3b0.pdf*

B_3D模型_hf105-mech-3.step*

C_购买渠道及产品介绍.png*

D_资料整体简介.png*

硬件总览

- 之前做了硬件介绍,位于 市面上的单板计算机中的 HiFive Unleashed

总介SOC 4*U74 + 1*S7内存16GB DDR4存储1.32 MB Quad SPI Boot Flash2.SD卡槽3.M.2 M-Key Slot网络Gigabit Ethernet Port其他4*USB-TypeA1*USB串口1*JTAGPCIE卡槽M.2 E-Key Slot

- soc 特性

宣传指标a high-performance multi-core, 64-bit dual-issue, superscalar RISC-V processorThe Freedom U740 SoC is the highest performance RISC-V processor available today硬指标Operating Frequency @ 1.2 GHzDual-issue in-order 64-bit execution pipeline4 个 U74RV64IMAFDC32KB I-Cache / 32KB D-Cache per coreM S U 三mode虚拟内存1 个 S7RV64IMAC16KB I-Cache / 8KB DTIMM U 两mode物理内存2 MB Coherent Banked L2-Cache

软件总览

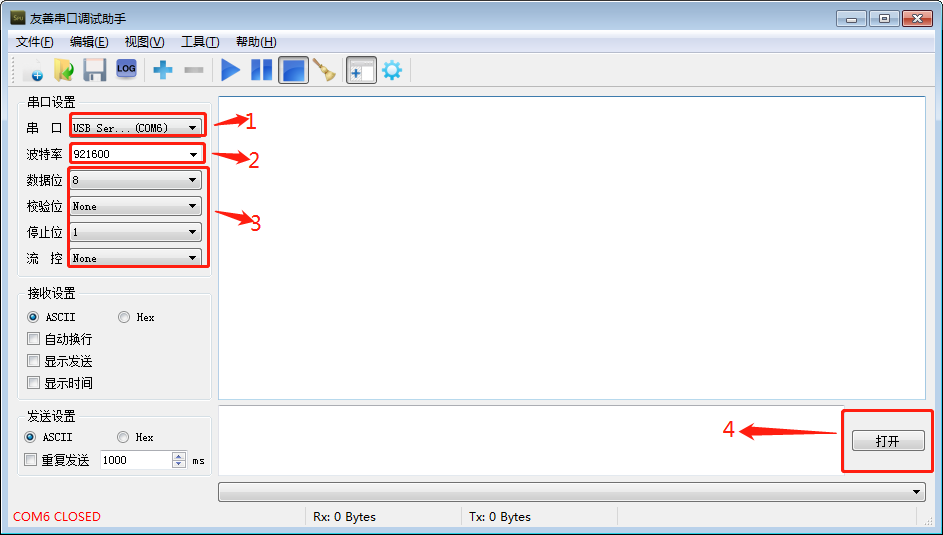

Reset vector ROM位置 : mask ROM 中的 0x1000-0x1020 上电后 所有核心的 pc(每个核心有一个pc寄存器) 位于 0x1004会根据 MSEL[3:0] 选择 jump 到1. loops forever waiting for debugger2. jump to memory-mapped QSPI0 // 0x2000_00003. jump to memory-mapped QSPI1 // 0x3000_00004. jump to ZSBLbootrom/ZSBL:位置 : mask ROM // memory-mapped 0x0000_1000-0x0000_1FFF会根据 MSEL[3:0] 选择 load 的数据 // 用 QSPI 接口 从 QSPIFlash 和 sdcard1.根据 MSEL[3:0] 判定即将load的数据(u-boot spl)在哪里2.load该数据到内存3.跳转波特率 89856 8n1可以用 57600 来解析如果有错误,就会打印信息, 如Error 0x00000000000000019如果没错误,不会打印信息第0阶段引导加载程序(ZSBL)包含在0x1_0000的掩码ROM中。它负责从GUID分区表下载更复杂的U-Boot SPL。所有hart都直接从外部时钟输入输入输入ZSBL,预期为26 MHz。具有mhartid zero的内核配置外围时钟分配器,然后搜索GUID类型为5B193300-FC78-40CD-8002-E86C45580B47的分区。 // mhartid 为 非0 的核心呢 ? 它首先下载GPT头(字节512-604),然后逐块(512字节)顺序扫描分区表,直到找到分区。然后,将该分区的全部内容U-Boot SPL下载到地址0x0800_0000处的L2 LIM中。然后执行分支到U-Boot SPL。u-boot spl : 会根据 MSEL[3:0] 判断 opensbi 在哪里1.根据 MSEL[3:0] 判定即将load的数据(opensbi)在哪里2.load该数据到内存3.跳转波特率 115200 8n1U-Boot辅助程序加载程序(SPL)从位于0x0800_0000的L2 LIM执行。它负责准备从DDR运行的系统。它执行以下操作:•配置DDR PLL、PHY和控制器•将GEM GXL TX PLL设置为125 MHz并重置•如果有外部PHY,请将其重置•从GUID类型为2E54B353-1271-4842-806F-E436D6AF69851的分区下载OpenSBI和U-boot和u-boot的设备树dtb 到 0x8000_0000// U-Boot SPL读取MSEL开关以确定在何处查找该分区•在OTP上扫描芯片序列号•将嵌入式DTB复制到DDR,填写U-Boot SPL版本、内存大小和MAC地址•启用16个L2方式中的15个(这将删除几乎所有L2 LIM内存)•跳转到DDR内存(0x8000_0000)opensbiOpenSBI从位于0x8000_0000的DDR执行,并保持驻留在该位置的内存中。它负责提供监控二进制接口(SBI)以及模拟芯片本身未实现的任何RISC-V所需指令。// openSBI 应该跳到了 U-boot// U-boot 是什么时候 被加载到内存的呢?// 猜想是 U-boot SPL // U-Boot SPL then loads and starts the next boot stage, consisting of OpenSBI and U-Boot, from the micro SD card into DRAM.// U-boot 在哪里 不是 Sifive 规定的波特率 没有打印,在 linux boot 阶段 打印出来u-bootU-Boot管理用于加载Linux内核的硬件。在板级,U-Boot在控制台串行端口上公开命令行接口。有关U-Boot SiFive使用U-Boot的更多信息,请参阅HiFive Unmatched Software Reference Manual(HiFive Unmatched软件参考手册)。波特率 115200 8n1

linux波特率 115200 8n1

systemd波特率 115200 8n1

- 启动流程中 sifive 规定了什么

Reset vector ROM 的代码及位置及执行 是 固定的, 动不了

bootrom/ZSBL 的代码及位置及执行是固定的,动不了

u-boot spl 的 代码及位置 及执行是可选的

opensbi 的 代码及位置及执行是由 u-boot spl(也就是用户)定的,但是 sifive 给出了建立 // 不建议改动,当然也可以改

u-boot 的代码及位置及执行是可选的 // 可以改动

linux 的代码及位置及执行是可选的

systemd 的代码及位置及执行是可选的

Hifive Unmatched 当前配置

Reset vector ROM 和 bootrom/ZSBL 在 soc 中

u-boot-spl opensbi u-boot linux rootfs 在 sd中

sd 被分成了4个分区分区1 : type : raw , u-boot-spl分区2 : type : raw , opensbi u-boot u-boot的设备树分区3 : type : fat16 , 内核, 内核的设备树 , u-boot配置文件分区4 : type : ext4 , rootfs

SMP 如何boot

TODO

S7 肯定不跑 opensbi

这篇关于riscv 开发板 HiFive Unmatched 总览的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!