本文主要是介绍编译链中的riscv指令集与寄存器,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

- 编译链

https://blog.csdn.net/u011011827/article/details/120086961

$ which riscv64-unknown-elf-gcc

/home/suweishuai/x-tools/riscv64-unknown-elf/bin/riscv64-unknown-elf-gcc

- code

FreeRTOSv202111.00/FreeRTOS/Demo/RISC-V-Qemu-virt_GCC 编译选项.c

-D__riscv_float_abi_soft // define 宏 ,在本例中没用到

-DportasmHANDLE_INTERRUPT=handle_trap // 在 Source/portable/GCC/RISC-V/portASM.S 被 jal

-march=rv32ima // Specify the name of the target architecture and, optionally, one or more feature modifiers.// 对于armv8 , 可填入 armv8-a, armv8.1-a, armv8.2-a, armv8.3-a, armv8.4-a, armv8.5-a// 对于armv7 , 可填入 armv7-a+vfpv4// 对于riscv , 可填入 RV32IMAFDC// 表示要生成哪一类 汇编指令

-mabi=ilp32 // Generate code for the specified ABI. // Permissible values are: apcs-gnu, atpcs, aapcs, aapcs-linux and iwmmxt.// 表示要遵循的 ABI 调用标准(Calling Convention)// RISC-V 编译器支持多个 ABI,具体取决于 F 和 D 扩展是否存在。RV32 的 ABI 分别名 为 ilp32,ilp32f 和 ilp32d// RISC-V-Reader-Chinese-v2p1.pdf P49// 参考 https://blog.csdn.net/zoomdy/article/details/79353313

-mcmodel=medany

-Wall // turns on the following warning flags

-fmessage-length=0 // 尝试格式化错误消息,使其适合大约n个字符的行。如果n为零,则不进行换行;每条错误消息显示在一行上。这是所有前端的默认设置。

-ffunction-sections //如果目标支持任意节,则将每个函数或数据项放入输出文件中自己的节中。函数名或数据项名决定了输出文件中节的名称。

-fdata-sections //如果目标支持任意节,则将每个函数或数据项放入输出文件中自己的节中。函数名或数据项名决定了输出文件中节的名称。

-fno-builtin-printf // 不使用编译器内建的 printf 函数链接

-O2 // 参考 https://blog.csdn.net/u011011827/article/details/121077950

-MMD // 只用用户头文件,而不是系统头文件 , 且生成.d文件

-MP // .d 文件的格式

-I ..编译选项.S

-D__riscv_float_abi_soft

-DportasmHANDLE_INTERRUPT=handle_trap

-march=rv32ima

-mabi=ilp32

-mcmodel=medany // Generate code for the medium-any code model. The program and its statically defined symbols must be within any single 2 GiB address range. Programs can be statically or dynamically linked.

-MMD

-MP

-I ..链接选项

riscv64-unknown-elf-gcc

-nostartfiles

-Tfake_rom.lds

-Xlinker --gc-sections

-Xlinker --defsym=__stack_size=300

xxx.o

-o

build/RTOSDemo.axf- dump

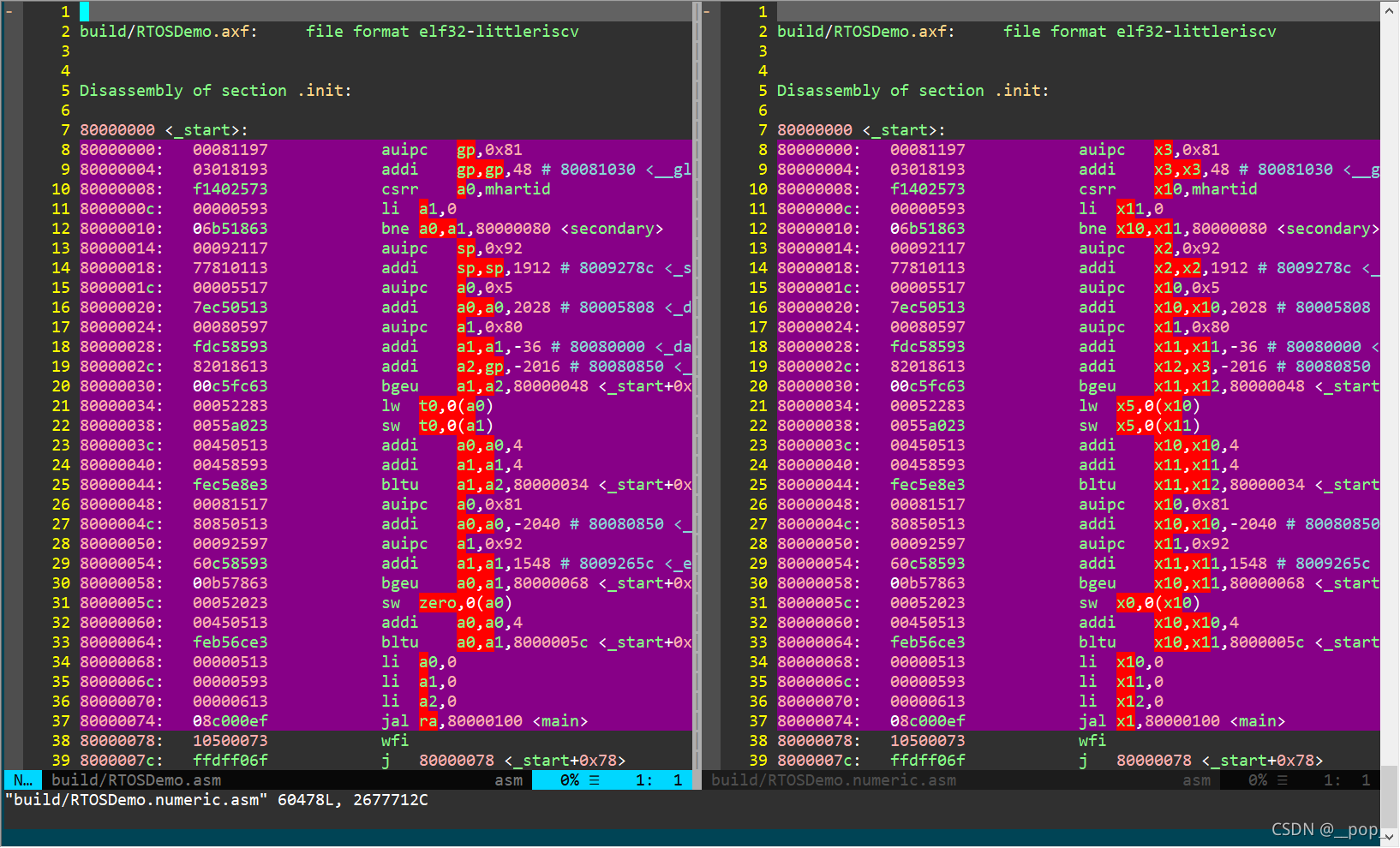

riscv64-unknown-elf-objdump: supported targets: elf64-littleriscv elf32-littleriscv elf64-little elf64-big elf32-little elf32-big pluginsrecsymbolsrecverilogtekhexbinaryihexriscv64-unknown-elf-objdump: supported architectures: riscv // 该选项 会根据 实际的 .o 来判断 是转成 rv64 还是 rv32riscv:rv64riscv:rv32pluginThe following RISC-V-specific disassembler options are supported for use with the -M switch (multiple options should be separated by commas):以下RISC-V特定反汇编程序选项支持与-M开关一起使用(多个选项应以逗号分隔):numeric Print numeric register names, rather than ABI names.数字打印数字寄存器名称,而不是ABI名称。no-aliases Disassemble only into canonical instructions, rather than into pseudoinstructions.没有别名只能分解为规范指令,而不是伪指令。

- riscv64-unknown-elf-gcc 可编译的 汇编格式

// riscv64-unknown-elf-objdump -D build/RTOSDemo.axf > build/RTOSDemo.asm

// riscv64-unknown-elf-objdump -M no-aliases -M numeric -D build/RTOSDemo.axf > build/RTOSDemo.no-aliases-numeric.asm

寄存器 字符串1. 默认 : ABI 名称的 寄存器(zero ra sp gp 等) RISC-V-Reader-Chinese-v2p1.pdf P30 2. "-M numeric" : X0 X1 类似名称

指令 字符串1. 默认: : 标准指令+伪指令(TODO) // 伪指令和编译器强相关 // RISC-V-Reader-Chinese-v2p1.pdf P117 有所有的标准指令和伪指令2. "-M no-aliases" : 标准指令 RISC-V-Reader-Chinese-v2p1.pdf P3 P4

寄存器的访问GPRs : 0x1000 – 0x101fRV32IMA指令Floating point registers : 0x1020 – 0x103fRV32IMA指令RV32FD指令CSRs : 0x0000 – 0x0fffRVZicsr指令

这篇关于编译链中的riscv指令集与寄存器的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!