指令集专题

字节全员标配的内部指令集鼠标垫,我的粉丝每人包邮送一块

最近很多粉丝后台说 steam 都开夏促了,看公号这么久有啥福利没……年中了是该给大家发点福利,我仔细琢磨了一下,找大厂的朋友要了一套他们撸了多年的 Java 算法逻辑 + 面试要点的私货,于是叫上合作伙伴,加急定制了一波桌面大鼠标垫! 很大…很爽、很实用 这批鼠标垫市面上必然买不到,从供应商给我的设计图来看, B 格还是不错的(拿来垫桌子也很实用)。不卖关子,从事 Java 工作的见者有份,

嵌入式:Arm v7-M指令集架构中的字节序(大小端)

相关阅读 嵌入式https://blog.csdn.net/weixin_45791458/category_12768532.html?spm=1001.2014.3001.5482 本文来源于博主无意之中的一个发现,虽然之前就知道Cortex-M3默认为小端模式,但是偶然发现了一些出乎意料的情况。 首先来看看Arm v7-M指令集架构中相关的定义。

ARM指令集——状态寄存器访问指令

ARM中有两条指令用于状态寄存器和通用寄存器之间传送数据。程序不能直接修改CPSR中的T控制位直接将程序状态切换到Thumb状态,必须通过BX等指令完成程序状态的切换。通常修改状态寄存器时通过“读取-修改-写回”的操作序列来实现的。状态寄存器访问指令包括以下两条指令: MRS 状态寄存器到通用寄存器的传送指令MSR 通用寄存器到状态寄存器的传送指令 下面一一介绍之: 1、MRS

ARM指令集——乘法指令

ARM有两类乘法指令:一类为32位的乘法指令,即乘法操作的结果为32位;另一类位64位的乘法指令,即乘法操作的结果为64位。两类指令共有以下6条: MUL 32位乘法指令MLA 32位带加数的乘法指令SMULL 64位有符号数乘法指令SMLAL 64位带加数的有符号乘法指令UMULL 64位无符号数乘法指令UMLAL 64位带加数的无符号数乘法指令 下面一一介绍之: 1、M

ARM指令集——数据处理指令篇

输出传送指令包括以下指令: MOV 数据传送指令MVN 数据求反传送指令CMP 比较指令CMV 基于相反数的比较指令TST 位测试指令TEQ 相等测试指令ADD 加法指令SUB 减法指令RSB 逆向减法指令ADC 带位加法指令SBC 带位减法指令RSC 带位逆向减法指令AND 安位与指令BIC 为清零指令EOR 逻辑异或指令ORR 逻辑或指令 下面分别作详细介绍: 1、MO

arm接口技术二--指令集与异常处理

arm汇编工程 注意事项: 魔法棒 - listing的两个选项勾上Linker --- Text Start: 指定指针起始地址0x0品按钮 – Folder选择arm-none-eabi编译器assemble编译报错:KEIL中错误FCARM - Output Name not specified, please check ‘Options for Target - Utilit解决方法

C++系统相关操作4 - 获取CPU(指令集)架构类型

1. 关键词2. sysutil.h3. sysutil.cpp4. 测试代码5. 运行结果6. 源码地址 1. 关键词 关键词: C++ 系统调用 CPU架构 指令集 跨平台 实现原理: Unix-like 系统: 可以通过 uname -m 命令获取 CPU 架构类型。Windows 系统: 可以通过环境变量 PROCESSOR_ARCHITECTURE 获取 CPU 架构类型。

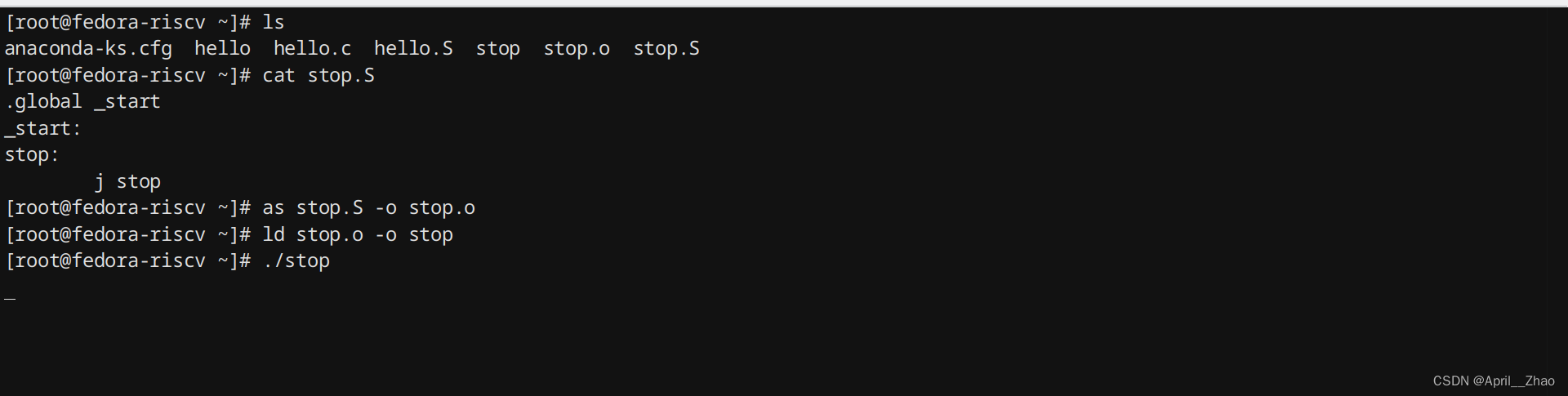

01_RISC-V 入门及指令集学习

参考文档 risc-v入门:https://blog.csdn.net/bebebug/article/details/128039038RISC-V OS:https://blog.csdn.net/bebebug/article/details/130551378riscv-spec文档:https://riscv.org/wp-content/uploads/2019/12/riscv-s

使用SSE指令集来优化程序

SSE和SSE2的指令系统非常相似,SSE2比SSE多的仅是少量的额外浮点处理功能、64位浮点数运算支持和64位整数运算支持。 SSE为什么会比传统的浮点运算更快呢?因为它使用了128位的存储单元,这对于32位的浮点数来讲,是可以存下4个的,也就是说,SSE中的所有计算都是一次性针对4个浮点数来完成的。 虽然SSE从理论上来讲要比传统的浮点运算会快,但是所受的限制也很

CPU中的寄存器CPU能理解的指令(指令集)

CPU中的寄存器 寄存器有很多种。如指令寄存器,专门存储指令 问:CPU的寄存器存的是什么? 答:CPU寄存器是中央处理器(CPU)内部的一小部分高速存储资源,用于快速访问和存储各种类型的数据和信息。以下是CPU寄存器通常存储的一些内容: 指令:某些CPU寄存器(如指令寄存器,IR)用于存储当前正在执行的指令。 操作数:操作数寄存器用于存储指令的操作数,这些操作数是计算

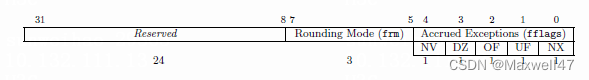

RV32F\RV32D指令集

RV32F\RV32D指令集 F扩展1、浮点控制状态寄存器2、指令类型 F扩展 F扩展增加了32个浮点寄存器f0-f31,每个32位宽,以及一个浮点控制和状态寄存器fcsr,其中包含浮点单元的工作模式和异常状态。FLEN=32表示F单精度浮点扩展,大多数浮点指令对浮点寄存器中的值进行操作。浮点加载和存储指令在寄存器和内存之间传输浮点值。还提供了将值传入和传出整数寄存器的说明。

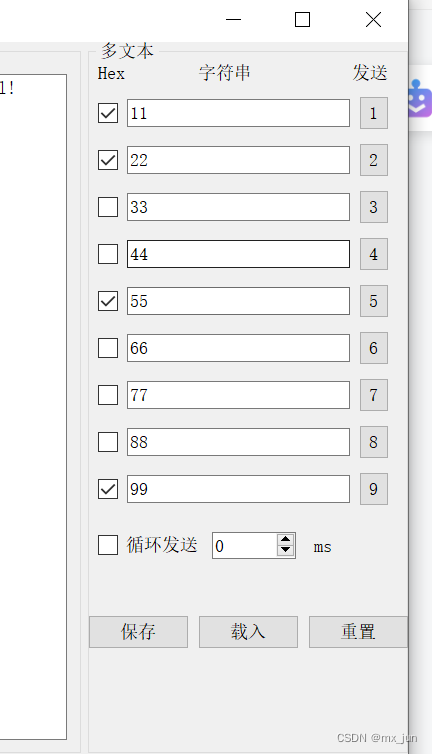

从零开始实现自己的串口调试助手(9)-重置多文本框,保存/载入指令集

重置多文本框 添加多文本控件列表 在构造函数中把我们需要操作的控件归类到对应列表之中 //创建多文本存放数组 - 存放那三列内容 checkBox lineEdi btnfor(int i=1;i<=9;i++){// 添加到按钮数组QString btnName = QString("pushButton_t%1").arg(i); //构建对应控件名QPushButton

ios指令集以及基于指令集的app包压缩策略

iPhone指令集 本文所讲的内容都是围绕iPhone的CPU指令集(想了解ARM指令集的同学请点击 这里),现在先说说不同型号的iPhone都使用的是什么指令集: ARMv8/ARM64 = iPhone 5s, iPad Air, Retina iPad Mini ARMv7s = iPhone 5, iPhone 5c, iPad 4 ARMv7 = iPhone 3GS

ARM指令集详解(带实例)

ADC : 带进位的加法 (Addition with Carry) ADC{条件}{S} <dest>, <op 1>, <op 2>dest = op_1 + op_2 + carry ADC 将把两个操作数加起来,并把结果放置到目的寄存器中。它使用一个进位标志位,这样就可以做比 32 位大的加法。下列例子将加两个 128 位的数。 128 位结果: 寄存器 0、1、2、和 3 第

iOS逆向基础:1、汇编语言 2、指令集(虚拟化首先要先接口标准定义,然后再在别人接口之上完成了一套自己的实现)3、调试工具:GDB与LLDB 4、iOS系统架构

文章目录 前言I、汇编语言II、指令集2.1 虚拟系统的简单实现2.2 CPU的组成2.3 CPU指令集2.4 主流的CPU指令集或CPU架构体系2.4.1 x86架构2.4.2 [ARM指令集](https://blog.csdn.net/z929118967/article/details/78276307)2.4.3 MIPS架构2.4.4 POWER -PC 2.5 CPU体系的分类

编译链中的riscv指令集与寄存器

编译链 https://blog.csdn.net/u011011827/article/details/120086961$ which riscv64-unknown-elf-gcc/home/suweishuai/x-tools/riscv64-unknown-elf/bin/riscv64-unknown-elf-gcc code FreeRTOSv202111.00/Free

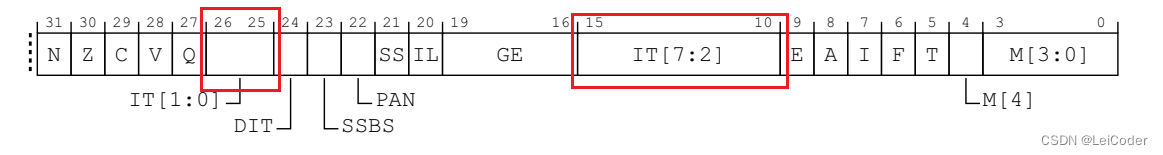

spsr 的恢复出错,导致 thumb 指令集的 it 条件运行指令运行异常,清晰的调试思路帮助快速解决问题

记一次调试过程 这是一个在 arm 架构上的 RTOS 上的调试过程。问题现象为使用 thumb 指令集的 libgcc 库的情况下,浮点运算随机出错。经过一番追踪调试,逐步缩小问题范围,最后定位问题,成功解决。 场景 在某款的国产 RTOS 上,由于客户应用需要,使用了thumb 指令集编译的 libgcc 的库,导致了同时运行了 arm 指令集和 thumb 指令集的代码。原本的 RTO

RV32I指令集及其编码方式解读

文章目录 前言RISCV指令集的模块化RV32IR型指令I型指令load指令 (I型) S型指令B型指令 (S型指令变体)PC相对地址B型指令简单举例 U型指令LUI指令li伪指令 AUIPC指令 J型指令(U型指令变体)JAL指令JALR指令(I型指令) 注参考 前言 R I S C − V RISC-V RISC−V 表示精简指令集计算机 R I S C ( R

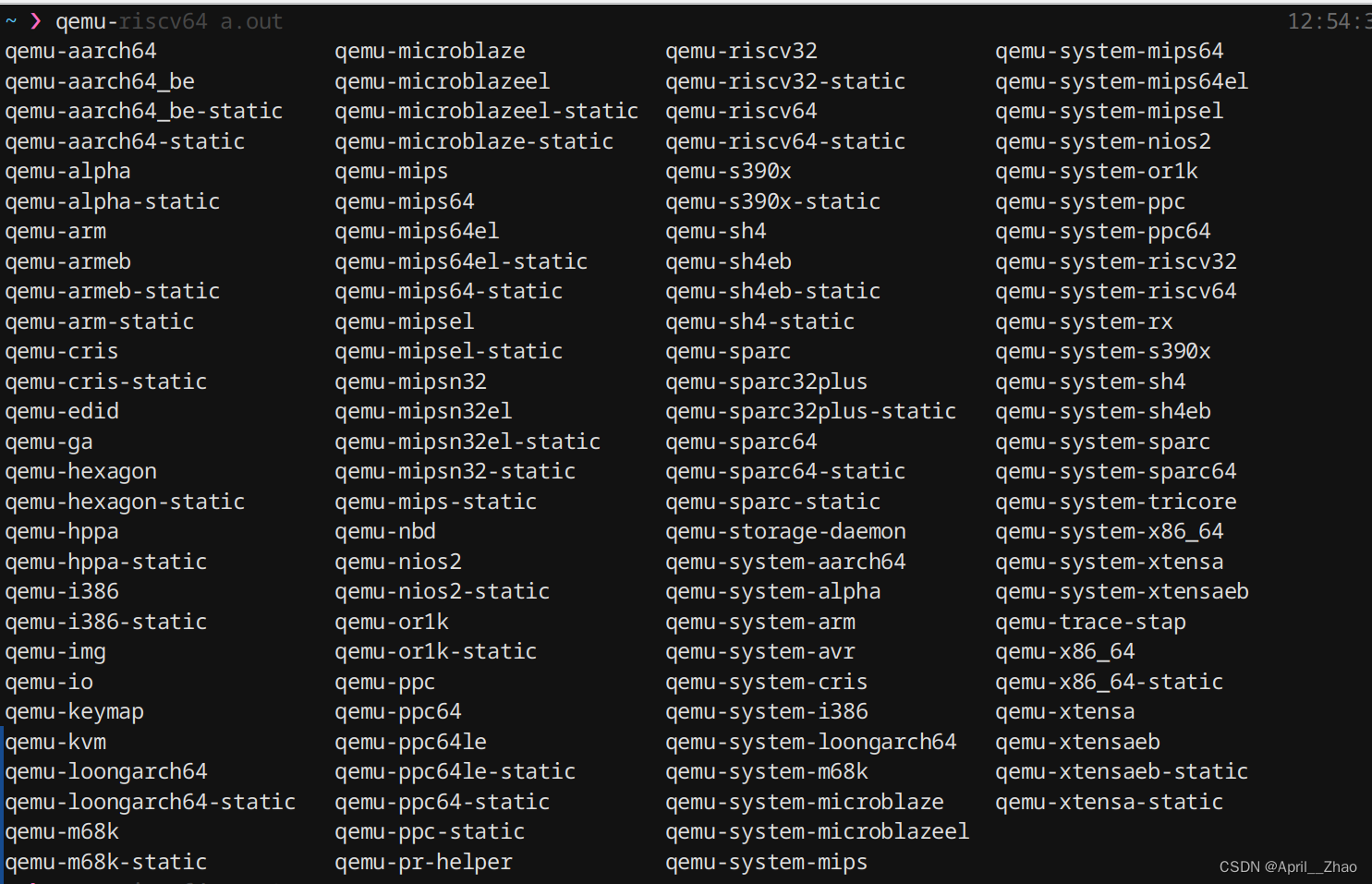

【跟我学RISC-V】(一)认识RISC-V指令集并搭建实验环境

写在前面 现在计算机的体系架构正是发展得如火如荼的时候,占领桌面端市场的x86架构、占领移动端市场的arm架构、在服务器市场仍有一定地位的mips架构、国产自研的指令集loongarch架构、还有我现在要讲到的新型开源开放的RISC-V指令集架构。 我先说一说我的学习经历,三年前我开始学习x86架构,不得不说x86架构这么多年的发展变得是真的非常复杂和难以概括,它为了兼容性,不得不保留一些早期

jvm(3)-运行时数据区、指令集

1. Runtime Data Area and Instruction Set(运行时数据区和指令集) 1.1 jvm运行时数据区 分为以下几部分: jvm stacks ,就是我们常说的栈,栈里面包含frame(窗口,也叫栈帧)Program Counter,简称PCmethod area 方法区,包括常量池。native method stacks,本地方法栈。Direct, 直接内存

记ARM NEON指令集深度优化

最近和同事一直讨论优化的事情,优化这个概念是模糊的,通常我们都是为了达到某种性能才考虑优化,当某种算法跑在CPU上较为消耗算力,达不到性能指标,可能就要优化。如果我们的代码是用JAVA编写的,那么可以使用Native(C/C++)语言替代其实现。如果Native语言还是无法满足性能要求,那么我们首先想到的应该是如何将Native实现为最优的版本,比如可以使用空间换时间—将一部分固定值先计算好,通过

【跟我学RISC-V】认识RISC-V指令集并搭建实验环境

写在前面 现在计算机的体系架构正是发展得如火如荼的时候,占领桌面端市场的x86架构、占领移动端市场的arm架构、在服务器市场仍有一定地位的mips架构、国产自研的指令集loongarch架构、还有我现在要讲到的新型开源开放的RISC-V指令集架构。 我先说一说我的学习经历,三年前我开始学习x86架构,不得不说x86架构这么多年的发展变得是真的非常复杂和难以概括,它为了兼容性,不得不保留一些早期

CentOS7-部署指令集

Systemd systemctl 服务管理 字母 d 是守护进程(daemon)的缩写。 Systemd 这个名字的含义,就是它要守护整个系统。 systemd 是用于管理 Linux 系统的初始化过程和后台服务的初始化系统,在 systemd 中,所有的服务、套接字、设备等都被视为 UNIT,翻译为单元。 systemctl 是用于与 systemd 交互的 命令行工具。systemctl