eda专题

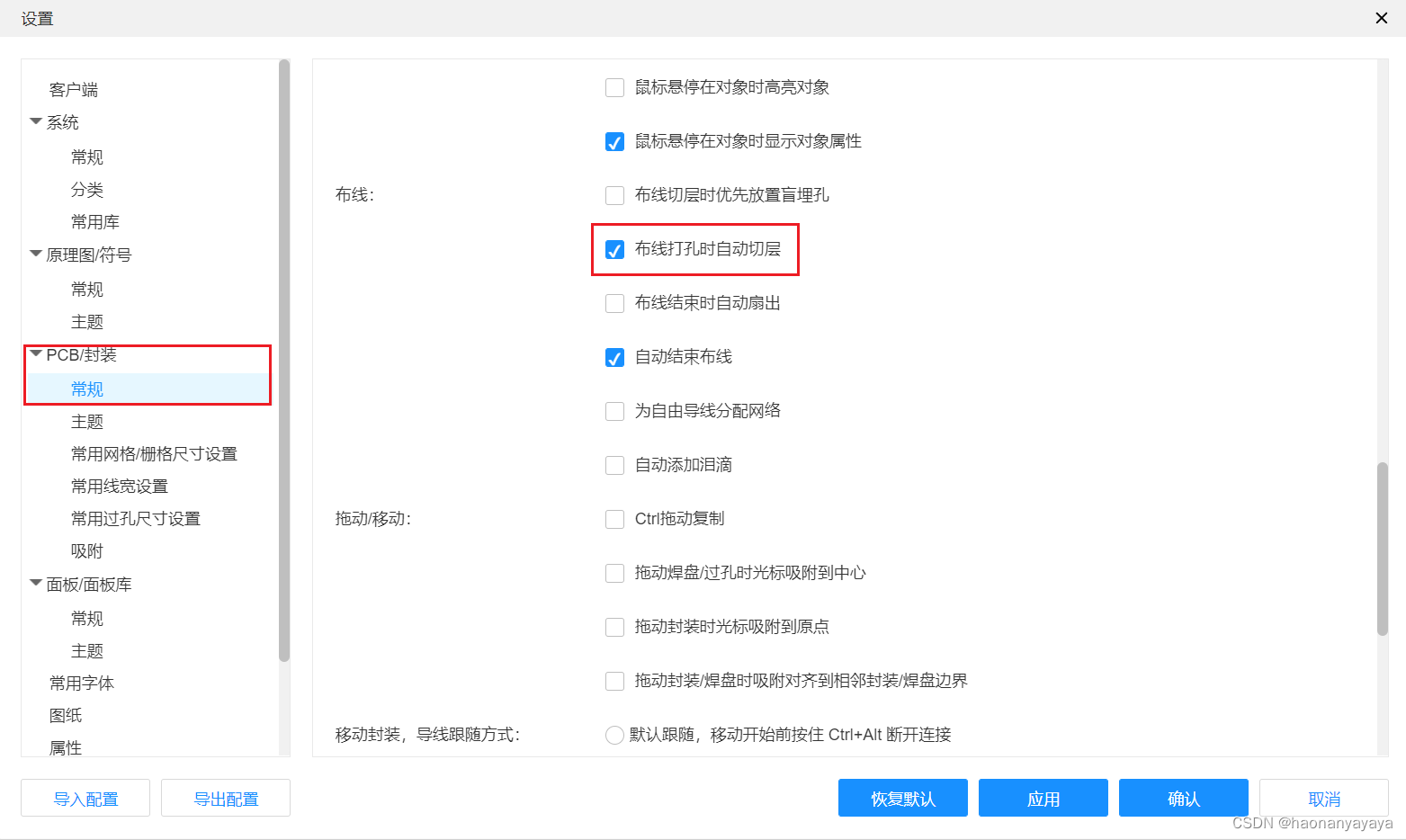

“立创EDA专业版”笔记

目录 二、立创EDA专业版 2.0 整体功能 2.0.1 快捷键 2.1 右侧功能栏 2.1.1 过滤 2.2 PCB设计 2.2.1 切换亮度 2.2.2 偏移 2.2.3 单位切换 2.2.4 检查DRC 2.2.5 重新铺铜 2.2.6 布线 2.2.7 锁定 2.2.8 “过滤”设置锁定 2.3 上方菜单栏 2.3.1 保存文件 2.4 元件库

京存分布式赋能EDA应用

合抱之木,生于毫末;九层之台,起于累土;千里之行,始于足下。——《老子·德经·第六十四章》 EDA(Electronic Design Automation 电子设计自动化)是利用计算机,完成对VLSI (Very Large Scale Integration 超大规模集成电路)的数字化研究、设计、验证等任务。高性能集成电路的设计和制造中,最出名的两个配套工具、设备就是EDA软件和光刻机,除此

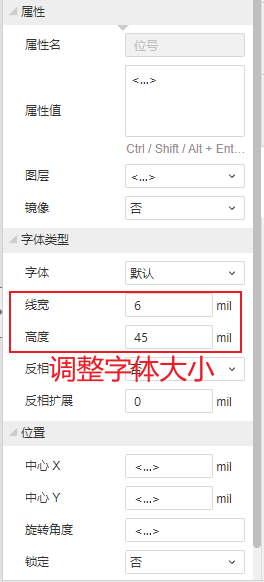

立创EDA专业版设置位号居中并调整字体大小

选择某一个器件位号,右键->查找: 选择查找全部: 下面会显示查找结果: 查看,所有的位号都被选中了: 然后布局->属性位置: 属性位置选择中间: 然后位号就居中了 调整字体大小:元件属性面板

电路笔记 : 嘉立创EDA 导入、查找、设计管理器(快速寻找网络标签)功能+DRC错误检查和处理

导入功能 查找功能 可查找多种类型,如原件名称、网络标签等 设计管理器 图层查看 DRC错误 规则设置 线距问题 大多数PCB制造商能够可靠地生产5 mil间距的走线和间隙。这是一个常见的标准,适合大多数消费级和工业级电子产品。在5 mil以上的间距,制造商可以确保线路的完整性和一致性。 合理的线间距有助于减少信号串扰(cross-talk)和电磁干扰

数字模拟EDA研发环境搭建

中小企业数字模拟EDA研发环境部署、集群搭建、网络配置、硬件咨询、数据备份、技术指导、环境生命周期维护等,Cadence、Synopsys、Mentor、Keysight、ANSYS,MATLAB、Xilinx等厂商软件工具安装调试。 EDA研发环境搭建经验交流,请加V

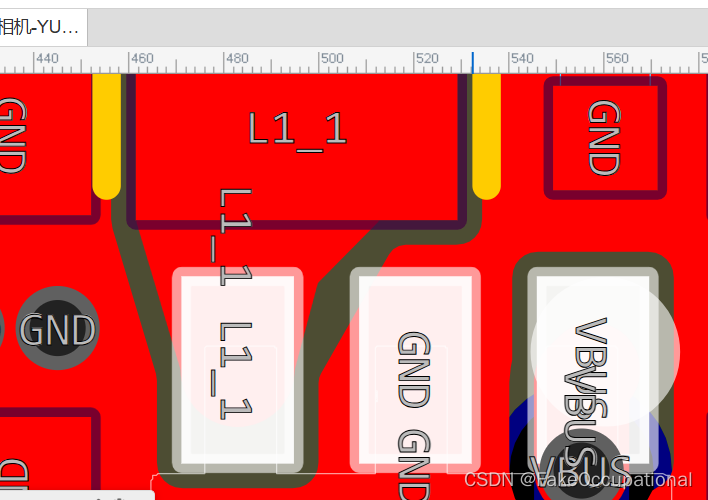

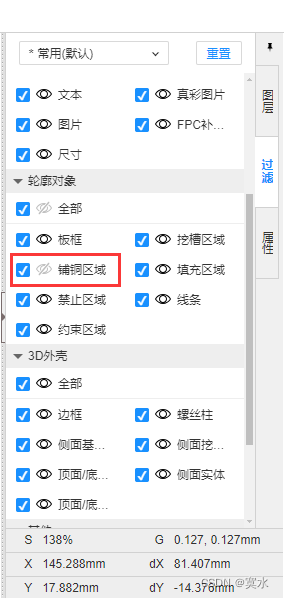

嘉立创EDA隐藏铺铜

在设计PCB时,如果在铺铜后进行部分线路的修改、调试与检查,会比较困难。如果对铺铜进行隐藏后,可极大的方便观察与设计。 嘉立创EDA隐藏铺铜方法如下: 1、打开左侧的过滤选项,在轮廓对象下,关闭铺铜区域选项即可 2、使用快捷键操作 使用Shift+M可以快速切换铺铜的显示与隐藏状态。 同时,在调整完电路后,可通过快捷键Shift+B用所有铺于重建铜区。

Python | 自动探索性数据分析(EDA)库SweetViz

SweetViz是一个开放源代码Python库,主要用于生成精美的高密度可视化文件,启动探索性数据分析(EDA),输出为完全独立的HTML应用程序。 探索性数据分析(EDA)是分析和总结数据集主要特征的过程,通常旨在了解数据中的潜在模式,关系和趋势。 SweetViz库的特点 主要包括以下几个方面: 快速生成可视化图表:通过仅两行代码或更少,SweetViz可以快速生成美观且高密度的可视化

蓝桥杯 EDA 组 历届国赛真题解析

一、2021年国赛真题 1.1 CN3767 太阳能充电电路 CN3767 是具有太阳能电池最大功率点跟踪功能的 4A,12V 铅酸电池充电管理集成电路。 最大功率点应指的是电池板的输出电压,跟踪电压其做保护。当然 CN3767 也可以直接使用直流充电,具体可以阅读芯片手册。 CN3767 其原理是根据 BAT 引脚检测电池电压;BAT 和 CSP 引脚配合 R26 检测电阻

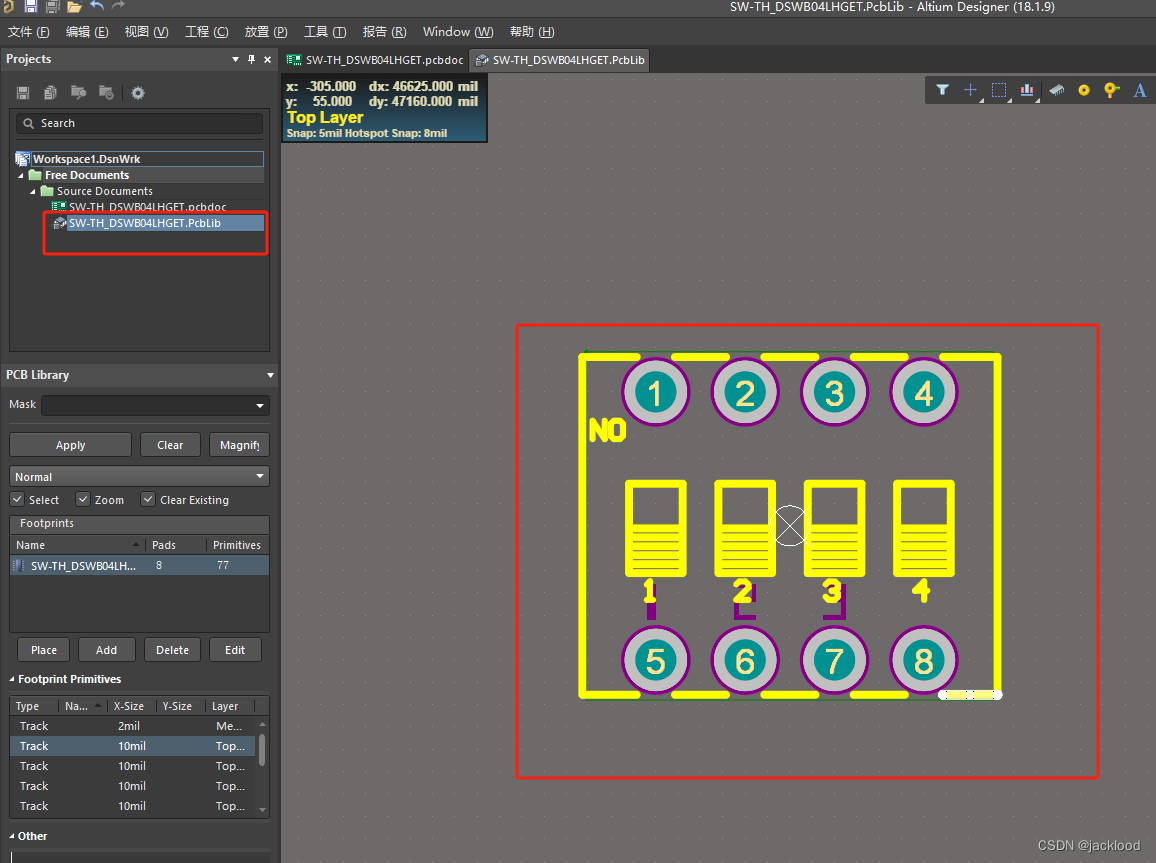

从嘉立创EDA提取PCB封装到Altiumdesigner的步骤

1、以拨码开关为例,再嘉立创EDA的立创商城搜索到拨码开关,如下图: 2、然后点击数据手册,显示出来4位拨码开关的封装图 3、点击立即打开,进入立创EDA编辑界面 4、登录编辑器 5、点击文件,导出Altiumdesigner 6、勾选同意,并导出,放至一个文件夹 7、然后用AD打开这个文件 8、然后在AD点击设计---生成PCB库,即可生成AD使

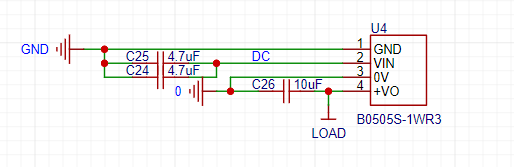

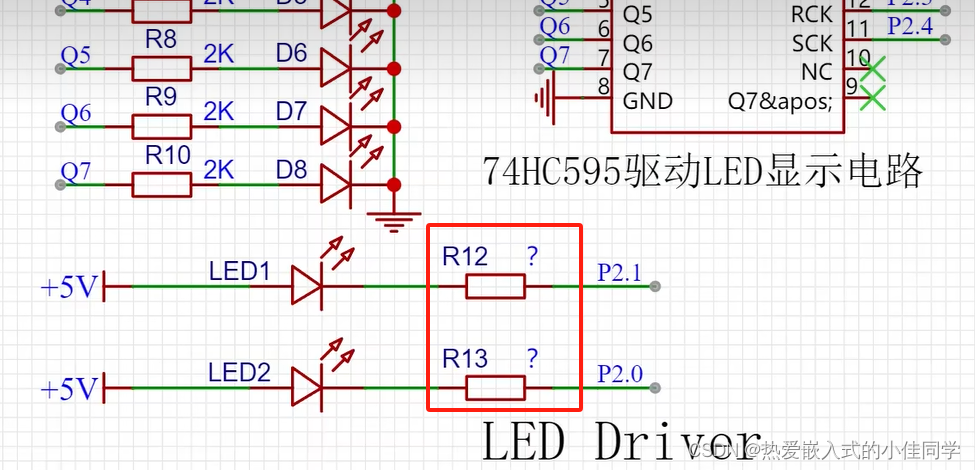

蓝桥杯EDA常见电路原理图设计和分析

目录 前言 一、常见器件及其作用 二、原理图设计题目 1.蜂鸣器原理图 2.LCD背光控制电路 3.参考电压源 4.低通滤波器电路设计 5.5-3.3电源转换电路 6.3.3V-VDD_EXT电平转换电路 7.DS18B20原理图 8.供电输出控制接口电路 9.电源检测接口电路 10.USB转串口电路 三、原理图分析题目 1.计算电阻R5 2.计算电阻R92

关于国产板级EDA软件的一点看法

这两天估计很多朋友都收到了关于一款国产板级EDA软件将要发布的消息,我也顺着相关消息去访问了这家公司的官网: 成都派兹互连电子技术有限公司(“派兹互连”)成立于2023年07月31日,注册资本为2.1亿元。 派兹互连独家收购西门子EDA的PADS Standard和PADS Standard Plus软件的源代码及中国区业务。 派兹互连依托全球主流成熟商用的PADS软件技术和完善庞大的用户生态

EDA(四)布局布线

EDA(四)布局布线 布局布线(Layout and Routing)是电子设计自动化(EDA)领域中的一个重要环节,特别是在集成电路(IC)设计和印刷电路板(PCB)设计中。它涉及到将电路设计中的逻辑门、晶体管、电容器、电阻器等电子元件在物理空间中进行精确的放置(布局),并通过导线(通常称为走线或布线)将它们连接起来,以实现电路的功能。 布局(Layout) 布局是指在芯片或电路板上为电子

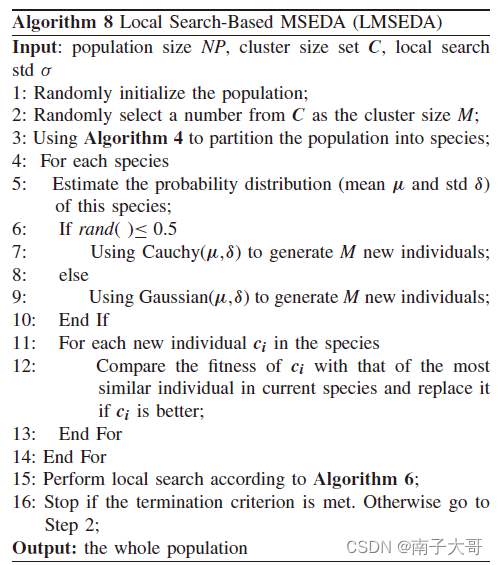

多模态EDA论文小记

论文地址 该论文主要改进点是:通过动态化局部搜索中每个集群大小,高斯和柯西分布共同产生个体。总的来说改进点不多,当然也可能是笔者还没发现。 局部搜索 划分集群 划分集群有两个策略分别是: 随机生成一个点作为中心点,将该点半径r内点划为一个集群选择最优个体作为中心点,将该点半径r内点划为一个集群 下图分别是两种划分方式。 这两个方法对于参数都比较敏感,具体来说就是集群大小参数设置将很

EDA(一)Verilog

EDA(一)Verilog Verilog是一种用于电子系统设计自动化(EDA)的硬件描述语言(HDL),主要用于设计和模拟电子系统,特别是在集成电路(IC)和印刷电路板(PCB)的设计中。Verilog由Philip Moorby和Edward Gelbach在1983年开发,并于1984年首次发布。Verilog HDL的语法类似于C语言,但它提供了用于描述硬件行为和结构的特定构造。 1.

datawhale——EDA

EDA目标 EDA的价值主要在于熟悉数据集,了解数据集,对数据集进行验证来确定所获得数据集可以用于接下来的机器学习或者深度学习使用。当了解了数据集之后我们下一步就是要去了解变量间的相互关系以及变量与预测值之间的存在关系。引导数据科学从业者进行数据处理以及特征工程的步骤,使数据集的结构和特征集让接下来的预测问题更加可靠。完成对于数据的探索性分析,并对于数据进行一些图表或者文字总结并打卡。 这次学

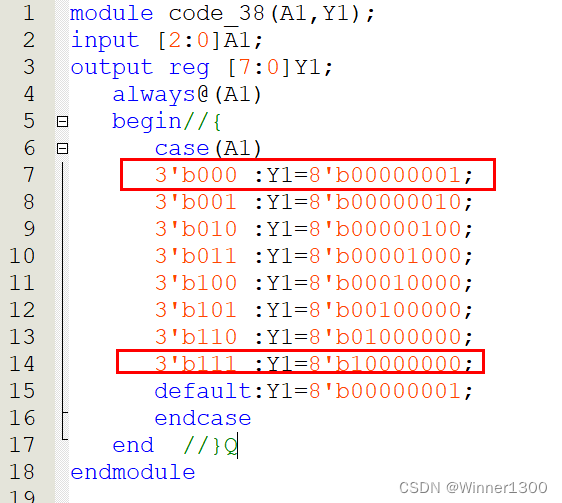

【EP2C35F672C8 EDA试验箱下载 38译码器实现】

文章目录 前言一、实验设备1.实验箱2.下载器: 二、编译工程1.编译工程2.添加tcl引脚配置文件2.1将tcl文件拷贝到工程目录下:2.2 在软件中添加tcl文件 3.tcl文件简答讲解 三、下载四、实验结果总结 前言 提示:这里可以添加本文要记录的大概内容: 课程需要:展示EP2C35F672C8 EDA试验箱 38译码器实验下载验证 提示:以下是本篇文章正文内

3D开发工具HOOPS SDK在电子设计自动化(EDA)中的应用

在当今电子行业中,电子设计自动化(EDA)软件的重要性日益突显。这些软件不仅需要能够处理大量的电子设计数据,而且需要提供高效的设计工作流程、准确的分析模拟功能以及直观的可视化界面。为了满足这些需求,开发者们寻求利用先进的工具和技术来构建领先的EDA软件应用程序。 Tech Soft 3D的HOOPS SDK正是这样一种先进的工具,它为开发者提供了一系列强大的功能,从而帮助他们构建卓越的EDA软件

数据分析案例-中国黄金股票市场的EDA与价格预测

🤵♂️ 个人主页:@艾派森的个人主页 ✍🏻作者简介:Python学习者 🐋 希望大家多多支持,我们一起进步!😄 如果文章对你有帮助的话, 欢迎评论 💬点赞👍🏻 收藏 📂加关注+ 目录 1.项目背景 2.数据集介绍 3.技术工具 4.导入数据 5.数据可视化 6.建模预测 源代码 1.项目背景 在金融市场中,黄金一直被视

EDA软件常用3D库站点

我常用的如下,欢迎评论补充。 http://www.3dcontentcentral.cn/ https://www.snapeda.com/ https://componentsearchengine.com/ga/ https://www.datasheet5.com/ https://grabcad.com/ http://www.3ds.com/ https://www.digikey.

探索性数据分析(EDA)

本篇博客主要介绍的是探索性数据分析以及其Python实现本篇博客内容基于阿里云天池竞赛:心跳信号分类预测写就,着重说明了其探索性数据分析的部分学习交流请联系 obito0401@163.com 文章目录 含义内容载入数据处理以及可视化库载入数据数据总览判断数据缺失和异常了解数据分布情况 含义 探索性数据分析(Exploratory Data Analysis,EDA),是指

【六 (2)机器学习-EDA探索性数据分析模板】

目录 文章导航一、EDA:二、导入类库三、导入数据四、查看数据类型和缺失情况五、确认目标变量和ID六、查看目标变量分布情况七、特征变量按照数据类型分成定量变量和定性变量八、查看定量变量分布情况九、查看定量变量的离散程度十、查看定量变量与目标变量关系十一、查看定性变量分布情况十二、查看定性变量与目标变量关系十三、查看定性变量对目标变量的显著性影响十四、查看定性变量和目标变量的spearman相

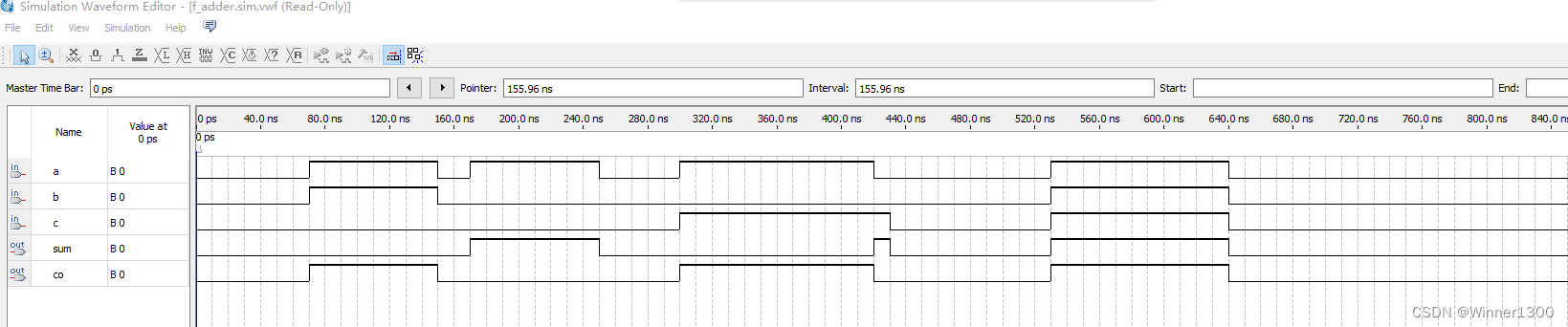

EDA 全加器设计及例化语句应用

文章目录 前言一、全加器是什么?二、使用步骤1.半加器2.全加器1.新建一个全加器工程2.添加半加器的.v文件到全加器工程中3.新建全加器.v文件,写程序,调用半加器.v文件 完成例化 三、仿真效果总结 前言 提示:这里可以添加本文要记录的大概内容: 项目需要: 提示:以下是本篇文章正文内容,下面案例可供参考 一、全加器是什么? 示例: 二、使用步骤 1.半

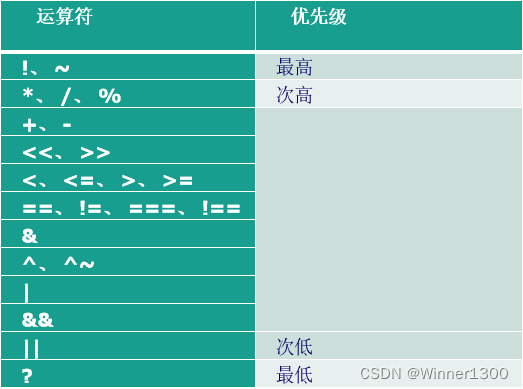

【EDA verilog 基础语法】

文章目录 前言一、逻辑值二、数字进制格式三、标识符四、数据类型1.寄存器类型:2.线网类型:3. 参数类型: 五、运算符1.算术运算符2.逻辑运算符3.条件运算符4.位运算符:5.移位运算符6.拼接运算符:7.运算符的优先级: 总结 前言 提示:这里可以添加本文要记录的大概内容: 课程需要: 提示:以下是本篇文章正文内容,下面案例可供参考 一、逻辑值 逻辑 0:表

EDA - s家的dc_shell-t read缓冲区大小不同引起的问题

EDA - s家的dc_shell-t read缓冲区大小不同引起的问题 问题描述 在CentOS 7上执行dc_shell-t -topo -64bit进入shell后,source /path/to/tcl.tl,还在source的过程中使用另一台服务器执行svn up /path/to/tcl.tl,接着该source过程就报错退出。而在CentOS 6上该flow是能正常完成的。 问