逻辑电路专题

怎么判断同步时序逻辑电路和异步时序逻辑电路?

🏆本文收录于「Bug调优」专栏,主要记录项目实战过程中的Bug之前因后果及提供真实有效的解决方案,希望能够助你一臂之力,帮你早日登顶实现财富自由🚀;同时,欢迎大家关注&&收藏&&订阅!持续更新中,up!up!up!! 问题描述 这个电路是异步逻辑电路还是同步逻辑电路啊,判断依据是什么啊,可以列出他的状态图,激励图,激励方程和时钟方程吗 如上问题有来自我自身项目开发,有

logism数电实验二 (组合逻辑电路设计)运动码表

因为看得人好像蛮多,作为一名负责的博主(bushi,所以就把文章补充了一下,现在过程应该是比较清晰了。 电路文件已经托管至Github,欢迎star:点这里 一、组件_二路选择器(16位) 使用真值表得到一位二路选择器 注意要得到下图所示的电路需要在Analysis circuit中简化一下 叠加得到十六位的二路选择器 测试通过 二、组件_16位并行加载寄存器 对我这种菜鸡来说,mooc

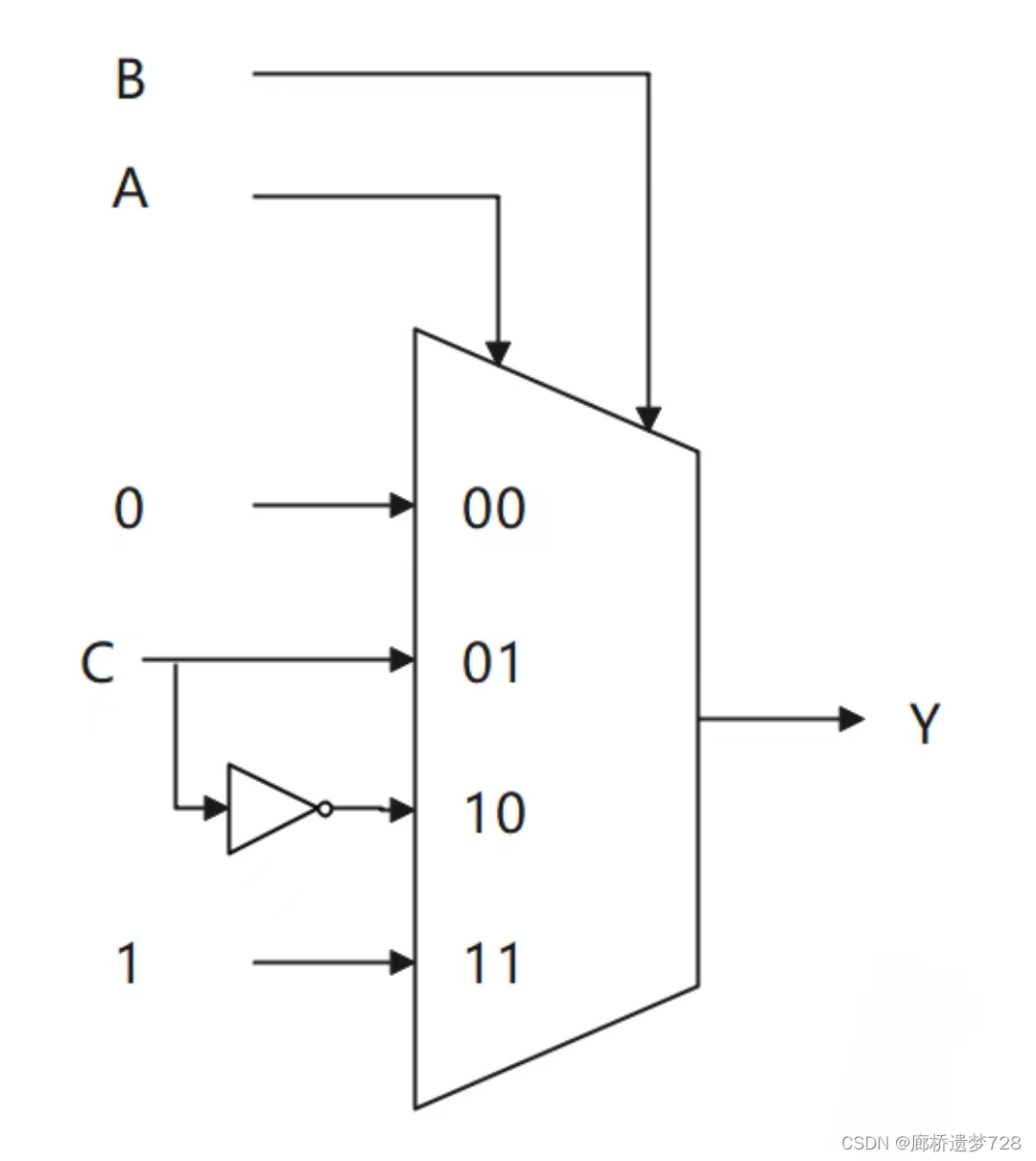

常用组合逻辑电路模块(3):数据选择器

数据选择器概述 数据选择:指经过选择,将多路数据中的某一路数据传到公共数据线上。(相当于多个输入的单刀多掷开关) 数据选择器:能实现数据选择功能的逻辑电路。也称多路选择器或多路开关。如下图为4选1数据选择器: 对于4选1数据选择器,最常见的芯片为74LS153,其内部有两个4选1数据选择器。 工作原理:给A1、A0一组信号,比如10,就相当于给了一个二进制数字2,也就相当于选通了D2这

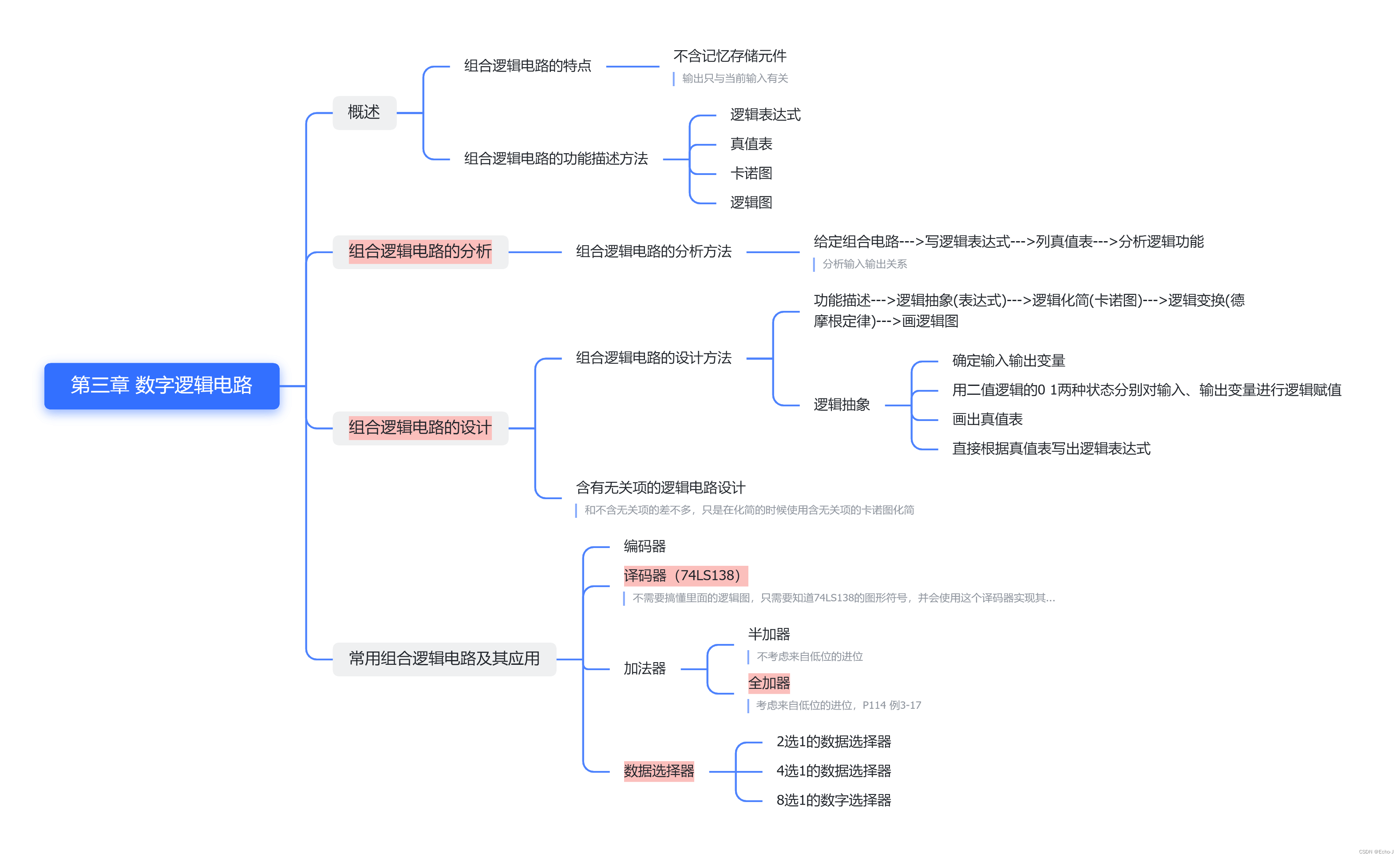

数字逻辑-组合逻辑电路二——沐雨先生

一、实验目的 (1)掌握数据选择器和译码器的功能。 (2)用数据选择器实验逻辑函数。 (3)用译码器实现逻辑函数。 二、实验仪器及材料 三、实验原理 (一)74LS151 74LS151是常用的8选1数据选择器,芯片内部有一个8选1数据选择器。通过输入不同的地址码C、B、A,可以控制输出Y选择8个输入数据D0~D7中的一个。 连线图和逻辑功能表如下图所示。 S为使能端; C、B、

组合逻辑电路(二)(译码器和编码器)

目录 译码器 简单逻辑门译码器 二进制译码器 2线-4线译码器 3线-8线译码器 二-十进制译码器 4线-10线译码器 七段显示译码器 编码器 二进制普通编码器 二-十进制普通编码器(8421BCD码编码器) 优先编码器(Priority Encoder) 译码器 将输入的代码译为特定对象(如逻辑电平),用于检测特定数字状态的组合逻辑电路 译码 利用译码表将具有特定含义的文字

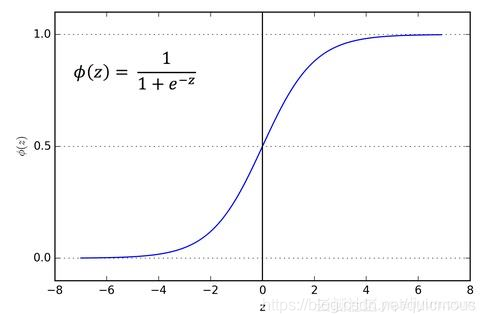

神经网络和逻辑电路——表面相同的设计形式,天壤之别的设计思想

1. 神经网络与逻辑电路相似的表面形式 第一次看到神经网络这个理论的时候,首先呢,这个我脑子里边儿闪出的第一个念头就是它,它可能和我们传统的逻辑电路非常相似。 逻辑电路里边我们处理的数据,就是0、1两个数字.那么在神经网络里边呢,由于Sigmoid函数的存在,我们所处理的数据啊,是0到1之间的实数。所以从这个角度来讲的话,我想神经网络,它很可能是逻辑电路的一个推广,把0、1两个值推广到[0,1

专145+总420+哈尔滨工业大学803信号与系统和数字逻辑电路考研经验哈工大电子信息与通信,真题,大纲,参考书。

自从高考失利没有考入哈工大,一直带着遗憾,今年初试专业课803信号与系统和数字逻辑电路145+,总分420+顺利圆满哈工大,了却了一块心病,回看这一年的复习起起落落,心中的那块初心,让我坚持到了上岸,总结一下自己的复习经验,希望对大家复习有帮助。 专业课:(145+,很遗憾没有拿到满分,信息通信Jenny老师一再鼓励和以满分为要求,也让我对自己有了更高的要求,求上得中,最后专业课分数

《数电》理论笔记-第3章-常用组合逻辑电路及MSI组合电路模块的应用

一,编码器和译码器 1,编码器 编码:用由0和1组成的代码表示不同的事物。 编码器:实现编码功能的电路, 常见编码器:普通编码器、优先编码器、二进制编码器二-十进制编码器等等 1.1 三位二进制普通编码器和三位二进制优先编码器 1分58秒开始 1.2 8421BCD普通编码器和8421BCD优先编码器 0-8分钟 1.3 MSI74148优先编码器及应用 高电平有效在实际电

数字电路之如雷贯耳的“逻辑电路”

博主福利:100G+电子设计学习资源包! http://mp.weixin.qq.com/mp/homepage?__biz=MzU3OTczMzk5Mg==&hid=7&sn=ad5d5d0f15df84f4a92ebf72f88d4ee8&scene=18#wechat_redirect ----------------------------------------------------

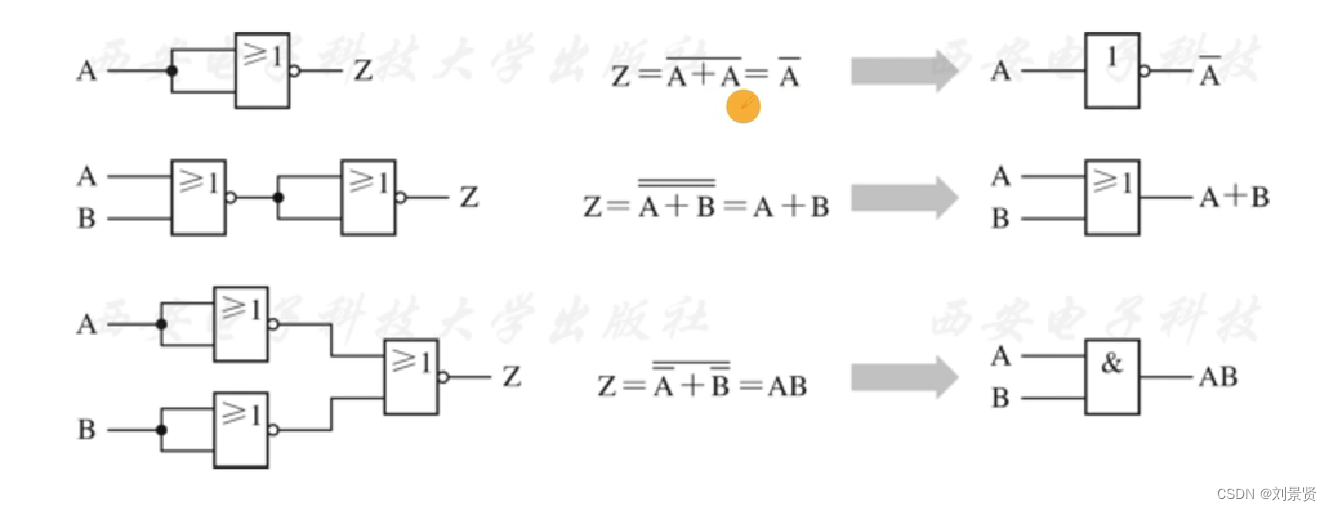

《数电》理论笔记-第2章-组合逻辑电路

一,集成门电路 1TTL门电路 TTL门电路中双极型三极管构成,它的特点是速度快、抗静电能力强集成度低、功耗大, 目前广泛应用于中、小规模集成电路中。 TTL门电路有 74 (商用) 和 54 (军用) 两大系列,每个系列中又有若干子系列。 2 CMOS门电路 CMOS门电路由场效应管构成。 特点:集成度高、功耗低、速度慢、抗静电能力差。 目前已可与TTL门电路相媲美。因此,CMO

Verilog HDL语言组合逻辑电路设计实列

Verilog DHL语言组合逻辑举列 内容8位带进位端的加法器的设计指令译码电路设计比较重组信号设计比较器设计3-8译码器设计 内容 8位带进位端的加法器的设计 实现模块: module adder_8(cout,sum,a,b,cin);input cin;input[7:0] a,b;output cout;output[7:0] sum;assign {cout,s

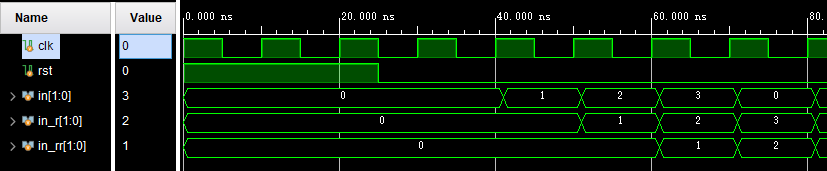

为什么时序逻辑电路会落后一拍?

1、时序逻辑电路落后一拍? FPGA初学者可能经常听到一句话:“时序逻辑电路,或者说用 <= 输出的电路会延迟(落后)一个时钟周期。”但在仿真过程中经常会发现不符合这一“定律”的现象–明明是在仿真时序逻辑,怎么输出不会落后一拍? 先来看一个简单的例子:把输入信号用时序逻辑电路寄存两次,即俗称的“打两拍”。Verilog代码如下: module test( input clk, //

硬件基础:组合逻辑电路

什么是组合逻辑电路 组合逻辑电路是由一些基本的逻辑门电路组成的,没有反馈,输出仅取决于输入。 组合逻辑电路是数字逻辑电路中一种重要的电路类型,它是由多个逻辑门(例如与门、或门、非门等)组成的电路。组合逻辑电路根据输入信号的状态,在不需要时钟脉冲的情况下直接产生输出。 因此,组合逻辑电路可以看成纯粹的布尔运算器。 组合逻辑电路有以下特点: (1)只由逻辑门和电线构成,没有存储器件; (2)输出仅

专业130+总400+哈尔滨工业大学803信号与系统和数字逻辑电路考研经验哈工大,电子信息,信息与通信工程,信通

今年专业课803信号与系统和数字逻辑130+总分400+如愿考上哈尔滨工业大学电子信息(信息与通信工程-信通),总结了一些各门课程复习心得,希望对大家复习有帮助。 数学一 资料选择: ①高数:张宇强化班 ②线性代数:李永乐强化 ③概率论:王式安强化+张宇强化 上面说的都是视频,下面说纸质资料。李永乐复习全书强化版、李永乐660题;张宇高数18讲、概率论9讲、1000题;历年真题;模

【Verilog】期末复习——VerilogHDL描述数字逻辑电路的建模方式有哪三种?它们的特点是?

系列文章 数值(整数,实数,字符串)与数据类型(wire、reg、mem、parameter) 运算符 数据流建模 行为级建模 结构化建模 组合电路的设计和时序电路的设计 有限状态机的定义和分类 期末复习——数字逻辑电路分为哪两类?它们各自的特点是什么? 系列文章VerilogHDL描述数字逻辑电路的建模方式有哪三种?它们的特点是? VerilogHDL描述数字逻辑

数字逻辑电路入门:从晶体管到逻辑门

数字逻辑电路入门:从晶体管到逻辑门 这是数字逻辑电路中最基础的部分。但是并非那么容易理解。 1、晶体管 mosfet:场效应晶体管,是电压控制元件。cmos:是指由mos管构成的门级电路通常是互补的。BJT:一种三极管,是电流控制元件,用来放大电流,功耗大于mos管。nmos:衬底是p型半导体,源极和漏极是n型掺杂区域。适合用来导通低电压,不适合导通高电压。pmos:和nmos相反,衬底是n

Verilog描述——时序逻辑电路浅析

时序逻辑电路浅析 时序电路时状态依赖的,所以又称为状态机。这里只限于讨论有限数量的存储单元构成的状态机,因而其状态数是有限的,称为有限状态机FSM(Finite State Machine)。 时序逻辑电路具有以下主要特征: 时序逻辑电路由组合电路和存储电路组成;时序逻辑电路的状态与时间因素有关,即时序电路在任一时刻的状态变量不仅是当前输入信号的函数,而且还是电路以前状态的函数,时序电路的输

Verilog描述——组合逻辑电路浅析

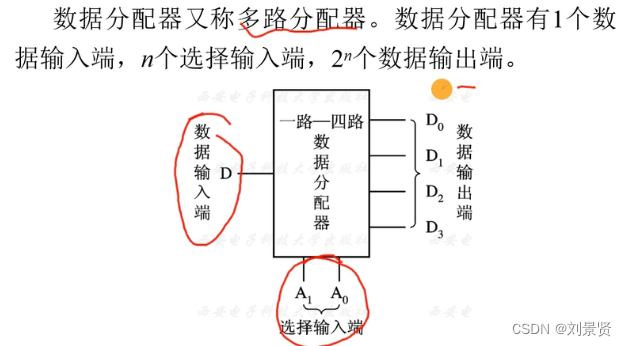

组合逻辑电路浅析 由于某些原因,又重新看是看了本科的教材——《电子技术基础数字部分》,经过两年半的工作,再次看到上面的内容,感觉到自己的基础环节着实薄弱,所以,就从书上找些基础内容,学习记录下来; 组合逻辑电路 原来,典型的一些中规模集成电路,都是属于组合逻辑电路,比如:编码器,数据选择器,数据分配器,数值比较器,算数逻辑运算单元等。 组合电路的结构具有如下特点: 输出、输入之间没有反馈

12.12进制(原反补码,运算,进制转换),卡诺图化简,组合逻辑电路(竞争冒险,分析、设计方法),杂项

逻辑代数的基本定理和规则是用来处理逻辑函数的,其中包括以下几个重要的定理和规则: 1. 与门的性质: - 同一律:A∧A=A - 零律:A∧0=0 - 一律:A∧1=A 2. 或门的性质: - 同一律:A∨A=A - 零律:A∨0=A - 一律:A∨1=1 3. 非门的性质: - 否定律:¬(¬A)=A 4. 交换律: - 与门交换律:A∧B=B∧A - 或门交换律:A∨B=B∨A

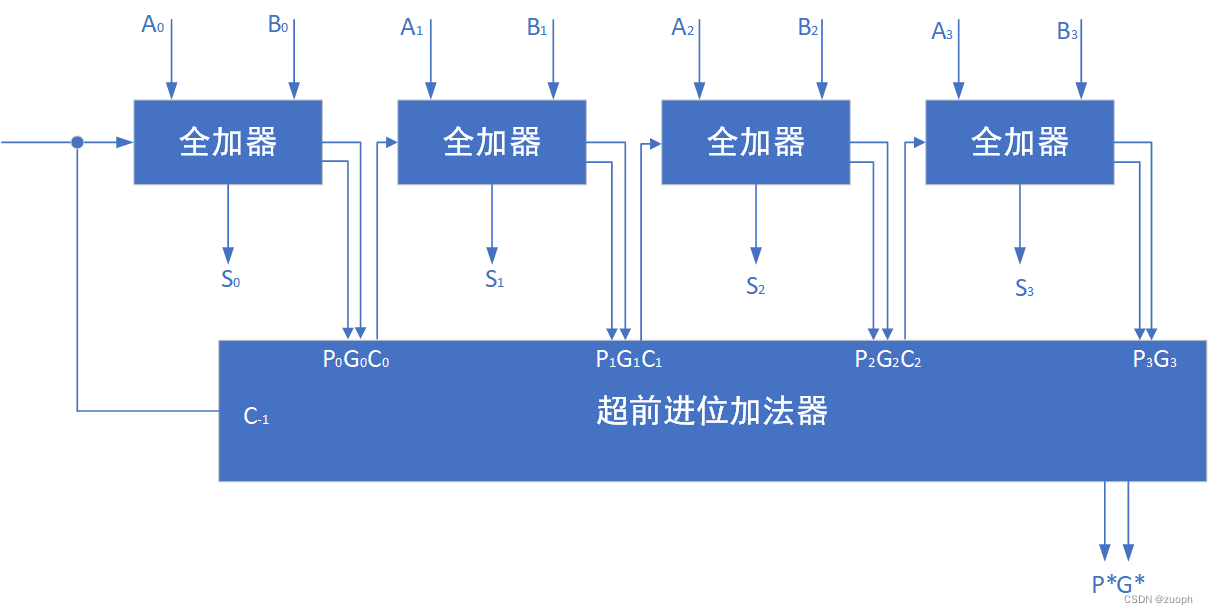

数字逻辑电路基础-组合逻辑电路之4位先行进位加法器

文章目录 一、问题描述二、verilog源码三、仿真结果 一、问题描述 前面介绍4位行波进位全加器(串行加法器)的原理及verilog实现,但是它是一种串行加法器,当位数多时,比如32位的二进制数相加,由于进位逐位从低位向高位传递,这会造成相当大的延迟。对于需要快速加法运算的信号处理电路来说,我们需要对其进行改进,一个常见的想法就是将进位提前计算出来,这样我们可以实现一种称

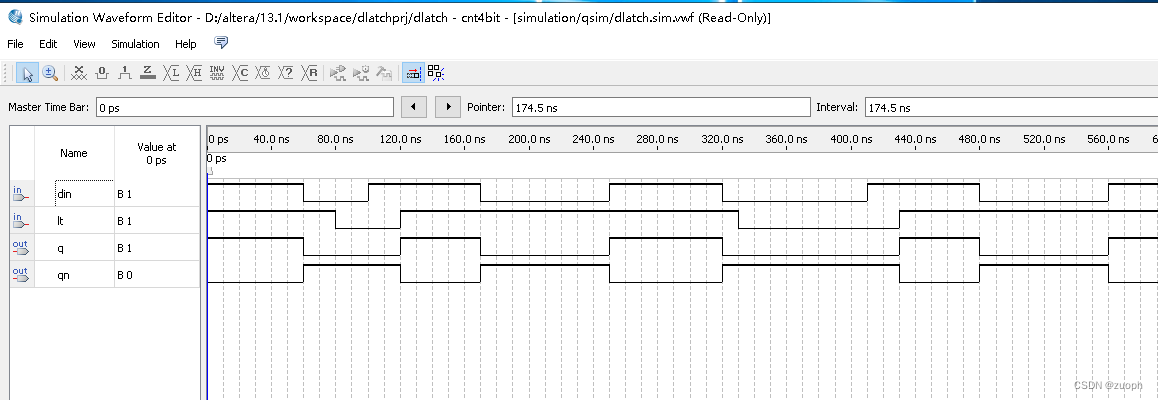

数字逻辑电路基础-时序逻辑电路之锁存器

文章目录 一、锁存器简介二、verilog源码三、综合及仿真结果 一、锁存器简介 本文介绍数字逻辑电路中一种常用的基础时序逻辑电路-锁存,顾名思义,它的功能就是将输入在控制信号有效时透明传输到输出端,当控制信号无效时,输出值保持不变。它具有记忆和存储功能。这是它区别组合逻辑的基本点。 下图是锁存器的门级结构图。它由两个与非门、一个反相器及后级的RS锁存器构成。 锁存器

数字逻辑电路基础-时序逻辑电路之锁存器

文章目录 一、锁存器简介二、verilog源码三、综合及仿真结果 一、锁存器简介 本文介绍数字逻辑电路中一种常用的基础时序逻辑电路-锁存,顾名思义,它的功能就是将输入在控制信号有效时透明传输到输出端,当控制信号无效时,输出值保持不变。它具有记忆和存储功能。这是它区别组合逻辑的基本点。 下图是锁存器的门级结构图。它由两个与非门、一个反相器及后级的RS锁存器构成。 锁存器

怎样看电路图-电路图中的数字逻辑电路

http://www.56dz.com/Article/dzrm/jczs/200801/312.html 数字电子电路中的后起之秀是数字逻辑电路。把它叫做数字电路是因为电路中传递的虽然也是脉冲,但这些脉冲是用来表示二进制数码的,例如用高电平表示“ 1 ”,低电平表示“ 0 ”。声音图像文字等信息经过数字化处理后变成了一串串电脉冲,它们被称为数字信号。能处理数字信号的电路就称为数字

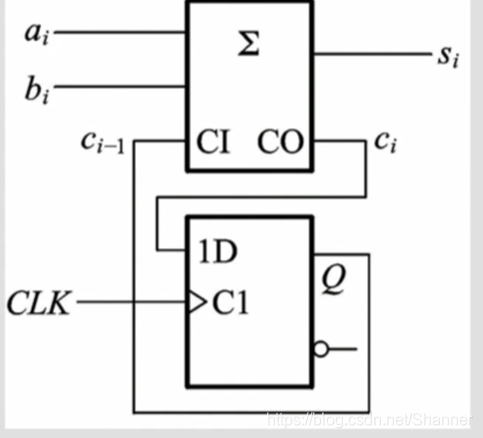

数字电路6-时序逻辑电路

时序逻辑电路 简介时序电路的分析方法 简介 以上是一个串行加法电路。 时序逻辑电路包括组合逻辑电路和存储电路连部分组成。 时序电路的分析方法 1、分析驱动方程 有多少触发器就有多少触发方程 2.状态方程 将驱动方程代入触发器的特性方程中,得到电路的状态方程 3.输出方程