相关文章

数字电路专题:verilog 阻塞赋值和非阻塞赋值

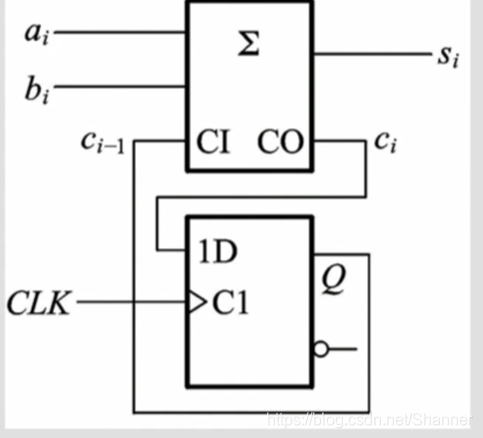

verilog 阻塞赋值 和 非阻塞赋值 “=”阻塞赋值, ”<=”非阻塞赋值。阻塞赋值为执行完一条赋值语句,再执行下一条,可理解为顺序执行,而且赋值是立即执行; 非阻塞赋值可理解为并行执行,不考虑顺序,在 always 块语句执行完成后,才进行赋值。 如下面的阻塞赋值: //代码如下:module top(din,a,b,c,clk);input din;input clk;out

多维时序 | Matlab基于SSA-SVR麻雀算法优化支持向量机的数据多变量时间序列预测

多维时序 | Matlab基于SSA-SVR麻雀算法优化支持向量机的数据多变量时间序列预测 目录 多维时序 | Matlab基于SSA-SVR麻雀算法优化支持向量机的数据多变量时间序列预测效果一览基本介绍程序设计参考资料 效果一览 基本介绍 1.Matlab基于SSA-SVR麻雀算法优化支持向量机的数据多变量时间序列预测(完整源码和数据) 2.SS

时序预测|变分模态分解-双向时域卷积-双向门控单元-注意力机制多变量时间序列预测VMD-BiTCN-BiGRU-Attention

时序预测|变分模态分解-双向时域卷积-双向门控单元-注意力机制多变量时间序列预测VMD-BiTCN-BiGRU-Attention 文章目录 一、基本原理1. 变分模态分解(VMD)2. 双向时域卷积(BiTCN)3. 双向门控单元(BiGRU)4. 注意力机制(Attention)总结流程 二、实验结果三、核心代码四、代码获取五、总结 时序预测|变分模态分解-双向时域卷积

(176)时序收敛--->(26)时序收敛二六

1 目录 (a)FPGA简介 (b)Verilog简介 (c)时钟简介 (d)时序收敛二六 (e)结束 1 FPGA简介 (a)FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了

基于 BiLSTM+Attention 实现降雨预测多变量时序分类——明日是否降雨

前言 系列专栏:【深度学习:算法项目实战】✨︎ 涉及医疗健康、财经金融、商业零售、食品饮料、运动健身、交通运输、环境科学、社交媒体以及文本和图像处理等诸多领域,讨论了各种复杂的深度神经网络思想,如卷积神经网络、循环神经网络、生成对抗网络、门控循环单元、长短期记忆、自然语言处理、深度强化学习、大型语言模型和迁移学习。 降雨预测作为气象学和水文学领域的重要研究课题,对于农业、城市规划、

(175)时序收敛--->(25)时序收敛二五

1 目录 (a)FPGA简介 (b)Verilog简介 (c)时钟简介 (d)时序收敛二五 (e)结束 1 FPGA简介 (a)FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了

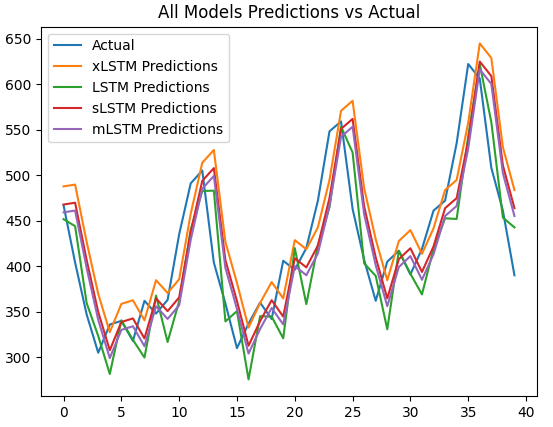

【Python时序预测系列】高创新模型:基于xlstm模型实现单变量时间序列预测(案例+源码)

这是我的第351篇原创文章。 一、引言 LSTM在1990年代被提出,用以解决循环神经网络(RNN)的梯度消失问题。LSTM在多种领域取得了成功,但随着Transformer技术的出现,其地位受到了挑战。如果将LSTM扩展到数十亿参数,并利用现代大型语言模型(LLM)的技术,同时克服LSTM的已知限制,我们能在语言建模上走多远? 论文介绍了两种新的LSTM变体:sLSTM(具有标量记忆和

STM32—I2C的基本时序,MU6050的ID读取

目录 前言 一、I2C基本时序的书写 二、I2C基本时序的代码 1.引脚的初始化 2.起始时序 3.停止时序 4.发送一个字节 5.接收一个字节 6.发送一个应答 7.接收一个应答 三.MU6050的应答 1.先验证下应答功能: 2.读取ID 总结 前言 环境: 芯片:STM32F103C8T6 Keil:V5.24.2.0 模块:MU6050

时序数据库 IoTDB 为什么选择 TPCx-IoT 基准测评?

IoTDB 在 TPCx-IoT 榜单的 What 与 Why 解答! 去年,我们发布了 IoTDB 多项性能表现位居国际数据库性能测试排行榜 benchANT(Time Series: DevOps)第一名的好消息。 刚刚落幕的数据库顶级会议 VLDB 上,我们又收获了一则重磅喜讯:IoTDB 原厂团队基于 Apache IoTDB 开发的企业级产品 TimechoDB 成功打破世界纪录,登