本文主要是介绍logism数电实验二 (组合逻辑电路设计)运动码表,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

因为看得人好像蛮多,作为一名负责的博主(bushi,所以就把文章补充了一下,现在过程应该是比较清晰了。

电路文件已经托管至Github,欢迎star:点这里

一、组件_二路选择器(16位)

使用真值表得到一位二路选择器

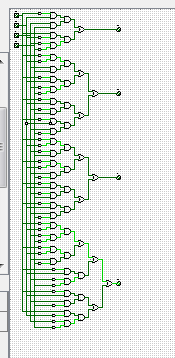

注意要得到下图所示的电路需要在Analysis circuit中简化一下

叠加得到十六位的二路选择器

测试通过

二、组件_16位并行加载寄存器

对我这种菜鸡来说,mooc上讲得不清楚(Q<=Din你说这谁懂啊!),实际上功能是当En为1时,输出数据,当En为0时,保持上次输入的数据。

需要用到:二路选择器、D触发器

先设计四位并行加载寄存器:

(连得不好看,见谅见谅)

然后级联即可

三、组件_BCD计数器

根据数电课程,设计一个同步时序逻辑电路要经过以下步骤:

- 根据逻辑功能要求,建立原始状态表

- 简化原始状态表,消去多余状态

- 状态分配或者状态编码

- 选择触发器类型,求出驱动方程、输出方程

- 检查自启动

- 画出逻辑图

得出状态转换

输出函数:

同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。

异步复位:它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

码表计数器级联即可。

RS、JK、D、T触发器,未使能时都保持原值。

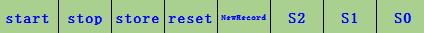

四、运动码表

我一直还在疑惑为什么有八个状态,其实s0、s1、s2被设计为用来表示当前状态,也就是说输入一栏为空。

这样我们就可以设计自己的状态转换机了。

比如:

| 状态 | 数字 |

|---|---|

| 显示 | 001 |

| 存储 | 010 |

| 计数 | 011 |

| 清零 | 100 |

| 暂停 | 101 |

| 复位 | 110 |

然后自定义一个转换规则

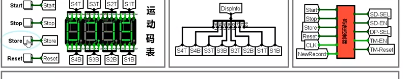

设计好逻辑图并自动生成电路后,连线如下所示:

测试:

因为笔者没上过数电课,所以失误在所难免,有问题可以留言

后续可能会有谭老师的组原实验更新(毕竟书已经买了==),有兴趣的关注一下吧!

这篇关于logism数电实验二 (组合逻辑电路设计)运动码表的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!