本文主要是介绍《数电》理论笔记-第3章-常用组合逻辑电路及MSI组合电路模块的应用,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一,编码器和译码器

1,编码器

编码:用由0和1组成的代码表示不同的事物。

编码器:实现编码功能的电路,

常见编码器:普通编码器、优先编码器、二进制编码器二-十进制编码器等等

1.1 三位二进制普通编码器和三位二进制优先编码器

1分58秒开始

1.2 8421BCD普通编码器和8421BCD优先编码器

0-8分钟

1.3 MSI74148优先编码器及应用

高电平有效在实际电路中的意义是:

不加高电平为低电平,加上高电平为高电平。在电路中传递的是高电平信号。

低电平有效在实际电路中的意义是:

不加低电平为高电平,加上低电平为低电平。在电路中传递的是低电平信号。

2,译码器

译码:编码的逆过程,将二进制代码所表示的相应信号或对象“翻译”出来。

译码器:具有译码功能的电路,

常见译码器:二进制译码器、二-十进制译码器和显示译码器等。

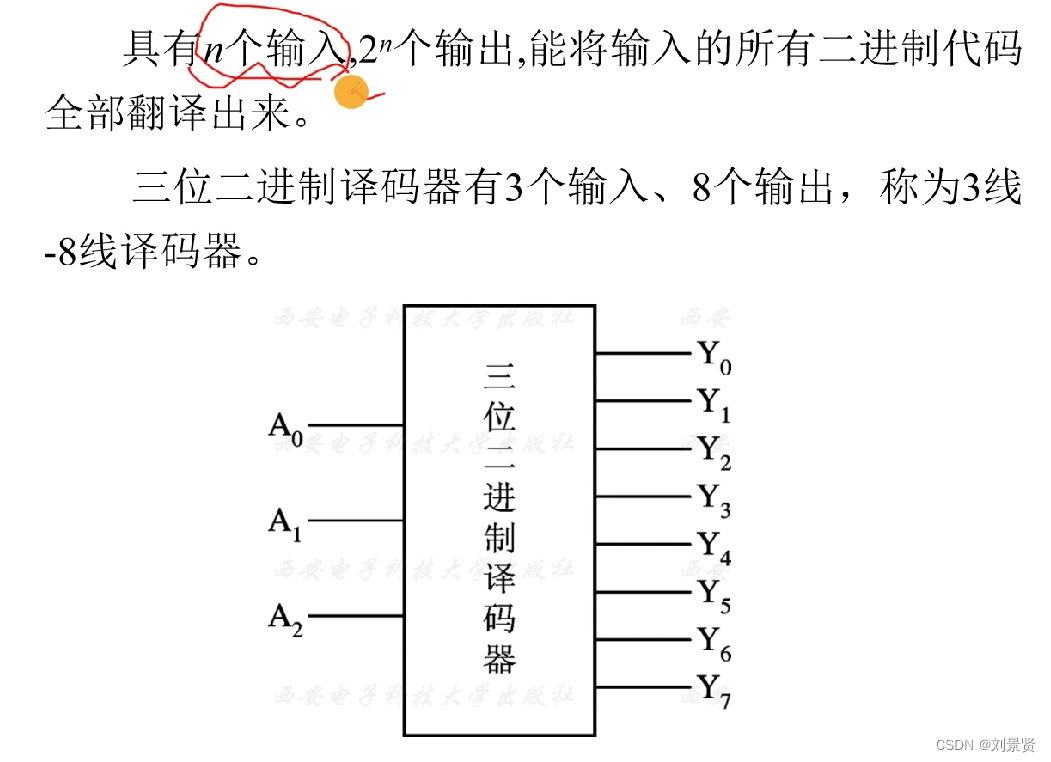

2.1 二进制译码器(3(线)8(线)译码器)

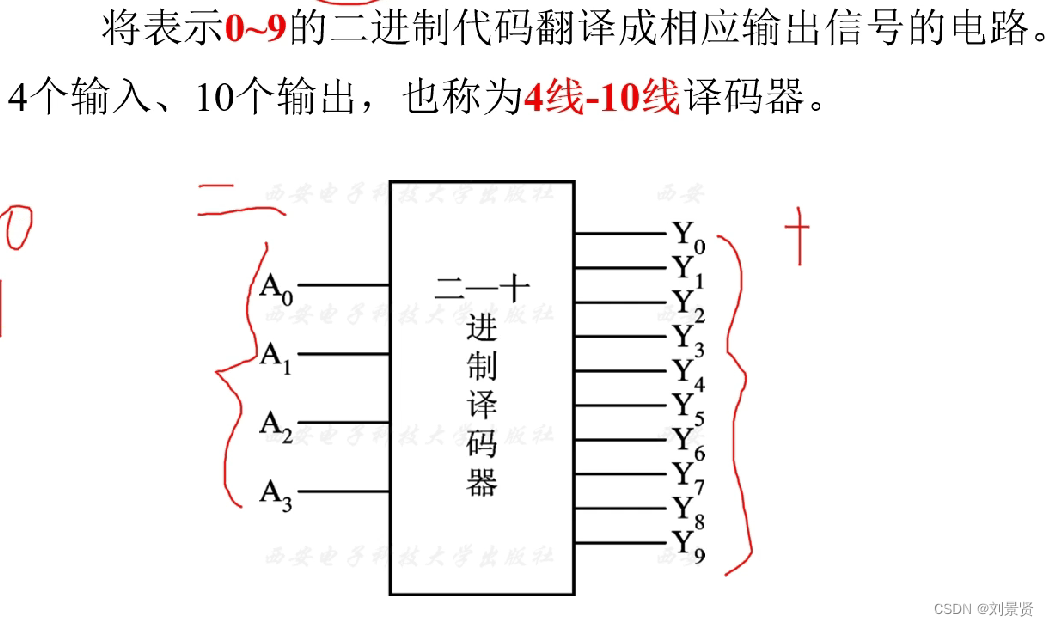

2.2 二-十进制译码器

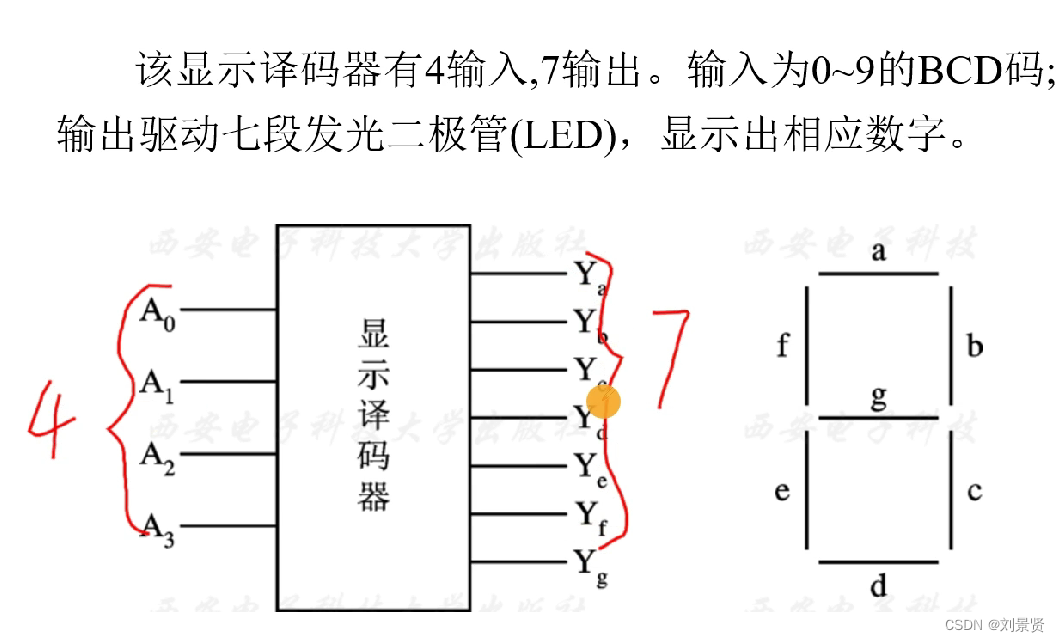

2.3显示译码器

将数字、文字、符号的二进制代码翻译成人们能看懂的形式,直观地显示出来。

把二进制代码翻译出来供显示器件显示的电路称为显示译码器。

常用显示器件:半导体显示器件和液晶显示器件都可用TTL和CMOS电路直接驱动。

BCD-七段显示译码器是一种常用的显示译码器。

BCD-七段显示译码器

2.4 MSI74138译码器

具体11.40到17.00

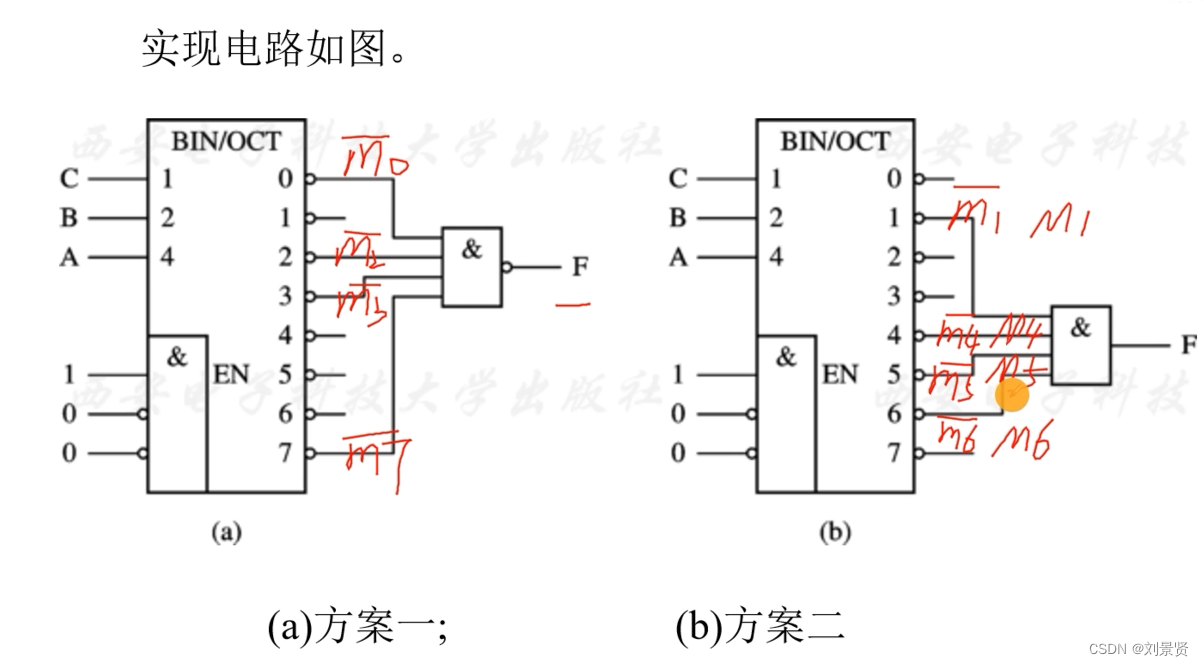

2.5 用MSI译码器实现组合逻辑函数

任一组合逻辑函数均可写成最小项之和的形式(标准与或表达式),

也可以写成最大项之积的形式(标准或与表达式)

二进制译码器的输出提供了其输入变量所有的最小项(或最小项的反-最大项),

因此,可利用译码器实现组合逻辑函数。

步骤

(1)根据译码器输出特点(最小项或最大项),将要实现的逻辑函数转换成相应形式。

(2)将输出端信号进行相或或相与。

例子

二,加法器和比较器

1,加法器

实现两个二进制数相加的电路。

分类:一位加法器和多位加法器。

1.1 一位加法器

实现两个之位二进制数相加的电路。

一位加法器 分为 半加器和全加器。

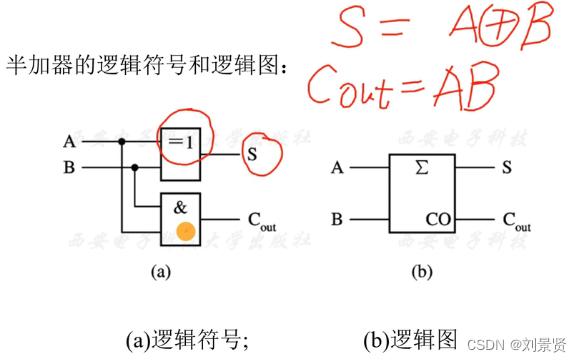

1.1.2 半加器

只考虑本位两个一位二进制数A和B相加,不考虑低位进位,称为半加.

实现半加功能的电路称为半加器。

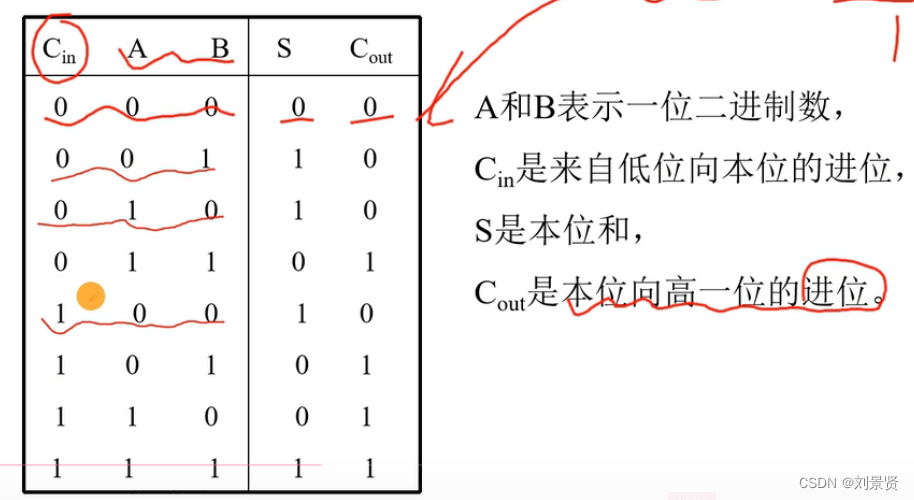

1.1.3全加器

将本位两个一位二进制数和来自低位的进位相加,叫做全加,具有全加功能的电路称为全加器。

1.2 多位加法器

实现两个多位二进制数相加的电路。

根据电路结构不同,分为:串行进位加法器和超前进位加法器。

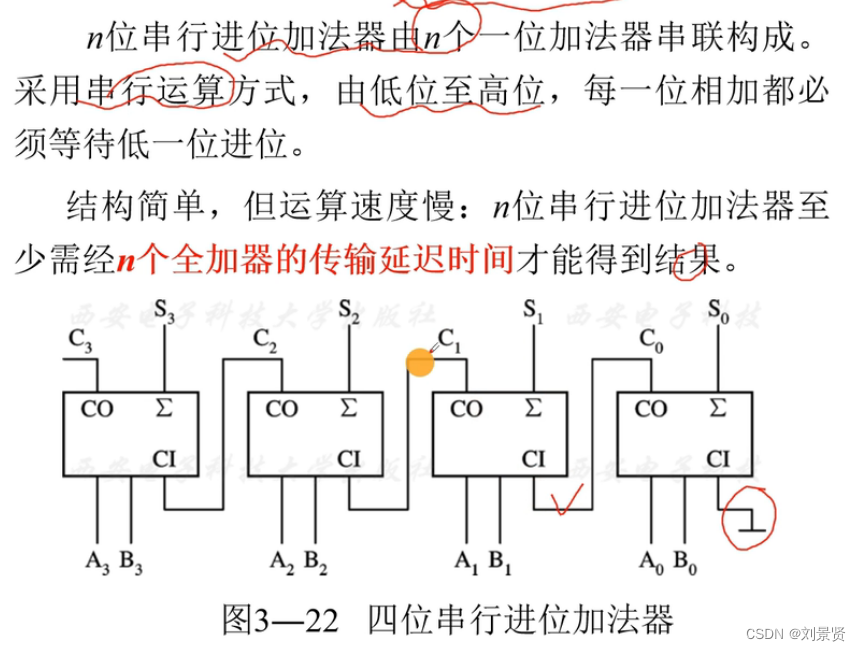

1.2.1串行进位加法器(行波进位加法器)

1.2.2 超前进位加法器

MSI74283加法器及应用例题

略

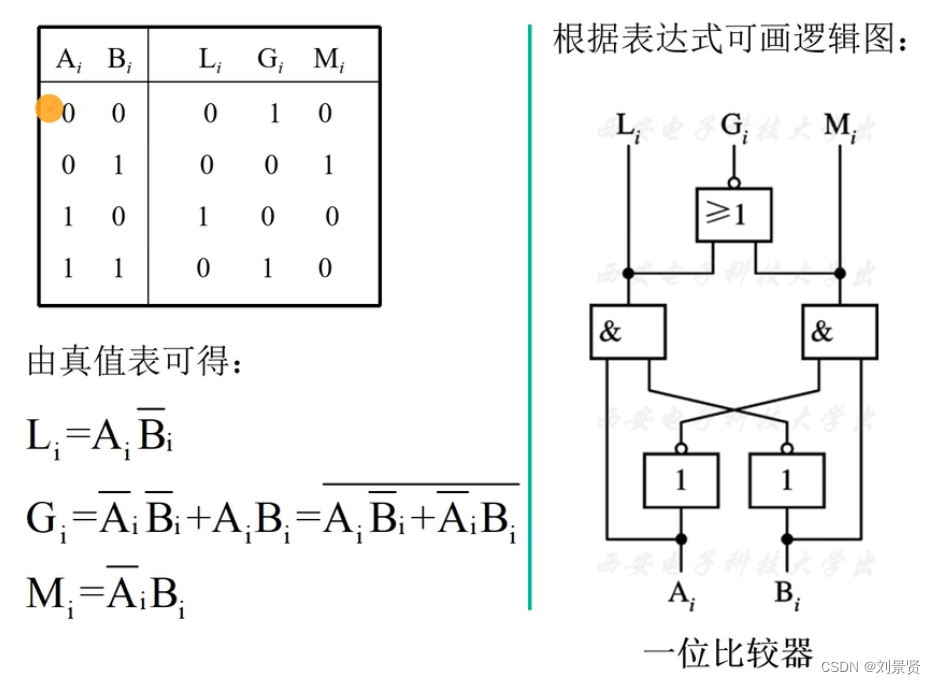

2,比较器

用来比较两个二进制数大小的逻辑电路。

2.1 一位比较器

用来比较两个一位二进制数Ai和Bi的大小。比较结果有三种:Ai>Bi;、Ai=Bi:、Ai<Bi分

别用Li;、Gi;、Mi表示。

2.2 多位比较器

比较两个多位二进制数A=A.....A….A和B=B...B...B的大小,从高位往低位进行,高位相等时才比

较低位。

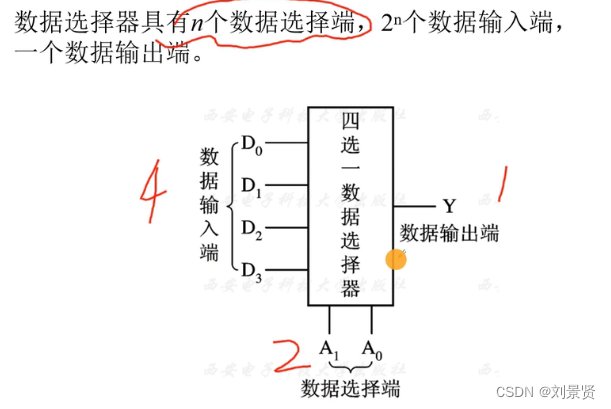

三,数据选择器和数据分配器

1,数据选择器

能从多个数据输入选择出其中进行传输的电路,也称多路选择器或多路开关。

原理:

略

实例:MSI八选一数据选择器74151

略

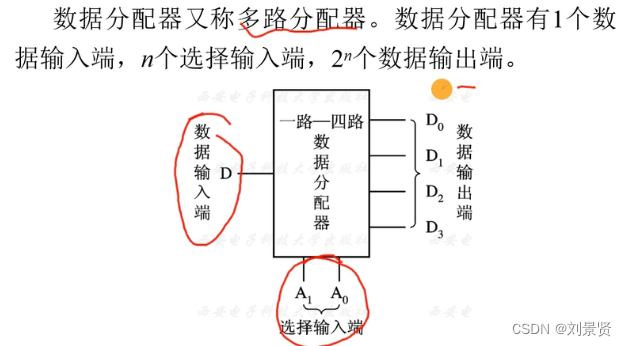

2,数据分配器

将一个输入信号,根据选择信号不同取值,传送至多个输出数据通道中的某一个。

原理:

略

这篇关于《数电》理论笔记-第3章-常用组合逻辑电路及MSI组合电路模块的应用的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!